## Nanocrystals for Nanodot Memories -Ion Beam Synthesis and Electrical Studies

Von der Fakultät für Elektrotechnik und Informatik der Gottfried Wilhelm Leibniz Universität Hannover zur Erlangung des akademischen Grades

> Doktor-Ingenieur (abgekürzt: Dr.-Ing.) genehmigte

> > Dissertation

von Dipl.-Ing. Volkhard Beyer

geboren am 27.10.1972 in Hannover

2012

Referent:Prof. K. R. HofmannKorreferent:Prof. W. Mathis

Tag der Promotion: 11.12.2009

### Abstract

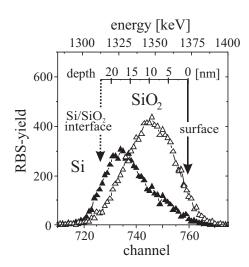

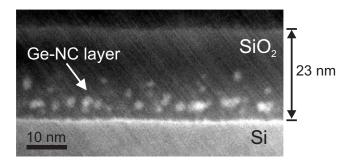

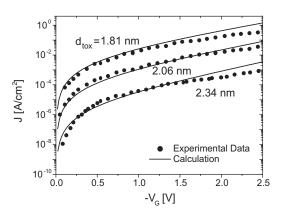

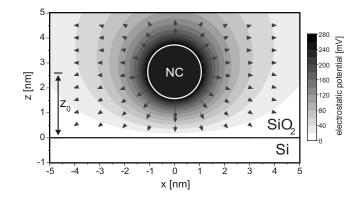

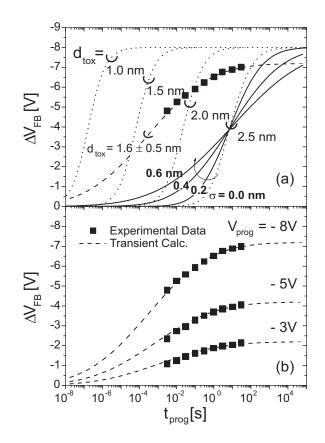

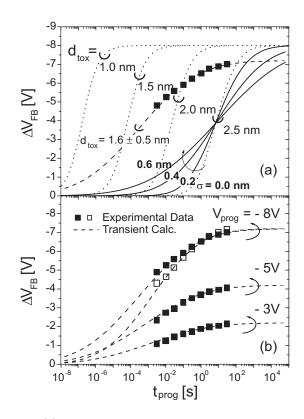

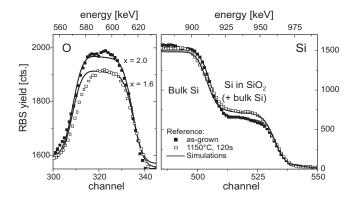

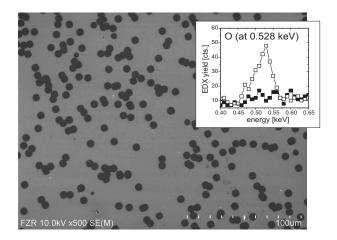

The nanodot memory is an emerging non-volatile memory device concept where isolated nanocrystals are used as charge storage nodes instead of a classical poly-Si floating gate. As a combination of ion implantation and subsequent annealing, the versatile method of ion beam synthesis is used in this thesis to prepare tiny Ge and Si nanocrystals in very thin gate oxides. During the thermal treatment after Ge<sup>+</sup> implantation an enhanced diffusion of Ge in the oxide is obtained which leads to a considerable Ge redistribution as well as to a partial loss of the implanted Ge. Both effects were studied in detail including a model of Ge diffusion in  $SiO_2$ . Due to a self-organizing process, a narrow layer of Ge nanocrystals forms in  $SiO_2$  in vicinity to the Si substrate which is a desired configuration for nanodot memory devices. Metal-oxide-semiconductor capacitor devices were prepared to study the electrical characteristics of the Ge and Si nanocrystal containing gate oxides by means of capacitance-voltage and current-voltage measurements. Additionally, in this thesis a transient electrical model was developed to describe the charging characteristics of such devices as a function of the programming voltage pulse height and duration with respect to the tunneling oxide thickness, nanocrystal size and density. Based on this model, for the first time the statistics of the individual tunneling distances between the nanocrystals and the Si substrate were obtained from simple programming characteristics. For Si and Ge implanted gate oxides leakage current characteristics were calculated with convincing agreements to the current-voltage measurements. It is shown that the leakage current depends mainly on the location of the nanocrystals in the gate oxides and not on implantation related oxide defects. The structural information needed for all these investigations were deduced from energy filtered transmission electron micrographs and Rutherford backscattering spectrometry.

### Kurzfassung

Der Nanodot-Speicher gehört gegenwärtig zu den meist diskutiertesten Konzepten für zukünftige nicht-flüchtige Speicherbauelemente. Dabei werden statt eines poly-Silizium "Floating Gates" isolierte Nanokristalle zur Ladungsspeicherung verwendet. Für diese Dissertationsarbeit wurden in sehr dünnen Gateoxiden winzige Ge und Si Nanokristalle mittels Ionenstrahlsynthese hergestellt, einer Kombination aus Ionenimplantation und anschliessender Ausheilung. Während der thermischen Behandlung nach der Ge<sup>+</sup> Implantation wurde im Oxid eine erhöhte Diffusion des Germaniums beobachtet, welche sowohl eine Umverteilung des Ge auch einen teilweisen Verlust des implantierten Germaniums zur Folge hatte. Beide Effekte wurden im Detail untersucht und ein Modell für die Ge-Diffusion in SiO<sub>2</sub> aufgestellt. Ein selbst-organisierender Prozess sorgt dafür, dass sich Ge Nanokristallen vorwiegend in einem eng begrenzten Bereich im Oxid nahe des Si Substrates - eine gewünschte Anordnung für Nanodot-Speicherbauelemente - formieren. Metall-Oxid-Halbleiter Kapazitätsbauelemente wurden hergestellt, um die elektrischen Eigenschaften der Ge- und Si-haltigen Gateoxide mittels Kapazitäts-Spannungs- und Strom-Spannungs-Messungen untersuchen zu können. Zudem wurde in dieser Arbeit ein elektrisches Modell zur Beschreibung des transienten Beladeverhaltens der Baulemente entwickelt unter Berücksichtigung der Höhe und Dauer der Programmierspannungspulse. Insbesondere die Abhängigkeiten von der Tunneloxiddicke, sowie der Größe und Flächendichte der Nanokristalle konnten damit untersucht werden. Basierend auf diesem Modell konnte zum ersten Mal die statistische Verteilung individueller Tunneldistanzen zwischen den Nanokristallen und dem Si Substrat analysiert werden und zwar aus dem Verhalten einfacher Programmierkennlinien. Darüber hinaus wurden für die Si und Ge implantierten Gateoxide Leckstrom-Charakteristika berechnet, die überzeugende Ubereinstimmungen mit den gemessenen Strom-Spannungskennlinien aufweisen. Dabei konnte gezeigt werden, dass der Leckstrom im Wesentlichen durch den Ort der Nanokristalle im Oxid definiert ist und nicht durch implantationsbedingte Oxiddefekte. Die benötigten strukturellen Informationen wurden mittels energiegefilterter Transmissionselektronenmikroskopie und Rutherford-Rückstreu-Spektrometrie erlangt.

Schlagworte: Ionenimplantation, Nanokristalle, nichtflüchtige Speicherbauelmente

Keywords: ion implantation, nanocrystals, non-volatile memory

# List of publications and thesis conception

In this thesis the major results are summarized in five previously published or submitted manuscripts to refereed journals which are included in this work as separate chapters (chapter 5 - 9). These papers are printed in the format of publication or in a similar two-column paper-like style.

- IN V. Beyer and J. v. Borany Elemental redistribution and Ge loss during ion-beam synthesis of Ge nanocrystals in SiO<sub>2</sub> films. Phys. Rev. B, 014107 (2008) (chapter 5)

- V. Beyer, J. v. Borany, and M. Klimenkov A transient electrical model of charging for Ge nanocrystal containing gate oxides. J. Appl. Phys. 101, 094507 (2007) (chapter 6)

- V. Beyer, J. v. Borany, and M. Klimenkov Determination and evolution of tunneling distances in Ge nanocrystal based memories Appl. Phys. Lett. 89, 193505 (2006) (chapter 7)

- IST V. Beyer, J. v. Borany, M. Klimenkov, and T. Müller Current-voltage characteristics of metal-oxide-semiconductor devices containing Ge or Si nanocrystals in thin gate oxides. accepted for publication in J. Appl. Phys. (2009) (chapter 8)

- IST V. Beyer, J. v. Borany, and K.-H. Heinig Dissociation of Si<sup>+</sup> ion implanted and asgrown thin SiO<sub>2</sub> layers during annealing in ultra-pure neutral ambient by emanation of SiO. J. Appl. Phys. 101, 053516 (2007) (chapter 9)

As a contribution to a book an article has been previously published by Springer-Verlag, Berlin which discusses the different concepts and recent progresses in the subject of ion beam synthesis of Si and Ge nanocrystals in thin gate oxides for memory device applications.

V. Beyer and J. v. Borany Ion-beam Synthesis of Nanocrystals for Multidot Memory Structures in: Materials for Information Technology, edited by E. Zschech, C. Whelan, and T. Mikolajick (Springer Verlag, Berlin), pp. 139-147 (2005)

# List of Acronyms and Abbreviations

| ALD    | atomic layer deposition                                 |  |  |  |  |  |

|--------|---------------------------------------------------------|--|--|--|--|--|

| CHE    | channel hot electron                                    |  |  |  |  |  |

| CMOS   | complementary MOS                                       |  |  |  |  |  |

| C-V    | capacitance-voltage                                     |  |  |  |  |  |

| CVD    | chemical vapor deposition                               |  |  |  |  |  |

| DT     | direct tunneling                                        |  |  |  |  |  |

| DRAM   | dynamic random access memory                            |  |  |  |  |  |

| EELS   | electron energy loss spectroscopy                       |  |  |  |  |  |

| EEPROM | electrically erasable and programmable read only memory |  |  |  |  |  |

| EFTEM  | energy filtered TEM                                     |  |  |  |  |  |

| F-N    | Fowler Nordheim                                         |  |  |  |  |  |

| HAADF  | high-angle annular dark field                           |  |  |  |  |  |

| IBS    | ion beam synthesis                                      |  |  |  |  |  |

| II     | ion implantation                                        |  |  |  |  |  |

| ITRS   | international technology roadmap for semiconductors     |  |  |  |  |  |

| I-V    | current-voltage                                         |  |  |  |  |  |

| KLMC   | kinetic lattice Monte Carlo                             |  |  |  |  |  |

| LE     | low energy                                              |  |  |  |  |  |

| LPCVD  | low-pressure CVD                                        |  |  |  |  |  |

| MONOS  | SONOS with metal gate                                   |  |  |  |  |  |

| MOS    | metal oxide semiconductor                               |  |  |  |  |  |

| MOSFET | MOS field effect transistor                             |  |  |  |  |  |

| NC       | nanocrystal                                                |

|----------|------------------------------------------------------------|

| NRA      | nuclear reaction analysis                                  |

| NROM     | nitrided read only memory                                  |

| NVM      | non-volatile memory                                        |

| PCRAM    | phase change random access memory                          |

| RBS      | Rutherford backscattering spectrometry                     |

| RTA      | rapid thermal annealing                                    |

| SILC     | stress induced leakage current                             |

| SONOS    | silicon oxide nitride oxide silicon                        |

| SRIM     | stopping and range of ions in matter                       |

| STEM     | scanning transmission electron microscopy                  |

| TEM      | transmission electron microscopy                           |

| ToF-SIMS | time of flight secondary ion mass spectrometry             |

| TRIDYN   | SRIM simulation code including dynamic composition changes |

| TXRF     | total reflection X-ray fluorescence                        |

| ULE      | ultra low energy                                           |

| XPS      | X-ray photoelectron spectroscopy                           |

## Contents

| 1 | The  | nanocrystal-based memory device                                                         | 1  |

|---|------|-----------------------------------------------------------------------------------------|----|

|   | 1.1  | Introduction                                                                            | 1  |

|   | 1.2  | Basics of non-volatile memory devices                                                   | 2  |

|   | 1.3  | Nanocrystal memory device characteristics                                               | 4  |

|   | 1.4  | Synthesis of nanocrystals and first demonstrated Mbit memory arrays                     | 7  |

|   | 1.5  | Quantum confinement and Coulomb blockade effect                                         | 8  |

|   | 1.6  | Data retention limitations and concepts of improvement                                  | 9  |

|   | 1.7  | Charge trapping memories, a multibit non-volatile memory cell and new                   |    |

|   |      | materials                                                                               | 11 |

| 2 | lon  | beam synthesis of nanocrystals in SiO $_2$ for nanodot memories                         | 15 |

|   | 2.1  | The principle of ion beam synthesis                                                     | 15 |

|   | 2.2  | Diffusion of Si and Ge in $SiO_2$                                                       | 18 |

|   | 2.3  | Different approaches for ion beam synthesis of NC's in thin $SiO_2$ layers .            | 21 |

|   | 2.4  | Low energy Ge and Si ion implantation, Ge redistribution and loss                       | 25 |

|   | 2.5  | Ion depth profile calculation using TRIDYN                                              | 29 |

|   | 2.6  | High fluence ion implantation in thin gate oxides and related effects                   | 33 |

|   | 2.7  | The impact of humidity on IBS of NC's in thin oxide layers                              | 41 |

|   | 2.8  | Nanocrystals under thermal treatment                                                    | 43 |

|   | 2.9  | Sample preparation with optimized annealing conditions                                  | 44 |

| 3 |      | hods of structural and compositional analysis                                           | 49 |

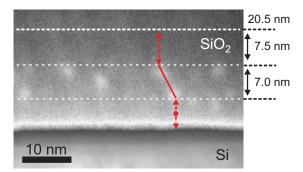

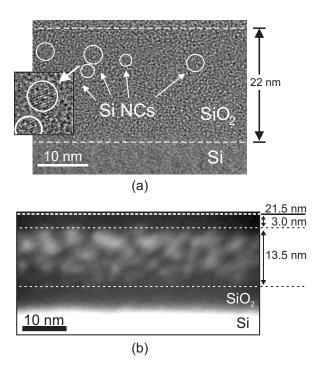

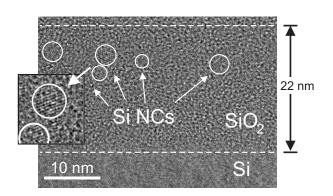

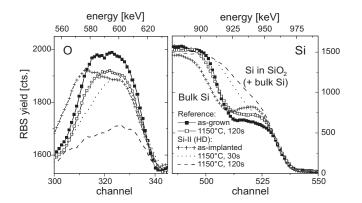

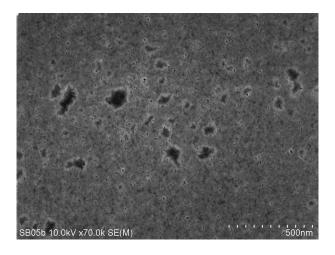

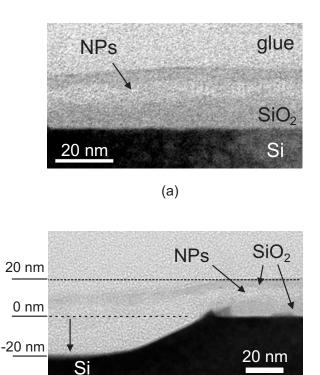

|   | 3.1  | Imaging of Si and Ge NC's embedded in $SiO_2$ (TEM)                                     | 49 |

|   | 3.2  | Rutherford backscattering spectrometry (RBS)                                            | 51 |

|   | 3.3  | Hydrogen profiling using nuclear reaction analysis (NRA)                                | 52 |

| 4 |      | trical modeling and characterization of nanocrystal containing gate ox-                 |    |

|   | ides |                                                                                         | 55 |

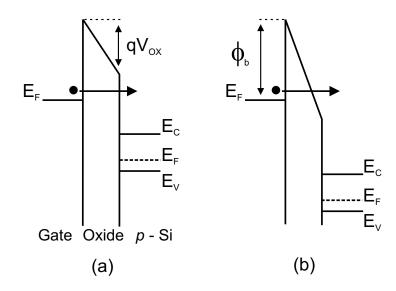

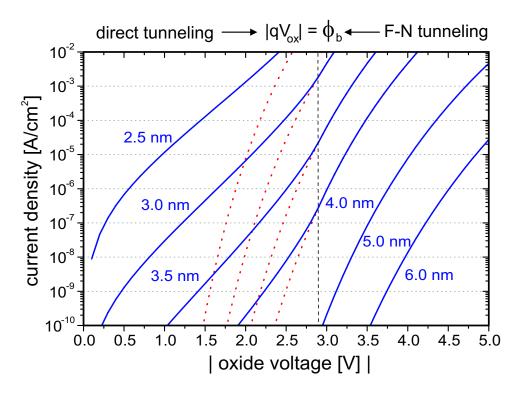

|   | 4.1  | Fowler-Nordheim and direct tunneling                                                    | 57 |

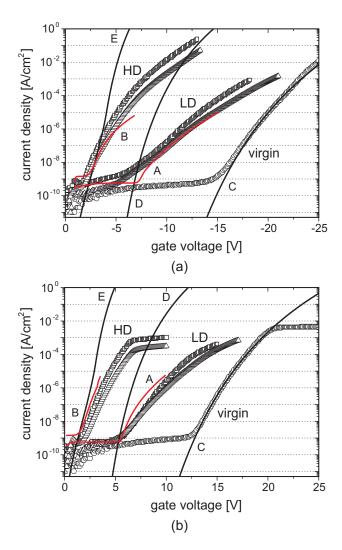

|   | 4.2  | Electrical properties of ion implanted gate oxides                                      | 59 |

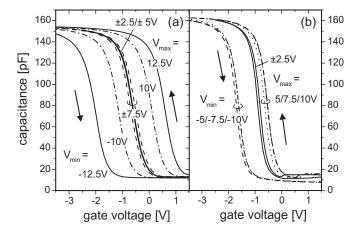

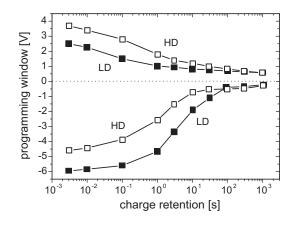

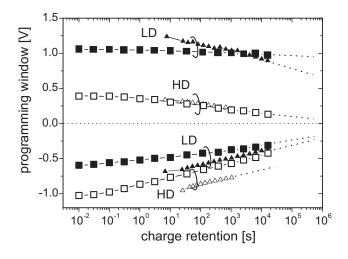

|   | 4.3  | Tracing the NC charging and discharging behavior on MOS capacitors                      | 61 |

| 5 |      | izing a Ge redistribution in the oxide during annealing to prepare nanodot nory devices | 63 |

| 6 | An   | electrical model of charging for nanocrystal containing gate oxides                     | 79 |

| 6 | An o | electrical model of charging for nanocrystal containing gate oxides                     | 1  |

### Contents

| 7   | Determination of the tunneling oxide thicknesses in nanocrystal memories from electrical characteristics    | 89  |

|-----|-------------------------------------------------------------------------------------------------------------|-----|

| 8   | Leakage current-voltage characteristics of nanocrystal containing thin gate oxides                          | 95  |

| 9   | Dissociation of implanted and as-grown thin oxide layers during annealing at low partial pressure of oxygen | 109 |

| 10  | Summary (English/German)                                                                                    | 117 |

| Bil | oliography                                                                                                  | 125 |

| Ac  | knowledgements                                                                                              | 147 |

# 1 The nanocrystal-based memory device

### 1.1 Introduction

Semiconductor Si and Ge nanocrystals (NC's) are very promising materials in silicon based memory and optoelectronic technologies fully compatible to modern complementary metal oxide semiconductor (CMOS) processing. In the mid 1990s Tiwari *et al.* introduced a Si NC based memory device with an auspicious performance [1]. Band-toband recombination of confined excitons in the NC's yields a near-infrared luminescence which is much more efficient than that of bulk silicon (internal photoluminescence quantum efficiency of about 59% [2]). Due to quantum confinement tiny Si NC's (typically of 1 - 4 nm diameter) show also a size tunable electronic bandgap with the option of light emission or absorption at different wavelengths. Thus, the expectable optical applications of Si quantum dots span from Si NC based laser devices [3, 4] to a new generation of photovoltaic solar cells [5]. Very promising, recently, a field-effect electroluminescence in silicon nanocrystals has been demonstrated [6, 7].

In the past decades dramatic improvements have been achieved in the silicon technology and the related device performances. In 1965 Gordon E. Moore predicted that the complexity (the number of transistors in an integrated circuit) increases roughly with a factor of two per year [8], which was refined in 1975 to a period of two years. Since that time this rule - called "Moore's law" - has a self-fulfilling prophecy as the entire microelectronic industry adapted this as a goal for their product and engineering roadmap. The International Technology Roadmap for Semiconductors (ITRS), which documents the current technology standards, uses this law to predict the device performances and technology demands for about the next 15 years [9]. Actually, one of the most difficult challenges for emerging research devices is attributed to the development of an electrically accessible high speed and high density non-volatile memory. It was found that the most limiting factor to increase the microprocessor program executing performance is the slow access to external storage media, e.g. to magnetic hard drives. A nanoscale non-volatile memory device is thought to improve the information throughput significantly, with the potential to "initiate a revolution in computer architecture" [9]. According to the actual roadmap there are two most promising candidates of emerging memory devices [9]. The nanofloating gate device includes all concepts which utilize a charge storage in discrete traps; the nanocrystal (also known as nanodot or multidot) memory depends to this type. The other concept considers a floating gate device with an engineered (graded or "crested") tunnel barrier with the consequence of the introduction of new tunnel oxide

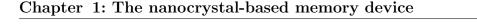

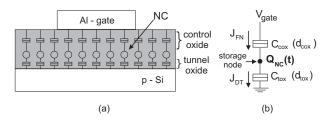

Figure 1.1: (a) Schematic of an EEPROM non-volatile memory transistor cell in crosssectional view. Programming and erasing occurs due to a charge exchange between the floating gate and the Si substrate across the tunneling oxide. A single leakage path through this oxide induces a complete discharge of the floating gate and, thus, complete data loss. (b) Simplified capacitor model of a floating gate memory device.

materials like  $Al_2O_3$  or  $HfO_2$  (see the following sections and Fig. 1.8 for details).

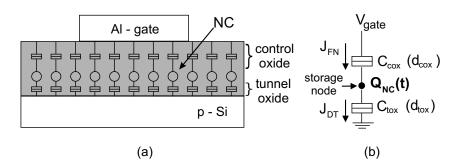

This thesis is aiming at nanocrystal memory devices and their electrical characteristics, whereas the Si (and Ge) nanocrystals are synthesized in 20 nm thin gate oxides by ion implantation and subsequent annealing. Both processes used in ion beam synthesis are widely accepted in the microelectronic industries, they are well-known and cost-effective.

### 1.2 Basics of non-volatile memory devices

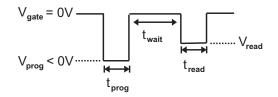

The most popular form of a conventional non-volatile memory is the Electrically Erasable and Programmable Read-Only Memory (EEPROM). As schematically shown in Fig. 1.1, this device consists of an isolated highly doped poly-Si layer, called floating gate, embedded in the gate oxide of a metal-oxide-semiconductor (MOS) field effect transistor (FET) [10]. An alternative is the silicon-oxide-nitride-oxide-silicon (SONOS) memory device where the poly-Si floating gate is exchanged by a charge trapping Si<sub>3</sub>N<sub>4</sub> layer [see Fig. 1.2(b)] [10]. In modern data storage devices like memory cards, USB sticks, or solid state drives, we find floating gate devices integrated in a Flash memory architecture which implies block-wise erase at once. Electrons, which are injected from the Si substrate (the Si channel) into the floating gate by Fowler-Nordheim (F-N) tunneling or channel-hotelectron (CHE) injection, cause a shift of the threshold voltage of the transistor which is analyzed sensing the source-drain current (for details see Ref. [10]). The most relevant parameters to evaluate the performance of a single memory transistor cell are [10]

- the **programming characteristics** which shows the shifting of the threshold voltage as a function of the applied programming voltage and time;

- the **device retention** indicating the ability to retain the stored charge as a function

of the storage time (>10 years are required for real non-volatility);

• the endurance characteristics revealing the memory device reliability as a function of the number of applied write/erase cycles. EEPROM cells hold typically 10<sup>6</sup> cycles without significant changes in the threshold voltages in the programmed or erased states.

An overview of Flash memory cells and their basic principles is given in Refs. [10], [11]. Disregarding the source and drain contacts to reduce the memory transistor to a metaloxide-semiconductor (MOS) capacitor device, the potential of the floating gate ( $V_{fg}$ ) simplifies to

$$V_{fg} = \frac{C_2}{C_1 + C_2} V_{gate} + \frac{Q_{fg}}{C_1 + C_2}$$

(1.1)

with the capacitances of the tunneling and control oxide  $C_1$  and  $C_2$  (in units of F/cm<sup>2</sup>), respectively [see Fig. 1.1(b)].  $V_{gate}$  is the potential of the gate with respect to the Si substrate. The charge density stored at the floating gate  $Q_{fg}$  changes with time t as electrons or hole are transferred through the tunneling or control oxide contributing to the positive or negative current density  $J_i$  in Eq. (1.2).

$$Q_{fg}(t) = \int_0^t \sum_{A_i} J_i[E_i(t)]dt$$

(1.2)

$A_i$  subsume all areas of charge injection (or ejection) toward (or from) the floating gate. The electrical fields  $E_i$  across the tunneling and control oxides are themselves a function of  $V_{cg}$  and  $Q_{fg}$  implicitly [10]. As a consequence, Eq. (1.2) can not be solved directly. One way to handle this problem is to calculate the internal potentials and the amount of charges numerically solving this equation iteratively as a function of the programming time, for instance, with very small time increments. Discussing the data retention of a Flash memory device usually a temperature activated process is considered for the charge loss following the Arrhenius law ( $E_A$  is its activation energy,  $t_R$  the retention time, and  $t_0$  the retention time corresponding to an infinite temperature) [12].

$$t_R = t_0 e^{E_A/kT} \tag{1.3}$$

As mentioned by De Salvo *et al.* [12] the measured EEPROM retention data loss characteristic has an exponential temperature dependence with T and not with 1/T as predicted by Eq. (1.3). This behavior is explained by the temperature dependence of the Fowler-Nordheim tunneling current which is the dominant charge loss mechanism in classical floating gate devices.

The conventional floating gate memory device suffers mainly from its sensitivity to oxide defects. A single defect or trap within the tunneling oxide can open leakage paths to deplete the floating gate leading to a complete data loss and memory device failure. Such defects are, for instance, generated during write/erase cycling, i.e. electron in-/ejection at high electrical fields across the tunneling oxide, which results in the so called "stress induced leakage currents" (SILC) [13]. As the performance of such a classical floating

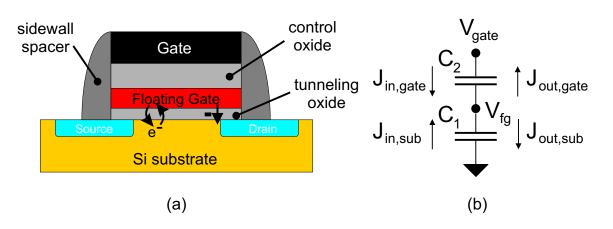

Figure 1.2: Different charge trapping non-volatile memory concepts, the nanocrystalbased (a) and SONOS memory device (b). In both cases the charge is trapped at individual storage nodes, at nanocrystals (a) or natural silicon-nitride traps (b).

gate memory device depends crucially on the quality of the tunneling oxide, an oxide thickness of at least 7 nm is needed to ensure real non-volatility. As a consequence, the conventional Flash EEPROM still suffers from high programming voltages (e.g.  $\geq 15$  V) resulting in high electrical oxide fields during write-/erase operation and, thus, hot-carrier degradation of the tunneling oxide limiting the retention and endurance memory device performance. This contradicts to design rules for further device scaling to achieve higher data densities where the shrinking of the transistor dimensions also includes a decreasing tunneling oxide thickness.

### 1.3 Nanocrystal memory device characteristics

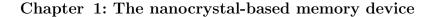

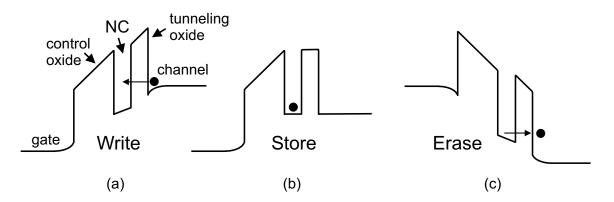

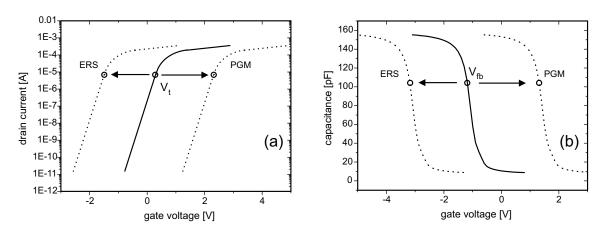

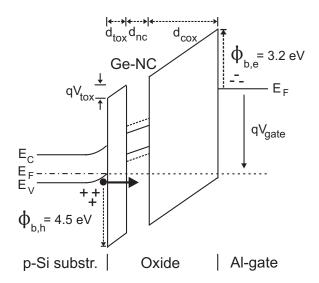

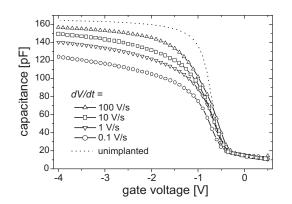

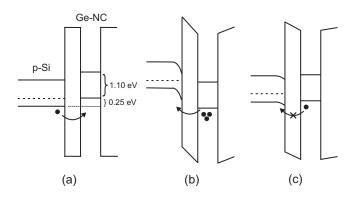

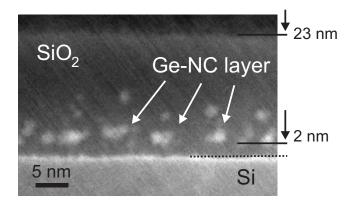

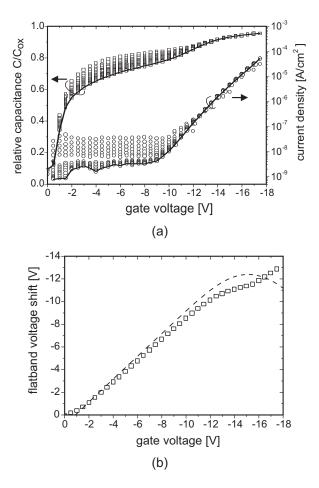

In the mid 1990s Tiwari et al. [1, 14] proposed a nanocrystal based memory device to overcome expectable limitations for the conventional non-volatile memory device concepts (oxide thickness scalability, operation at lower voltages, power consumption, write/erase speed etc.). As the most prominent approach for the nano-floating gate memories - according to the actual International Technology Roadmap for Semiconductors (ITRS) [9] this topic has dominated the research activities of emerging memory devices over the past 10 years (Fig. 1.8). The nanocrystal memory has an outstanding advantage over other memory concepts (e.g. magnetic or ferroelectric memories) as it is easily integratable in conventional silicon technology and CMOS processing. As shown in Fig. 1.2(a) in such a device the floating gate is replaced by a layer of tiny (much smaller than 10 nm in diameter) semiconductor (Si, Ge) nanocrystals embedded in SiO<sub>2</sub> well separated from each other and the  $Si/SiO_2$  interface. In Fig. 1.3 its working principle is illustrated. Charges are transferred from the Si substrate into three-dimensionally confined nanocrystals by a direct tunneling mechanism, which promises fast operation at room temperature at low gate voltages and low power consumption [1]. These charges stored within the gate oxide of the transistor cause a shift of the onset characteristic which can also be traced on MOS

Figure 1.3: Schematic band diagram of write, store and erase operations (a-c) for charge storage in a nanocrystals containing memory device after Ref. [1].

Figure 1.4: Shifting of (a) the subthreshold I-V characteristic of a memory n-FET transistor or (b) the C-V characteristic of a NC containing MOS capacitor device demonstrating schematically the initial, the programmed (PGM), and erased state (ERS) of the device.

capacitor devices (see Fig. 1.4). Due to an isolating spacing between the nanocrystals, a charge dispersion within this layer is suppressed and, thus, also a complete spontaneous charge loss through a single oxide leakage path to the substrate is avoided. This enables a low voltage operation with direct tunneling through a thinner oxide layer ( $d_{ox} < 5 \text{ nm}$ ) where high electrical fields with hot-carrier oxide degradation are not necessary anymore [1]. Thus, the charge storage in nanocrystals instead of in a conventional floating gate offers several attractive advantages:

- fast write and erase processes become possible due to large current densities in the direct tunneling regime,

- avoidance of hot carriers enables **an extremely reduced oxide degradation** in comparison to conventional Flash or nitride trapping devices (SONOS),

- operation at smaller voltages in the direct tunneling regime with lower power consumption than EEPROMs

- with the perspective of acceptable retention time and also non-volatility,

- in combination with a simple fabrication process and therefore low costs.

As this device is usually numerously embedded in NOR or NAND architectures also additional advantages appear, e.g., a decreased floating-gate capacitance coupling or suppression of "erratic bits" and drain-turn phenomena (see Ref. [15] for details).

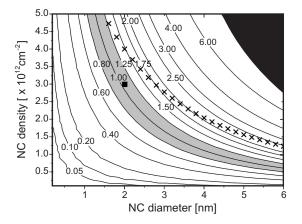

The magnitude of the threshold shift  $\Delta V_t$ , which separates the programmed "1" or erased "0" state of the device from the initially uncharged state, is approximately given by

$$\Delta V_t = \frac{nqN_{nc}}{\varepsilon_{ox}} \left( d_{cox} + \frac{1}{2} \frac{\varepsilon_{ox}}{\varepsilon_{nc}} d_{nc} \right) \quad . \tag{1.4}$$

There, *n* represents the averaged number of charges per nanocrystal and *q* the electron's charge.  $\varepsilon_{ox}$  and  $\varepsilon_{nc}$  are the dielectric constants of the oxide (usually SiO<sub>2</sub>) and the NC's, respectively. A similar equation [Eq.( 4.7)] describes the shift of the flatband voltage  $V_{fb}$  of the *C*-*V* characteristic of a MOS capacitor device (see also Fig. 1.4). Considering a mono-dispersed array ( $N_{nc} = 3 \times 10^{12} \,\mathrm{cm}^{-2}$ ) of Ge nanocrystals embedded in SiO<sub>2</sub> ( $d_{nc} = 2 \,\mathrm{nm}$ ) as shown in Fig. 1.2(a), a considerable threshold voltage shift of about 2 V is achieved assuming one stored charge per nanocrystal and a typical control oxide thickness  $d_{cox}$  of 15 nm ( $\varepsilon_{nc} = 16 \,\varepsilon_0, \,\varepsilon_0$  is the permittivity of free space [16]). A key parameter of the nanocrystal memory programming performance is - with experimental evidence [17] - the areal coverage ratio of the nanocrystals  $R_{nc}$  and not only the areal dot density  $N_{nc}$  as predicted in Eq. (1.4) [18].

$$R_{nc} = A_{nc}/A_{tot} = \frac{\pi}{4} d_{nc}^2 N_{nc} < 1 , \qquad (1.5)$$

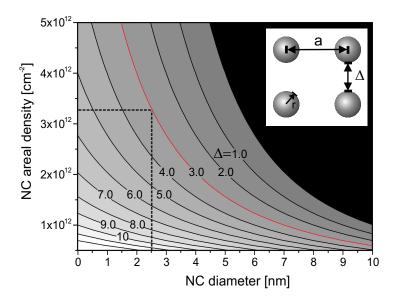

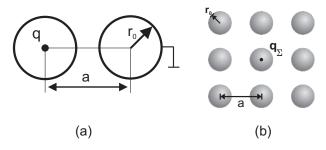

$A_{nc}$  is the projected area of the square NC surfaces and  $A_{tot}$  the total device (gate) area. This ratio defines the effective tunneling oxide areal fraction available for nanocrystal charging and is, thus, besides the tunneling oxide thickness and tunneling barrier heights, a key parameter for the programming and erase time performance. As a consequence, the nanocrystal size and density are crucial parameters with respect to NC formation. The scalability of a nanocrystal-based memory device demands a NC density considerably exceeding  $N_{nc} = 1 \times 10^{12} \text{ cm}^{-2}$  in order to ensure a clear separation between the "1" and "0" memory states [19]. Each cell transistor has to contain a sufficient number of NC's without significant deviations in the programming and erase performance. In any case the distance between the nanocrystal should be larger than the distance to the Si substrate (the tunneling oxide thickness) [20]. In a simple approximation of uniformly distributed, monodispersed nanocrystals in a floating gate layer as shown in the inset of Fig. 1.5, the NC density can be easily deduced by

$$N_{nc} = \frac{1}{a^2} = \frac{1}{(\Delta + d_{nc})^2}$$

(1.6)

Figure 1.5: Minimum tunneling distance  $\Delta$  (in nm) as a function of the NC density and size using Eq. (1.6) according to a homogeneous distribution of NC's as illustrated in the inset. The black shaded area represents connected NC's, equivalent to a continuous floating gate. For example, as indicated by the broken lines a layer of regularly distributed NC's of 2.5 nm size with a minimum distance of 3 nm between each other yields a NC density of 3 -  $3.5 \times 10^{12}$  cm<sup>-2</sup>.

for a known NC size  $d_{nc}$  and a tunneling distance  $\Delta$  between two nearest neighbored ones (*a* is the "lattice constant" of the NC array). As shown in Fig. 1.5 with these assumptions a density of about  $3 \times 10^{12}$  cm<sup>-2</sup> is only achievable with a NC size of  $d_{nc} \leq 3$  nm. Thinking about a suitable NC preparation technique, it is an excellence of the ion beam synthesis method to fulfill these demands easily without particular time and money spending efforts.

### 1.4 Synthesis of nanocrystals and first demonstrated Mbit memory arrays

Numerous efforts have been carried out to prepare Si nanocrystals in host matrices, preferably in a high density. Besides ion beam synthesis [21] - which is the topic of this thesis and discussed in detail in chapter 2 - manifold deposition techniques were reported. An overview is given by De Blauwe [22]. An aerosol technique was investigated [23], chemical vapor deposition (CVD) [24, 25, 26], and also amorphous-Si or Si-rich oxide layer physical vapor deposition (PVD) [27, 28], whereas the NC formation occurs during a recrystallizing annealing treatment. From these methods the CVD provides the best control over size and density of the nanocrystals (details of this method are reported by Rao *et al.* [25]): SiH<sub>4</sub> molecules adsorb on the previously thermally-grown tunneling oxide layer surface and dissociate there building Si adatoms. These atoms work either as

centers to form new nuclei or are consumed by existing and growing NC's by surface diffusion [25]. Usually, the reported nanocrystal density is in the range between  $1 \times 10^{11} \,\mathrm{cm}^{-2}$ and  $1 \times 10^{12} \,\mathrm{cm}^{-2}$  with a mean NC diameter of about 5 nm. The highest dot density ever reached by (low pressure) CVD in the literature is  $N_{nc} = 2 \times 10^{12} \,\mathrm{cm}^{-2}$  with a mean dot size of about 3 nm using highly hydroxylated SiO<sub>2</sub> [24]. Also the preparation of Si NC's on alumina was reported, which is important for a future application of NVM devices using high-k materials [29]. Similar and also alternative methods are reported for the formation of Ge NC's in  $SiO_2$ , e.g., the Ge or  $Ge/SiO_2$  co-sputtering [30], an oxidation of  $Si_{1-x}Ge_x$  layers [31], a reduction of CVD  $Si_{0.75}Si_{0.25}O_2$  layers by H<sub>2</sub> [32], molecular beam epitaxy [33], the sol-gel method [34], and also ion implantation [35, 36, 37]. Additionally, a Ge/Si hetero-nanocrystal memory device was discussed [38]. Metal NC's are usually prepared by e-beam evaporation and subsequent annealing (Au, W, Ag, Pt) [39], Au sputtering [40] or via decomposition of sputtered  $Au_{0.25}Si_{0.75}$  or  $W_5Si_3$  silicide layers [41, 42]. A double  $CoSi_2$  layer was produced by subsequent a-Si/Co/a-Si electron beam evaporation and plasma enhanced CVD [43]. Recently, a hexagonal-ordered array of Co NC's was prepared in a very small size distribution using diblock copolymer micelle templates with embedded Co [44].

Freescale (formerly known as Motorola) launched in 2003 first functional 4-Mbit Si nanocrystal-based non-volatile memory cell arrays and later on also 24-Mbit cell arrays [45]. The memory devices were easily integrated in a standard CMOS flow at low costs (a conventional 90 nm technology process) working at a maximum chip voltage of 6 V with sub-10  $\mu$ s programming and sub-100 ms erase times [46]. The total memory size was reduced approximately by a factor of two in comparison to a conventional floating gate nonvolatile memory device [46]. The Si nanocrystals were prepared by CVD in an areal density ranging between  $5 \times 10^{11}$  cm<sup>-2</sup> and  $1.1 \times 10^{12}$  cm<sup>-2</sup>. It should be mentioned that Freescale uses the nanocrystal memory device mainly in automotive applications, which has the most critical and challenging data safety demands [47]. Nitride memory devices, as discussed in chapter 1.7, suffer from the required writing operations using channel-hot electrons with the consequence of an early tunneling oxide wear out. In contrary, nanocrystal memories utilize direct or Fowler Nordheim tunneling processes with a weaker oxide destruction potential.

### 1.5 Quantum confinement and Coulomb blockade effect

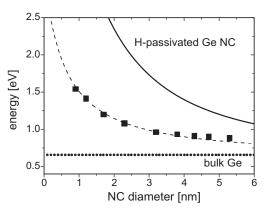

Dealing with particles on nanometer scales quantum size effects have to be taken into account. Contrary to metal NC's, where the valence and conduction bands overlap, semiconductor NC's exhibit a strongly size-dependent energy gap. If the semiconductor nano-particle diameter is below the order of the Bohr exciton (radius of this material), quantum confinement effects become relevant, which leads to an increasing band gap with decreasing particle size [48, 49, 50].

$$E = E_g + \frac{\hbar^2 \pi^2}{2r^2} \left[ \frac{1}{m_e} + \frac{1}{m_h} \right] - \frac{1.8e^2}{\varepsilon r} + \frac{e^2}{r} \sum_{n=1}^{\infty} a_n \left( \frac{S}{r} \right)^{2n}$$

(1.7)

The lowest excited 1s state E (with respect to the bulk bandgap  $E_g$ ) depends on the electron-hole quantum localization (first term), the Coulomb attraction (second term) and polarization (third term). r is the radius of the nano-particle,  $m_e$  and  $m_h$  the electron and hole masses, respectively, and h Planck's constant.  $a_n$  depends on the dielectric properties of the particle and the host and S is a position variable inside the NC sphere which has the dielectric coefficient  $\varepsilon$ . Due to quantum confinement the continuum of electronic transitions within the bands splits into separate energy levels. From the Bohr exciton radius in Si and Ge of 4.3 and 24.3 nm [51], respectively, a more pronounced quantum confinement effect can be expected in case of Ge than of Si NC's of 2 - 3 nm size. The analysis of photoluminescence spectra of, e.g., Si NC's [52, 53, 54] gives a hint of the real NC band-gap energy and NC size evolution during annealing due to band-to-band radiative recombination of confined electron-hole pairs [55, 56]. However, to obtain the NC size directly from the luminescence energy is very difficult, because the band-gap energy is also dependent on the kind of NC surface passivation [57, 58]. Considering hydrogen or oxygen bonds at the NC rim, which is likely in case of Ge or Si NC's being embedded in  $SiO_2$ , the band-gap widening due to quantum confinement is strongly quenched [57].

The basis of single-electron device concepts in quantum-dot structures, which are embedded in tunnel-junction systems, is the Coulomb blockade effect [59, 60]. Thinking about a room temperature application such phenomena only matter if the classical electrostatic charging energy  $E_c$

$$E_c = \frac{e^2}{2C} \gg kT \tag{1.8}$$

is much higher than the thermal energy (k is the Boltzmann constant and T the temperature).  $C = 2\pi\varepsilon r$  is the self-capacitance of a nanocrystal with radius r which is embedded in a matrix with dielectric constant  $\varepsilon$ . The typical staircase-like current-voltage characteristic derives from a quantization effect in a charging experiment of a single nanodot; an external bias voltage  $V_b$  has to be higher than a discrete threshold value of  $V_b = e/C$  to charge the dot with another electron [61]. In single Si nanocrystals these coulomb blockade effects were studied by scanning tunneling spectroscopy [62]. Singleelectron transistors suitable for low power operation have been demonstrated working at room temperature [63, 64] and also single-electron memory applications were discussed [65, 66, 67, 68]. In multi-nanocrystal memory devices the coulomb blockade effect is utilized to improve the retention time with self-aligned doubly-stacked dots [69] (see also chapter 1.6). However, single electron charging and discharging phenomena were detected even in ultrascaled Si NC memories [70].

# **1.6** Data retention limitations and concepts of improvement

Nanocrystal memory devices with a tunneling oxide thickness of  $d_{tox} \ge 5$  nm, where the programming and erase operations are carried out by Fowler Nordheim tunneling, show

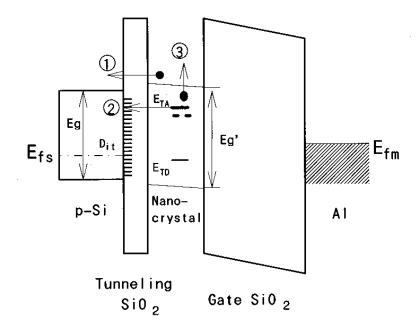

Figure 1.6: A schematic band diagram (taken from Ref. [71]) to illustrate different charge loss mechanisms of a Si NC containing memory structure (O: direct tunneling of electrons from the NC's conduction band to the substrate, O: direct tunneling of electrons from NC traps to unoccupied states at the Si substrate/SiO<sub>2</sub> interface, O: thermally detrapping of electrons to the NC conduction band).

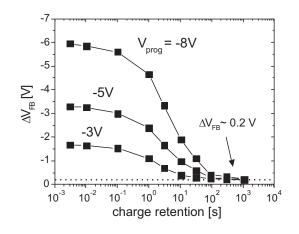

real nonvolatile behavior (charge storage up to 10 years) even at a data retention test performed at a high temperature  $(T = 250^{\circ}C)$  [15]. The performance of devices, which operate in the direct tunneling regime ( $d_{tox} \leq 3.5$  nm), is rather DRAM-like or quasi-(short term)-nonvolatile than real (long term) non-volatile as the data retain only for minutes, hours or days (see Fig. 1.8, for instance). Considering Si NC's as data storage nodes, the electrons are supposed to be stored in the conduction band of the NC. Due to the three-dimensional quantum confinement in the embedded NC's this level is energetically higher than the Si substrate conduction band level. Especially in case of more than one electron stored in the NC's, these electrons can easily tunnel back to the substrate, which is discussed to be the main reason of a short data retention (see process ① in Fig. 1.6) [71]. Considering this "intrinsic" discharging process of a floating-gate like array of nanocrystals a minimum oxide thickness of 4.2 nm is required (for uncycled memories) to guarantee data storage of about 10 years [20]. But, as a trade-off, such a tunneling oxide thickness necessitates longer write times and/or higher programming and erase voltages than those working mainly in the direct tunneling mode. Using Ge instead of Si NC's a long retention time was reported [21], which might be related to the smaller or shifted band gap position of Ge NC's with respect to that of the silicon substrate (see also chapter 6).

Shi et al. argued that a long-term data storage at Si NC's is related to charge capture

#### 1.7 Charge trapping memories, a multibit non-volatile memory cell and new materials

at traps located at the Si NC/SiO<sub>2</sub> interface [71, 72] (see Fig. 1.6). Due to their energy position the trapped charges see a higher barrier for back-tunneling, which is supposed to improve the data retention [20]. As thermal activated processes were found not to be dominant [72, 73], a mechanism of charge loss via detrapping and direct back-tunneling (processes  $\Im + \bigcirc$  in Fig. 1.6) seems not to be likely. A long-term charge storage was attributed to a charge loss involving traps located at the Si substrate/tunneling oxide interface (with density  $D_{it}$ ) as indicated by process  $\oslash$  in Fig. 1.6 [71, 72]. Thus, a low density of interface states there would result in a lower tunneling rate from the NC's to the Si substrate and thus in a longer data retention [72]. But, the quality of this interface is very sensitive to process deviations and stress from device cycling during operation.

Thus, different concepts are discussed to overcome the constrained performance of the "intrinsic" data retention. Likharev [74] introduced the idea to engineer the shape the of the tunneling oxide barrier with a stack of layered barriers using high-k materials like Al<sub>2</sub>O<sub>3</sub> or HfO<sub>2</sub>. Also self-aligned doubly stack Si dots show an improved charge retention, where a smaller Si dot is located directly below a bigger one [69]: A stronger quantum confinement and Coulomb blockade of the smaller (charged) NC causes an additional energy barrier for charges stored in the upper dot. A similar effect was recently shown for a double layer of CoSi<sub>2</sub> NC's [43]. Utilizing the energy difference between the valence band level of the Ge NC's and the Si substrate or NC's, an improved data storage can be expected using Ge NC's instead of Si NC's [21, 75] or Ge/Si hetero-nanocrystals, respectively [38].

Work function engineering is discussed mainly with respect to a replacement of the semiconductor NC's by metal NC's [39]. Metal NC's reveal a variety of barrier heights to the surrounding gate oxide and a well known Fermi energy level due to negligible quantum confinement. In contrary to semiconductor NC's [72], traps at the metal/oxide are supposed to be of subordinate importance, whether due to the high density of states or due to chemical stability of noble metals [76]. For devices containing Au, Ag or Pt NC's operating in the F-N tunneling regime ( $d_{tox} = 5 \text{ nm}$ ) a data retention of up to 10<sup>6</sup> s and also multibit-per-cell storage capability was demonstrated (see chapter 1.7) [77, 78].

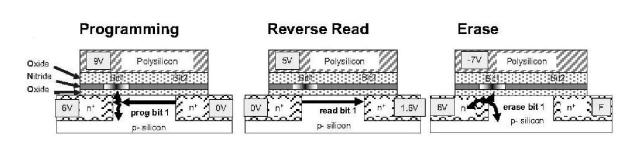

# 1.7 Charge trapping memories, a multibit non-volatile memory cell and new materials

In competition with the classical poly-Si or nanocrystal based floating gate-type nonvolatile memory is the very old charge trapping SONOS (silicon-oxide-nitride-oxidesilicon) or MONOS concept (using a metal gate electrode instead of silicon) [79, 80, 81]. An embedded silicon nitride (Si<sub>3</sub>N<sub>4</sub>) layer [see Fig. 1.2(b)] provides a considerable density of natural discrete traps, which allow a storage of both charge polarities in almost the same amount. The Si<sub>3</sub>N<sub>4</sub> layer, which replaces the poly-Si floating gate in the classical Flash cell, is usually prepared by low-pressure chemical vapor deposition (LPCVD) [82]. The success of such devices was very limited suffering from a so called "erase saturation effect", where during Fowler-Nordheim erase the traps are refilled by electrons injected

#### Chapter 1: The nanocrystal-based memory device

Figure 1.7: Concept of multibit charge trapping taken from Ref. [92].

from the gate [83]. Nevertheless, charge trapping memory cells have attracted special attention since in the late 1990s a 2-bit or multilevel charge storage was demonstrated utilizing channel hot electron and tunneling enhanced hot hole injection for programming and erase, respectively. In a so called nitrided-read-only-memory (NROM) cell [84, 85, 86] as shown in Fig. 1.7 the two bits are spatially separated and localized in the nitride layer of one transistor device, one close to the source and the other close to the drain contact. Such multibit devices are well established as, e.g., "Twin  $\operatorname{Flash}^{TM}$ " (Qimonda) [87] or "MirrorBit<sup>®</sup>" (Spansion) [88] devices in the non-volatile memory microelectronic industry. Multilevel storage capability, which is supposed to be a key aspect in future memory devices, was also demonstrated for Si and metal NC containing memory devices [89, 78]. Thus, Si NC based memory devices are suitable for both NOR and NAND device architectures, where the programming is achieved by channel hot electron injection as in SONOS structures or by electron Fowler-Nordheim tunneling, respectively [15, 90]. There, the multibit capability can be reached by a different charge localization (SONOS trappinglike) or in a conventional floating gate operation due to a difference in the amount of stored charges (different value of threshold voltage shift). Combining the good cycling endurance and fast programming/erase ability of a nanocrystal based memory with a better data retention of SONOS devices, a hybrid Si nanocrystal/SONOS type memory transistor cell offers the opportunity of longer refresh times for, e.g., DRAM applications [91].

New gate insulator material systems including high-k materials (e.g.,  $Al_2O_3$ ) were introduced to solve the problem of erase saturation reducing the voltage drop over the topoxide layer. Simulations for NC based memory devices show that the programming and erase performance of such cells is significantly improved replacing the SiO<sub>2</sub> top oxide by a high-k dielectric [93]. Tantalum nitride or Pt are discussed as gate electrode materials to increase the barrier for electrons from the gate [94]. HfO<sub>2</sub>/HfAlO/HfO<sub>2</sub> nanolaminates [95] prepared by atomic layer deposition (ALD) technique or TiN nanocrystals embedded in  $Al_2O_3$  [96] can be also used as trapping layers in such devices replacing the sandwiched silicon nitride layer. Advanced device structures like FinFET [97] or 3D stacked [98] charge trapping memory cells have been recently developed with very promising results. Considering alternative future memory concepts the phase change memory seems to be the most competitive [92] as recently, a fully functional 512-Mbit phase-change random access memory (PCRAM) chip has been demonstrated [99]. An overview of recent and future memory concepts is given in the international technology roadmap for semicon-

### 1.7 Charge trapping memories, a multibit non-volatile memory cell and new materials

ductors 2005 as shown in Fig. 1.8. The nanocrystal based memory devices are still an option for future non-volatile memories being fully compatible with other future charge trapping device concepts, i.e., the multibit storage, FinFET, 3D-structure etc. [92, 89]. After De Salvo *et al.* [15], the Si NC and the SONOS discrete-trap memory concept remain still promising candidates in future memory applications according to their costs per bit, their performance and reliability.

|                          |                     | Nano-floating<br>Gate Memory [A]                         | Engineered<br>Tunnel Barrier<br>Memory | Ferroelectric FET<br>Memory                                       | Insulator Resistance<br>Change Memory                                                | Polymer<br>Memory        | Molecular<br>Memories    |

|--------------------------|---------------------|----------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------|--------------------------|

| Storage Mechanism        |                     | Charge on floating<br>gate                               | Charge on<br>floating gate             | Remanent<br>polarization on a<br>ferroelectric gate<br>dielectric | Multiple<br>mechanisms                                                               | Not known                | Not known                |

| Cell Elements            |                     | 1T                                                       | 1T                                     | 1T                                                                | 1T1R or 1R                                                                           | 1T1R or 1R               | 1T1R or 1R               |

| Device Types             |                     | 1 Nanocrystal<br>2 Direct tunneling                      | Graded<br>insulator                    | FET with FE gate<br>insulator                                     | 1 M-I-M<br>2 Solid Electrolyte<br>3 FE tunneling<br>4 FE Schottky diode<br>5 FE-I-FE | M-I-M (nc)-I-M           | Bi-stable switch         |

| E. d                     | Minimum<br>required | <65 nm                                                   | <65 nm                                 | <65 nm                                                            | <65 nm                                                                               | <65 nm                   | <65 nm                   |

| Feature size F           | Best projected      | 25 nm                                                    | 10 nm [H]                              | 22 nm [K]                                                         | 5–10 nm [O]                                                                          | 5–10 nm                  | 5-10 nm [AA]             |

|                          | Demonstrated        | 90 nm [A]                                                | 180 nm [I]                             | ~10 µm [L]                                                        | 100 nm [P]                                                                           | 200 µm [W]               | 30 nm [AB]               |

|                          | Minimum<br>required | $10F^2$                                                  | $10 \ F^2$                             | $8F^2$                                                            | 10 F <sup>2</sup>                                                                    | 10 F <sup>2</sup>        | $10 \ \mathrm{F}^2$      |

| Cell Area                | Best projected      | 8-10F <sup>2</sup>                                       | 8F <sup>2</sup> [H]                    | 8F <sup>2</sup>                                                   | 8/5F <sup>2</sup> [Q]                                                                | 8/5F <sup>2</sup>        | 5F <sup>2</sup>          |

|                          | Demonstrated        | 16F <sup>2</sup> [A]                                     | Data not<br>available                  | Data not available                                                | Data not available                                                                   | Data not<br>available    | Data not available       |

| n 1 <i>m</i>             | Minimum<br>required | <15 ns                                                   | <15 ns                                 | <15 ns                                                            | <15 ns                                                                               | <15 ns                   | <15 ns                   |

| Read Time                | Best projected      | 2.5 ns                                                   | 2.5 ns                                 | 2.5 ns                                                            | <10 ns                                                                               | <10 ns                   | <10 ns [AA]              |

|                          | Demonstrated        | 20 ns [B]                                                | 20 ns [B]                              | 20 ns [B]                                                         | 2 ms [R]                                                                             | ~10 ns [X]               | Data not available       |

|                          | Minimum<br>required | 1 μs/10 ms                                               | 1 μs/10 ms                             | Application<br>dependent                                          | Application<br>dependent                                                             | Application<br>dependent | Application<br>dependent |

| W/E time                 | Best projected      | 1 µs/10 ms                                               | 1 ns at 9V[H]                          | 2.5 ns [B]                                                        | <20 ns [P]                                                                           | Not known                | <40 ns [AA]              |

|                          | Demonstrated        | W: 1–10 µs [C]<br>E: 10–100 ms [D]                       | E: ~10 ms [I]                          | 500 ns [L]                                                        | 25 ns [P]                                                                            | <10 ns [X]               | ~sec [AC]                |

| Retention                | Minimum<br>required | >10 y                                                    | >10 y                                  | >10 y                                                             | >10 y                                                                                | >10 y                    | >10 y                    |

| Time                     | Best projected      | >10 y                                                    | >10 y                                  | >1y                                                               | >10 y                                                                                | Not known                | Not known                |

|                          | Demonstrated        | >200 hours [E]                                           | >10 y [I]                              | 30 days [M]                                                       | 1 y [S]                                                                              | 6 month [Y]              | 2 months [AC]            |

| w t                      | Minimum<br>required | >1E5                                                     | >1E5                                   | >1E5                                                              | >1E5                                                                                 | >1E5                     | >1E5                     |

| Write Cycles             | Best projected      | >1E5                                                     | >3E16                                  | >3E16                                                             | >3E16                                                                                | >3E16                    | >3E16                    |

|                          | Demonstrated        | >1E4 [A]                                                 | 5E4 [J]                                | 1E12 [O]                                                          | 1E5 [T]                                                                              | >1E6 [X]                 | >2E3 [AD]                |

| Write<br>Operating       | Minimum<br>required | Application<br>dependent                                 | Application<br>dependent               | Application dependent                                             | Application dependent                                                                | Application<br>dependent | Application<br>dependent |

| Voltage (V)              | Best projected      | >3 V [F]                                                 | >3 V [F]                               | <0.9 V [K]                                                        | <0.5 V [U]                                                                           | Not known                | 2 V [AE]                 |

|                          | Demonstrated        | ±6 [A]                                                   | 6.5 [I]                                | ±6 [O]                                                            | 0.24 V [P]                                                                           | ~±2 [X]                  | ~±1.5 V [AB]             |

| Read                     | Min. required       | 2.5                                                      | 2.5                                    | 2.5                                                               | 2.5                                                                                  | 2.5                      | 2.5                      |

| Operating<br>Voltage (V) | Best projected      | 0.7                                                      | 0.7                                    | 0.7                                                               | <0.2 V [U]                                                                           | 0.7                      | 0.3 [AA]                 |

| · Singe (F)              | Demonstrated        | 2.5 [B]                                                  | 2.5 [B]                                | 2.5 [B]                                                           | ~0.2 V[P]                                                                            | ~1 [X]                   | 0.5 [AB]                 |

| Write Energy             | Min. required       | Application<br>dependent                                 | Application<br>dependent               | Application dependent                                             | Application dependent                                                                | Application<br>dependent | Application<br>dependent |

| (J/bit)                  | Best projected      | 5E-16 [G]                                                | 5E-16 [G]                              | 2E-15 [N]                                                         | 1E-15 [V]                                                                            | Not known                | 2E-14 [AA]               |

|                          | Demonstrated        | 2E-15 [G]                                                | Data not<br>available                  | Data not available                                                | 5E-14 [P]                                                                            | 1E-13 [Z]                | Data not available       |

| Comments                 |                     | A natural<br>evolution of the<br>floating gate<br>memory |                                        | Potential for non-<br>destructive readout                         | Low read voltage presents a problem                                                  |                          |                          |

| Research activit         | v [AE]              | 123                                                      | 12                                     | 74                                                                | 39                                                                                   | 25                       | 68                       |

Figure 1.8: Demostrated and projected parameters of emerging research memory devices as published in the ITRS 2005 [9].

### 2 Ion beam synthesis of nanocrystals in SiO<sub>2</sub> for nanodot memories

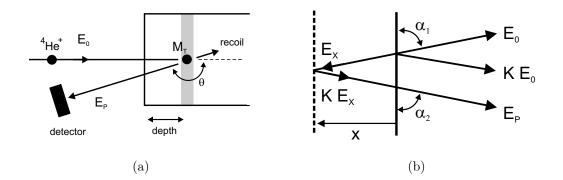

Ion implantation is a very important and widely used technique for the doping of silicon in the semiconductor industry (impurity concentration N < solid solubility in silicon c). Impurity depth profiles are easily adjustable by ion energy (depth distribution) and fluence (doping level) - scalable and reproducible, whereas isotopically pure ion beams assure a low contamination of the wafer during processing. Its wide familiarity in the silicon technology makes it advantageous for future memory applications. As a versatile and very powerful technique, for research studies the ion implantation is used to synthesize nanoclusters/-crystals or nanocomposite materials (N > c) embedded in various host materials affecting the optical, magnetical, electrical or other properties of near-surface regions of the treated materials [100, 101, 102, 103].

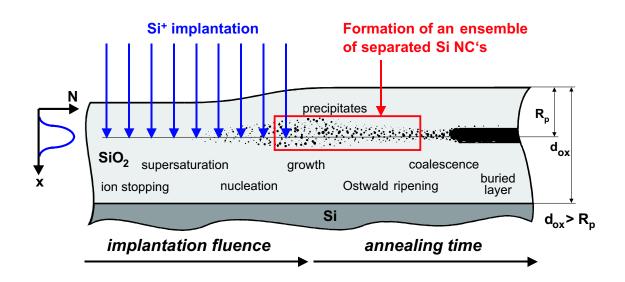

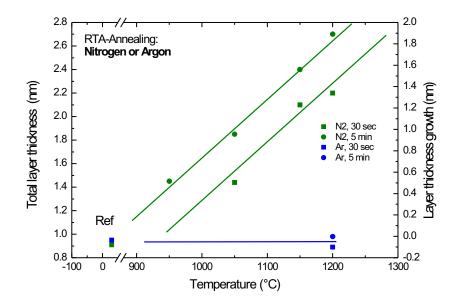

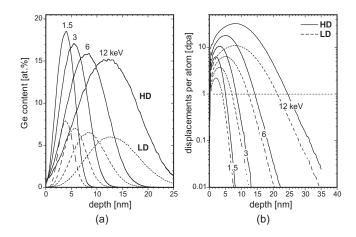

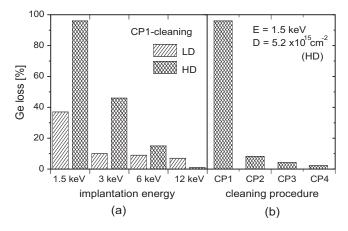

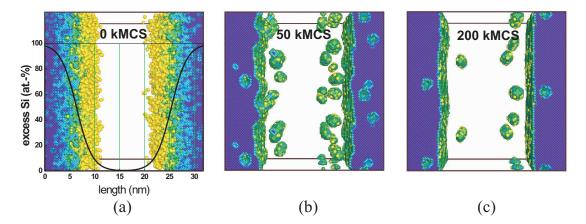

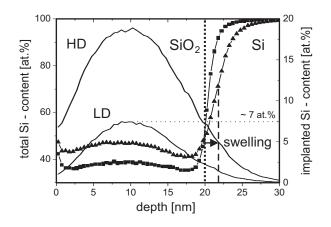

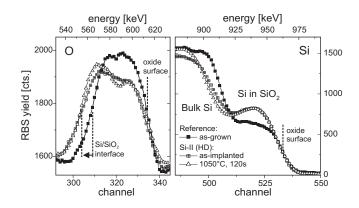

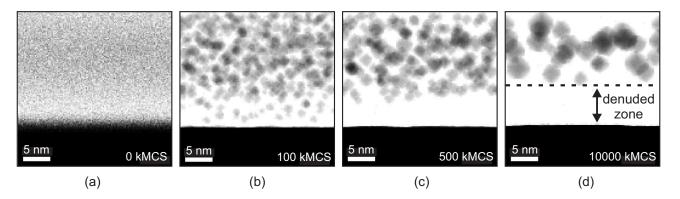

This chapter addresses the principle of ion beam synthesis (IBS), especially the synthesis of semiconductor nanocrystals in thin gate oxides for the application in (non-) volatile memory devices. As a combination of ion implantation and subsequent annealing, IBS utilizes processes of self-organization in supersaturated and perturbed matrices via phase separation. Mainly tiny NC's ( $d_{nc}$  of 2 - 3 nm) are formed in a very high density ( $N_{nc} \ge 1 \times 10^{12} \text{ cm}^{-2}$ ) in SiO<sub>2</sub> during annealing fulfilling one of the main requirements for future nanodot memory devices. Thin gate oxides ( $d_{ox} \le 20 \text{ nm}$ ) are required to realize devices with comparable or even lower programming voltages and times than of conventional floating-gate memories. In this chapter different IBS approaches are discussed with emphasis on the synthesis of NC's by low energy ion implantation - the main subject of this thesis. In a special case redistribution effects, i.e. combined processes of self-ordering and Ge diffusion, are utilized to obtain  $\delta$ -like layers of Ge NC's in SiO<sub>2</sub> in vicinity to the Si substrate.

### 2.1 The principle of ion beam synthesis

From the technological point of view the ion beam synthesis is a combination of ion implantation at high fluences and subsequent annealing which is herein exemplified on Ge and Si ion implantation in thin gate oxides. The ion implantation of Ge or Si in SiO<sub>2</sub> leads usually to a supersaturation by impurity atoms inside the gate oxide due to a rather low solubility of these atoms in the oxide. Generally speaking, the depth distribution of the implanted impurities is nearly of Gaussian-type and is adjusted by the mass and energy (in keV) of the implanted ions. Their average penetration depth (projected range  $R_p$ ) is determined by mass and energy, the mean NC size and density - at least to a

Chapter 2: Ion beam synthesis of nanocrystals in SiO<sub>2</sub> for nanodot memories

Figure 2.1: Scheme of ion beam synthesis of Si nanocrystals, for instance, deduced after Refs. [104, 105]. Even during ion implantation NC's nucleate inside the supersaturated region and grow in the following by subsequent annealing. Buried layers or wires can be formed for very high ion fluences by a process of coalescence.

certain extent [105] - by the implantation fluence (in ions/cm<sup>2</sup>). A subsequent thermal treatment is required to form the NC's by phase separation out of a supersaturated film and for damage annealing of the implanted oxide. The NC formation is described in terms of nucleation and growth of precipitates (Fig. 2.1). The NC mean size, density and spatial distribution changes during Ostwald ripening [106], whereas larger precipitates grow at the expense of smaller ones assuming an interaction between them by diffusion during the growth competition. The driving force of this process is the reduction of the total surface energy of the NC's and thus of the total free energy of the system by a mass transfer from dissolving small NC's toward larger ones. As a consequence, NC's of different size (radius R) have in thermal equilibrium different solute concentration of monomers in their surrounding media  $c^{GT}(R)$ , which is described by the Gibbs-Thomson relation [107, 104, 108].

$$c^{GT}(R) = c_{\infty} \exp\left(\frac{R_c}{R}\right) \approx c_{\infty} \left(1 + \frac{R_c}{R}\right) \quad \text{with} \quad R_c = \frac{2\sigma V_m}{kT}$$

(2.1)

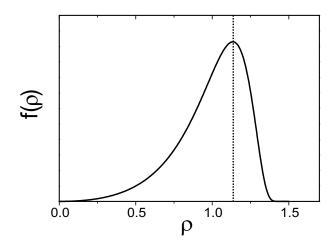

There,  $c_{\infty}$  is the solubility at a flat precipitate/matrix interface  $(R \to \infty)$  and  $R_c$  is the capillary length ( $\sigma$ ,  $V_m$ , k, and T are the surface tension, the atomic volume, the Boltzmann constant and temperature, respectively). Thus, during annealing the final NC size distribution is governed by the Ostwald ripening process which disturbs a direct size (and size distribution) control varying only the ion implantation parameters. Lifshitz, Slyozov and Wagner (LSW) [109, 107] gave an analytical time-invariant solution of the NC size distribution in diffusion controlled systems ( $t \to \infty$ ) assuming tiny nuclei embedded

Figure 2.2: A typical normalized particle radius distribution after Lifshitz, Slyozov, and Wagner for diffusion controlled systems (maximum at  $\rho = 1.135$ ) [107].

in a highly diluted solvent (volume fraction  $\phi \to 0$ ) with an initially Gaussian-type size distribution (see Fig. 2.2).

$$f(\rho,t) = \frac{const.}{(1+t/\tau_D)^{4/3}} \rho^2 \left(\frac{3}{3+\rho}\right)^{7/3} \left(\frac{3/2}{(3/2)-\rho}\right)^{11/3} \exp\left(\frac{-\rho}{(3/2)-\rho}\right)$$

(2.2)

$\rho$  is the a normalized NC radius with the mean particle radius  $r^*$ , which is also a function of time.

$$\rho = r/r^{\star} \le \frac{3}{2} \quad (f(\rho, t) = 0 \quad \text{for} \quad \rho > \frac{3}{2})$$

$\tau_D$  is a characteristic time constant of diffusion with diffusion constant D.

$$\tau_D = \frac{9[r^*(t=0)]^3}{4c_\infty DV_m R_c},$$

(2.3)

The LSW theory predicts that in the late stage of ripening the average NC radius evolves to the third potence with time t, i.e., the volume of tiny NC's ( $\sim R^3$ ) dissolves proportional with time [110, 108].

$$\overline{R}^{3}(t) - \overline{R}^{3}(t=0) = K(\phi) t$$

(2.4)

The coarsening rate  $K(\phi)$  is a monotonically increasing function of the volume fraction  $\phi$  which does not change with time [110]. The NC density decreases with 1/t for  $t \gg \tau_D$ . These results are valid for diffusional problems, where the diffusion fields of the particles are not directly interacting (mean-field approximation) [108]. This mean-field approximation holds for Si excess volume fractions up to 10 at.% as shown in recent investigations for the ion beam synthesis of Si NC's in thick gate oxides (e.g.,  $d_{ox} = 800 \text{ nm}$ ) [111]. For higher volume fractions the multi-particle competitive growth problem can be solved by a

#### Chapter 2: Ion beam synthesis of nanocrystals in $SiO_2$ for nanodot memories

superposition of *i* diffusion fields of several (N) point-like sources (or sinks) of strengthes  $Q_i$  [110, 112, 108, 104, 113].

$$c(\mathbf{r}) \simeq c_u + \frac{1}{4\pi D} \sum_{i=1}^{N} \frac{Q_i}{|\mathbf{r} - \mathbf{r}_i|} \quad \text{with} \quad \lim_{|\mathbf{r}| \to \infty} c(\mathbf{r}) = c_u$$

(2.5)

Alternatively, kinetic Monte Carlo simulations were used to predict the NC size and density evolution [114]. In case of NC synthesis in very thin oxides (e.g.,  $d_{ox} \approx 10 \text{ nm}$ ) also a diffusional interaction with the close absorbing surface of the Si substrate has to be taken into account [114]. For a very high impurity atom supersaturation in the oxide (volume fractions higher than 20 - 30 at.%) coalescence of NC's occurs which finally may lead to a closed buried layer formation (see Fig. 2.1). This process is used, for example, to create a buried oxide layer in a Si wafer [silicon on isolator (SOI)] in the so called SIMOX technique (separation by the **im**plantation of **ox**ygen), where a high fluence oxygen ion implantation is carried out with subsequent high temperature annealing [115, 116].

### 2.2 Diffusion of Si and Ge in SiO<sub>2</sub>

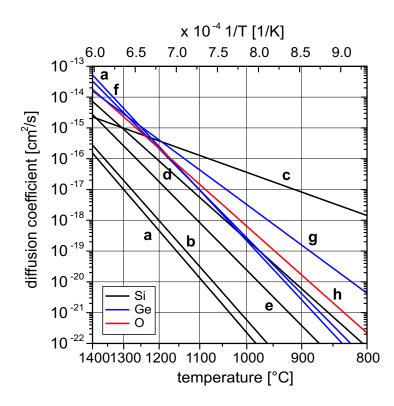

One of the key aspects of the nucleation and growth of Si, Ge or metal nanocrystals in  $SiO_2$  during ion beam synthesis is the diffusion of impurities in the oxide. This topic is of fundamental interest for the preparation of NC's from Si rich oxides in general (whether prepared by deposition or implantation techniques) thinking of memory or optical applications. However, the detailed microscopic kinetics of diffusion within the oxide layer is still hardly understood, although  $SiO_2$  is the most commonly used dielectric material in CMOS processing. Over the past two decades numerous experiments were carried out to enlighten the mechanism of Si diffusion in  $SiO_2$ , for instance. For this purpose different Si isotopes were used as tracers in stacked oxide layers, e.g., <sup>30</sup>Si atoms implanted in <sup>28</sup>SiO<sub>2</sub> layers (see Tab. 2.1 and Fig. 2.3). In general, the diffusion is described as a thermally activated process using the well-known Arrhenius function

$$D = D_0 \exp\left(-E_A/kT\right) \tag{2.6}$$

with diffusion coefficient at infinite temperature  $D_0$  (or  $kT gg E_A$ ) and activation energy  $E_A$  (k is the Boltzmann constant and T the temperature). The focus lies on both the detection of the diffusing specie - which is not a trivial question - and its diffusion kinetics in SiO<sub>2</sub>. Studying this way the self-diffusion of, e.g., Si and O gives also the perspective to understand the diffusion behavior of other (semiconductor) impurity atoms in SiO<sub>2</sub>.

In the literature values for the diffusivity of Ge and Si atoms in SiO<sub>2</sub> vary over several orders of magnitude (see Fig. 2.3) which is most likely due to a significant influence of the different preparation and annealing conditions in the experiments. Also a dependence of the oxide layer thickness is reported as the Si self-diffusivity is clearly enhanced in thinner oxides, where the Si/SiO<sub>2</sub> interface is located closer to the region of Si excess [117, 118]. Considering a typical value for the diffusion coefficient of Si, Ge or O atoms in SiO<sub>2</sub>, e.g.,  $D \leq 10^{-17} \text{ cm}^2/\text{s}$  at  $T \leq 1050^{\circ}\text{C}$  (see Fig. 2.3 and Tab. 2.1), the corresponding diffusion

| element | $\frac{D_0}{[\mathrm{cm}^2/\mathrm{s}]}$              | $E_A$ [eV]                                                                         | $\frac{D(1050^{\circ}\mathrm{C})}{[\mathrm{cm}^{2}/\mathrm{s}]}$                                                                                                      | Ref.                                                                                    | topic                                                                                                                                                                                                                                                 |

|---------|-------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Si      | $544.7 \\ 328 \\ 1.2 \times 10^{-9} \\ 1.378 \\ 33.2$ | $\begin{array}{c} 6.16 \\ 6.0 \\ 1.9 \\ 4.74{\pm}0.25 \\ 5.34 \\ 0.26 \end{array}$ | $\begin{array}{c} 1.9 \times 10^{-21} \\ 4.6 \times 10^{-21} \\ 6.9 \times 10^{-17} \\ 1.2 \times 10^{-18} \\ 1.5 \times 10^{-19} \\ > 4 \times 10^{-13} \end{array}$ | $[121]^{a}$ $[122]^{b}$ $[120]^{c}$ $[123]^{d}$ $[124]^{e}$ $[125, 126]$                | not specified<br>${}^{30}\text{SiO}_2 \text{ on } {}^{28}\text{SiO}_2$<br>Si NC growth in SiO <sub>2</sub><br>${}^{30}\text{Si}^+ \text{ implant in } {}^{28}\text{SiO}_2$<br>SiO <sub>2</sub> on ${}^{28}\text{SiO}_2$<br>sputtered SiO <sub>2</sub> |

| Ge      | $537 \\ 7250 \\ 8.9 \times 10^{-3} \\ 2.6$            | 5.38<br>5.69<br>3.9<br>4.7                                                         | $ \begin{array}{r} 1.7 \times 10^{-18} \\ 1.5 \times 10^{-18} \\ 1.2 \times 10^{-17} \\ 3.2 \times 10^{-18} \end{array} $                                             | $   \begin{bmatrix}     121]^{a} \\     [127]^{f} \\     [128]^{g} \\     [129]^{h}   $ | $\begin{array}{c} \mathrm{not} \ \mathrm{specified} \\ \mathrm{Ge^{+}} \ \mathrm{implant} \ \mathrm{in} \ \mathrm{SiO}_{2} \\ \mathrm{Ge} \ \mathrm{doped} \ \mathrm{SiO}_{2} \ \mathrm{on} \ \mathrm{SiO}_{2} \\ \end{array}$                        |

Table 2.1: Coefficients for the diffusion of Si and Ge atoms in SiO<sub>2</sub>. Exemplarily, the diffusivity at  $T = 1050^{\circ}$ C is specified varying in the case of Si diffusion over at least four orders of magnitude. The labelled references refer to the data in Fig. 2.3.

length  $L_D = \sqrt{Dt}$  yields only some angstroms (<4 Å) and below for a thermal annealing of 120 s. Such low values clearly contradict the observed formation of Si or Ge NC's in SiO<sub>2</sub> for thermal treatments at moderate temperatures and times ( $T \ll 1100^{\circ}$ C for less than 120 s) and also to the significant redistribution of Ge in SiO<sub>2</sub> as reported in chapter 5 for  $T \leq 950^{\circ}$ C annealing. 3D-kinetic Monte Carlo simulations reveal that under these circumstances ( $T = 1050^{\circ}$ C) the formation of Si NC's in thin oxides would take hours, not seconds as found by recent experiments [119]. However, a slightly higher diffusion coefficient ( $D = 6.9 \times 10^{-17}$ ,  $T = 1050^{\circ}$ C) is deduced studying the Si NC growth [120].

So far, the diffusion of Si in SiO<sub>2</sub> has been mainly discussed in terms of Si self-diffusion considering Si interstitials as the diffusing specie in the oxide [123, 124, 120, 122]. But, theoretical calculations reveal that models based on the formation and diffusion of isolated point defects (interstitials and vacancies in the classical sense) are likely misleading [130]. As a consequence, a mechanism of diffusion different from simple Si interstitial motion in SiO<sub>2</sub> should be considered. SiO molecules, which are generated at the Si/SiO<sub>2</sub> interface and emitted from there into the SiO<sub>2</sub> network during thermal treatment, are supposed to enhance the Si self-diffusivity in SiO<sub>2</sub> [131]. As shown by Uematsu *et al.* [118] this approach is suitable to explain the oxide thickness dependence on the diffusivity found by Fukatsu *et al.* [117]. But, the idea of SiO molecules squeezing through the oxide at elevated temperature without any interactions with the covalent SiO<sub>2</sub> network seems to be more than questionable [132]. However, as shown in Tab. 2.1 the energy of activation for the motion of Ge or the self-diffusion of Si or O in SiO<sub>2</sub> is conspicuously rather similar for all (about  $5.4 \pm 0.7 \, \text{eV}$ ), despite the different experimental conditions in the diffusion experiments. Thus, a common diffusion mechanism or specie should be considered.

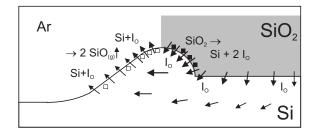

In this thesis (chapters 5 and 9) an oxygen vacancy mediated diffusion mechanism in

Figure 2.3: Diffusion coefficients for Si, Ge or O in  $SiO_2$  as a function of annealing temperature calculated from data as summarized in Tab. 2.1.

SiO<sub>2</sub> is proposed. The oxygen vacancy is the most common defect in SiO<sub>2</sub> [133]. An oxygen atom displaced from the SiO<sub>2</sub> network leaves two dangling Si bonds behind as the so-called bridging (Si-Si) or non-bridging (Si  $\cdot$  Si) oxygen-deficiency centers. It is known from *ab-initio* calculations that such defects have a very low energy of formation, especially at Si/SiO<sub>2</sub> interfaces [134, 135]; the energy of migration in SiO<sub>2</sub> is just 1.7 - 1.9 eV [136]. Migrating oxygen-vacancies induced long-range distortions in the SiO<sub>2</sub> network [133]. Thus, the Si diffusion in SiO<sub>2</sub> can be described as an effective process of multiple matrix perturbing and mixing events. In chapter 5 the enhanced diffusion of Ge in SiO<sub>2</sub> is explained in a similar way with the same diffusing specie being involved. Here, the Ge impurity atom gains a higher diffusivity sticking to an energetically favored position close to the highly mobile oxygen vacancies. This process is similar to the well-known transient enhanced diffusion of boron in Si bulk material [137], where the impurity atom diffusion is mediated by Si self-interstitials and not by oxygen vacancies as in SiO<sub>2</sub>.

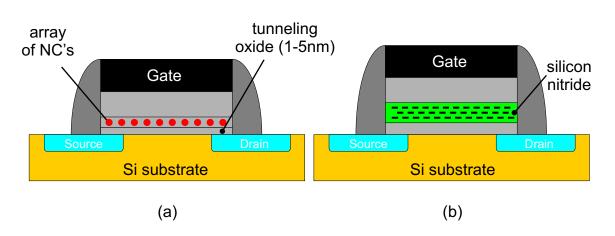

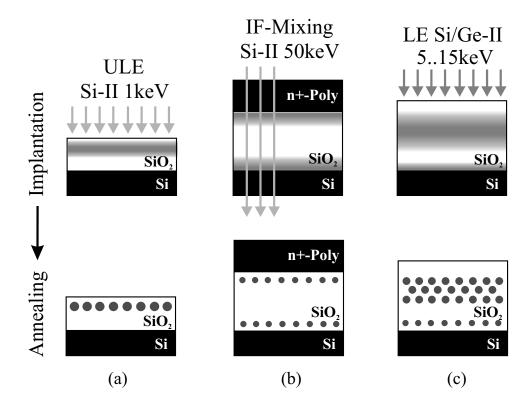

Figure 2.4: Main concepts of NC ion beam synthesis for nanodot memories. The ion implantation (II) is performed with different ion energies in or through 8, 15 and 20 - 30 nm thin oxide layers (typical sizes) in (a) - (c), respectively.

# 2.3 Different approaches for ion beam synthesis of NC's in thin SiO<sub>2</sub> layers

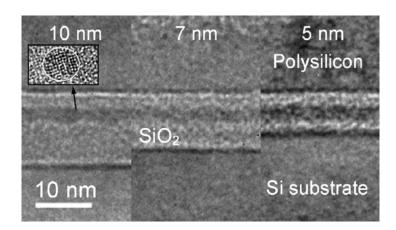

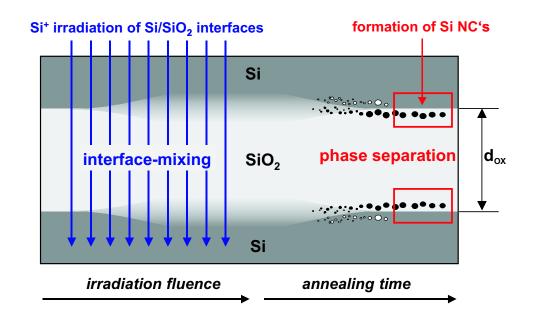

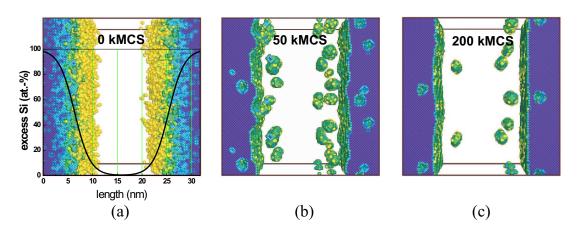

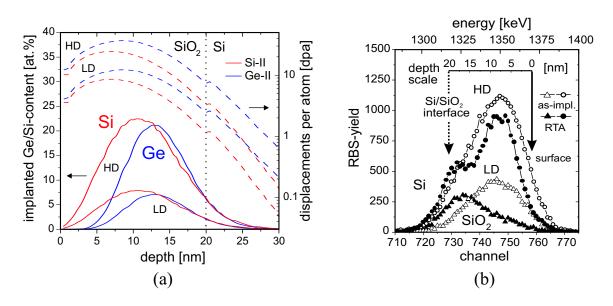

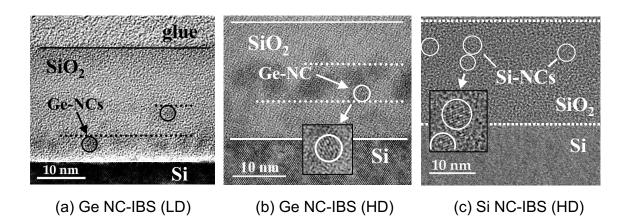

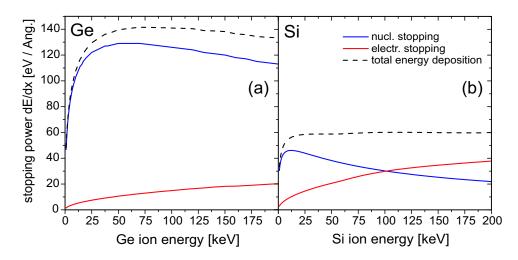

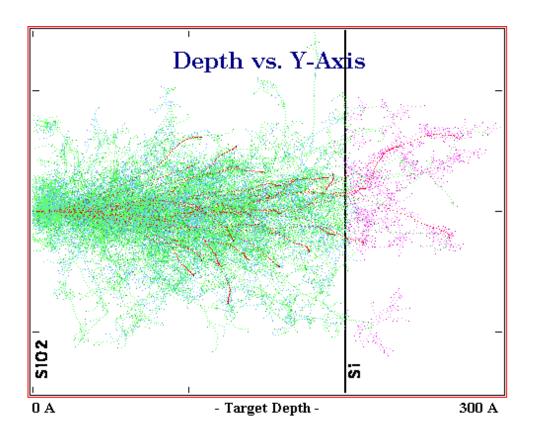

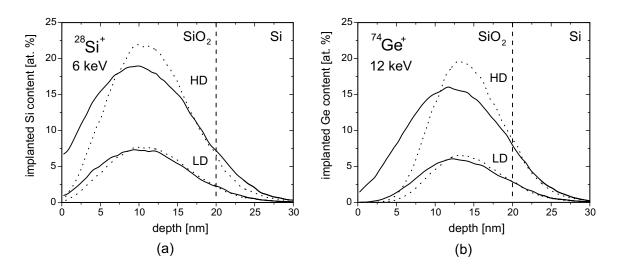

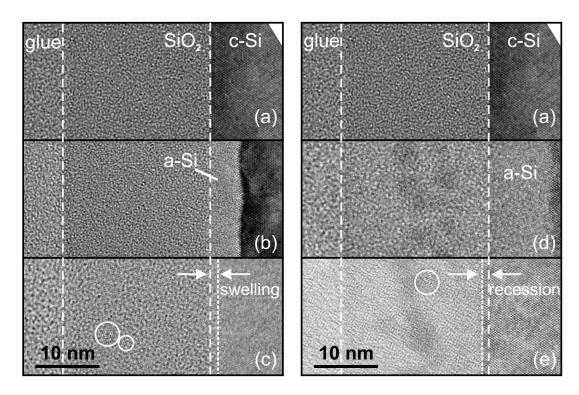

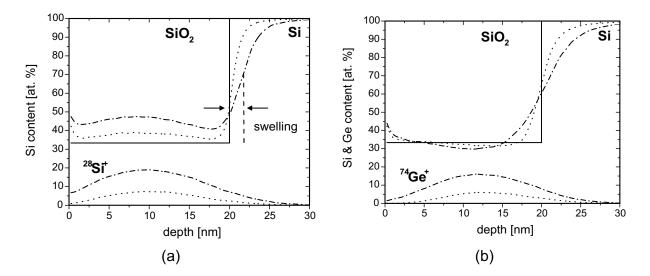

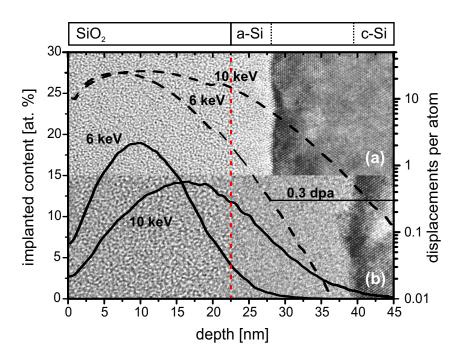

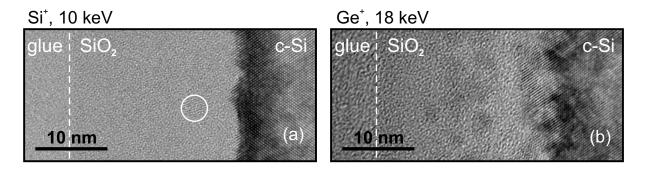

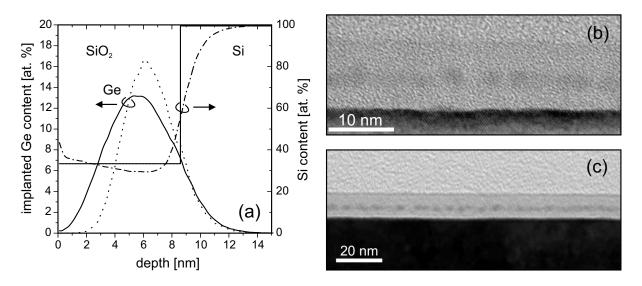

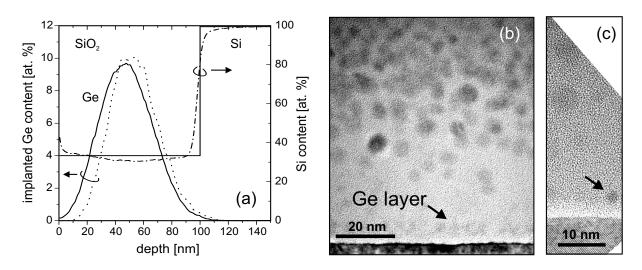

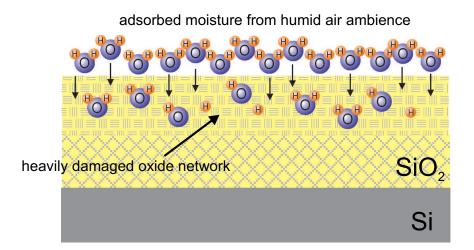

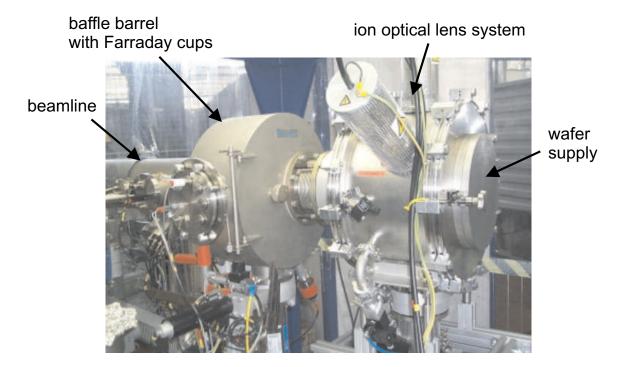

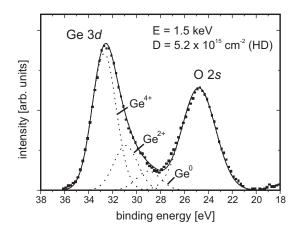

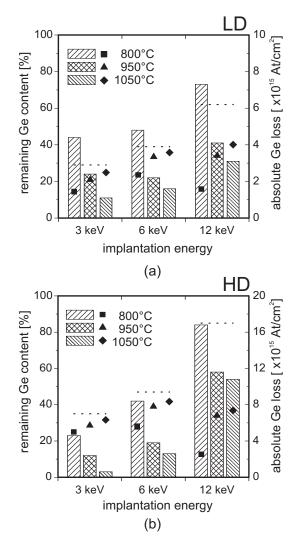

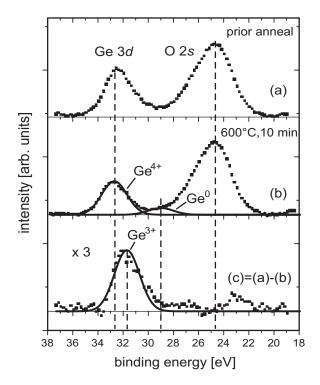

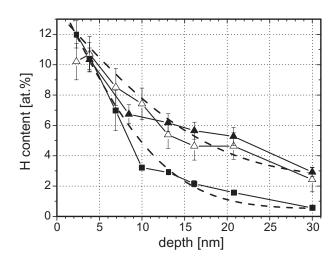

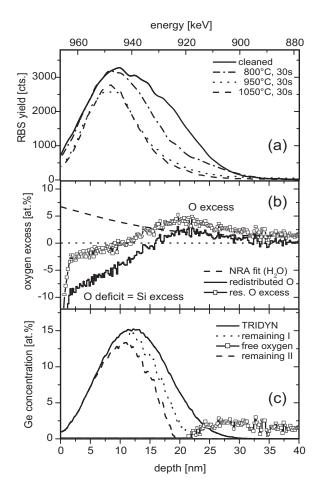

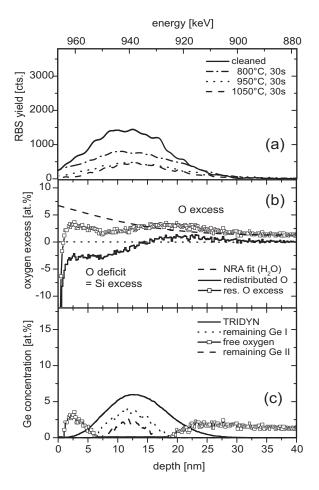

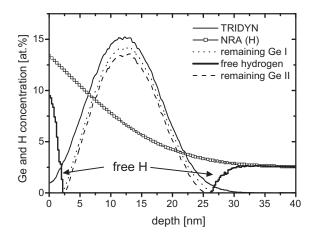

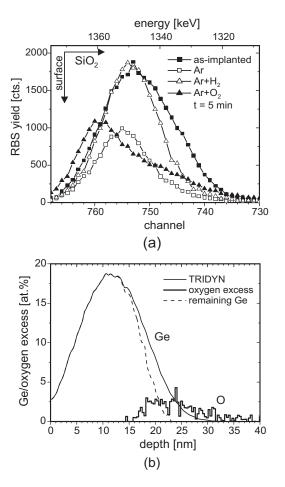

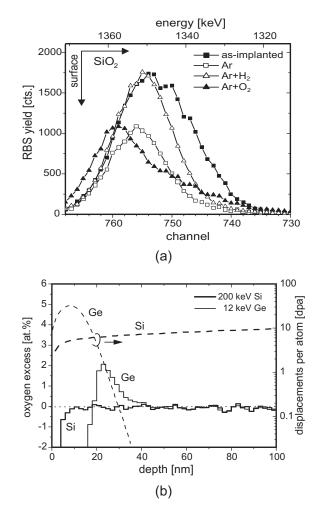

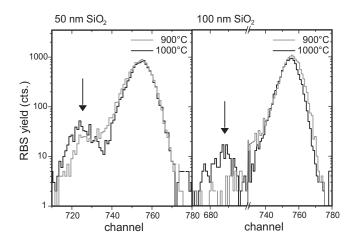

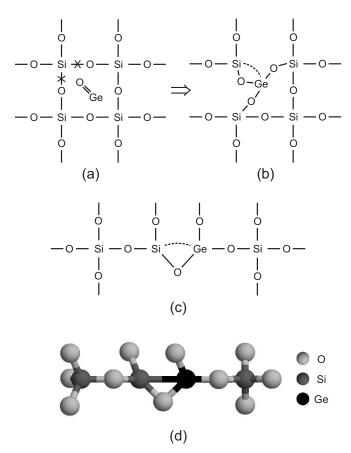

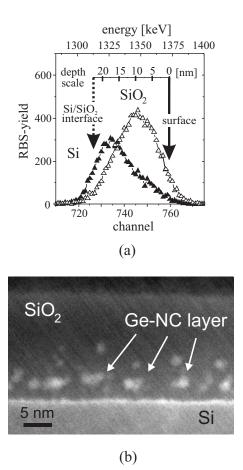

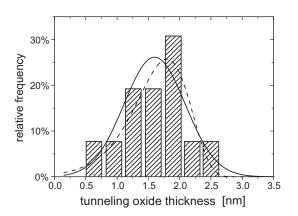

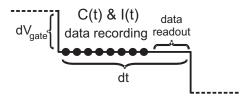

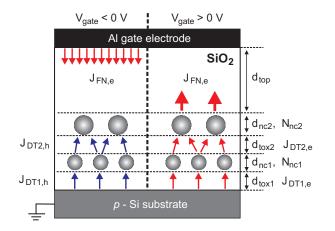

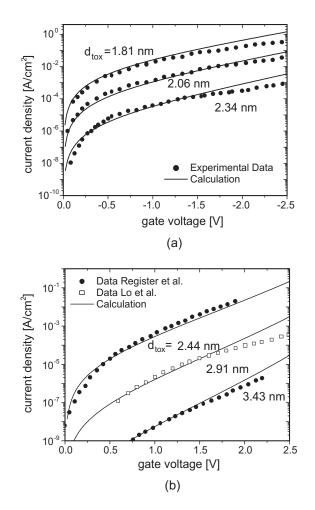

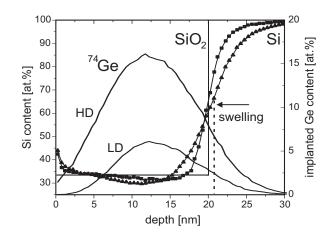

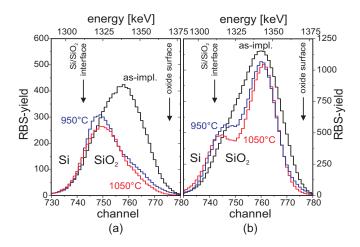

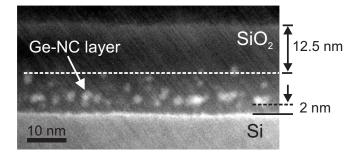

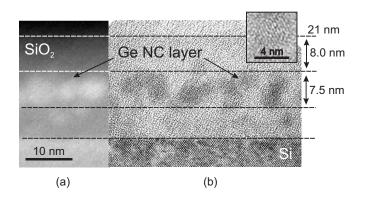

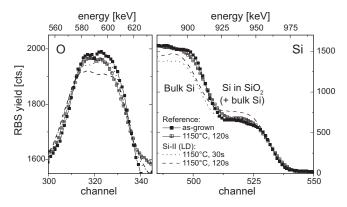

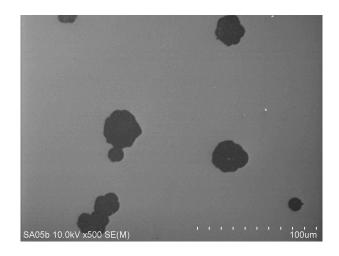

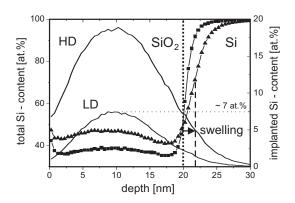

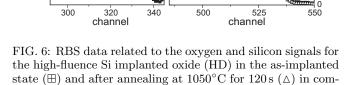

Figure 2.4 shows the three main routes of NC ion beam synthesis in thin oxide layers  $(d_{ox} \leq 30 \text{ nm})$  aiming at memory device applications. The choice of different ion energies and oxide thicknesses results in different NC distributions after annealing. (i) A very shallow Si ion profile is realized close to the oxide surface after annealing as shown in Fig. 2.4(a) using Si<sup>+</sup> ultra-low-energy (ULE)-implantation ( $E \approx 1 \text{ keV}$ ) at fluences of  $D \geq 1 \times 10^{16} \text{ cm}^{-2}$  in  $d_{ox} \leq 10 \text{ nm}$  thin SiO<sub>2</sub> layers which yields a very high peak Si excess of  $\geq 33 \text{ at.}\%$  in the oxide [114]. (ii) A completely different approach is pursued irradiating a poly-Si(Gate) | SiO<sub>2</sub> | Si(bulk) layer stack [Fig. 2.4(b)]. Collisional cascades of displaced atoms lead to a mixing of both formerly sharp Si/SiO<sub>2</sub> interfaces. During subsequent annealing and interface reconstruction a rather symmetric arrangement of Si NC's forms embedded in SiO<sub>2</sub> in vicinity to both electrodes, the poly-Si gate and Si bulk layer. (iii) By low-energy (LE)-implantation [Fig. 2.4(c)] both components - primary implanted Si ions and backward mixed Si atoms - contribute to the resulting NC distribution. A comparison of Si and Ge ion implantation reveals that in the latter case additionally a redistribution of Ge during annealing has to be taken into account. Each of these