# Ersatzschaltbilddarstellung von EBG-Filterstrukturen auf Leiterplatten

Dipl.-Ing. (FH) Matthias Friedrich, M.Sc. Christian Bednarz, Prof. Dr.-Ing. Marco Leone, Otto-von-Guericke-Universität Magdeburg – Lehrstuhl Theoretische Elektrotechnik

## 1 Einleitung

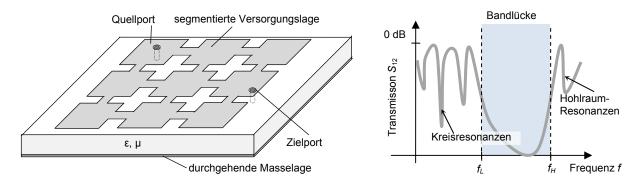

Zur Verringerung von Störausbreitungen innerhalb der Versorgungslagen (power delivery network, PDN) einer mehrlagigen Leiterplatte können elektromagnetischer Bandfilter (electromagnetic bandgap, EBG) angewandt werden (Abb.1, links). Sie bestehen aus einer Anzahl von kleinen Kupferflächen (Patch) über einer durchgehenden Masselage und können sowohl galvanisch durch kurze Verbindungen oder auch kapazitiv verbunden sein. Im Gegensatz zu durchgehenden Lagenpaaren verhält sich die EBG-Struktur wie ein periodisches Filter, welches die Störausbreitungen innerhalb eines bestimmten Frequenzbandes (Bandlücke, bandgap) stark dämpft. Das prinzipielle Transmissionsverhalten zwischen zwei Ports ist in Abb. 1, rechts skizziert.

Bild 1: Einfache EBG-Struktur (links) und typisches Übertragungsverhalten (rechts)

Die zum Design solcher EBG-Strukturen relevanten Parameter sind die obere und untere Grenzfrequenzen  $f_H$  und  $f_L$  der Bandlücke (Abb. 1, rechts). Diese sind jedoch nicht exakt definiert. Die Bandlücke wird nach oben hin durch die erste Hohlraumresonanz eines einzelnen Patches begrenzt. Diese Resonanzfrequenz kann direkt mit Hilfe der effektiven Kantenlänge eines Patches  $a_e$  abgeschätzt werden [1]:

$$f_H \approx \frac{c_0}{2a_e\sqrt{\varepsilon_r}}.$$

(1)

Zur Bestimmung der unteren Grenze der Bandlücke muss der Frequenzgang der Gesamtstruktur mit Hilfe geeigneter Modelle bzw. numerischer Feldsimulationen berechnet werden [1]-[9]. In den letzten Jahren wurden dazu unterschiedliche Ansätze entwickelt und einfache Designregeln abgeleitet (z.B. [1],[2]). Ebenfalls wurden verschiedene Erstsatzschaltbilddarstellungen vorgestellt [1],[5],[7],[8], welche im Wesentlichen auf die bekannten Lösungen von Mikrostreifenleitungen zurückgreifen.

Als eine effiziente und genaue Alternative wird in diesem Paper ein Ersatzschaltbild auf Basis gekoppelter Induktivitäten zur Modellierung der einzelnen Patches vorgestellt. Als explizites Anwendungsbeispiel wird die sehr verbreitete EBG-Form mit galvanischen Verbindungen (Abb. 1, links) aus [1]-[4] betrachtet. Für die quadratischen Patches, wel-

che mit kurzen Mikrostreifenleitungen verbunden sind, können alle Ersatzschaltbildelemente nach [9],[10] ermittelt werden. Die Randeffekte entlang der offenen Ränder der Patches sowie das inhomogene Dielektrikum werden durch Einführung einer äquivalenten Patch-Größe sowie einer effektiven Permittivität berücksichtigt. Die Validierung des vorgestellten Modells erfolgt an numerischen 3D-Vollwellensimulationen und Messungen. Das Modell erlaubt eine sehr gute Beschreibung des Frequenzverhaltens unterhalb der Bandlücke und eignet sich zur Abschätzung der unteren Grenze  $f_L$ . Es ist allgemeingültig und kann auf jede Patch-Geometrie angewendet werden, für die geschlossene Lösungen für die Induktivitäten vorhanden sind.

#### 2 Induktives Netzwerkmodell

Im Frequenzbereich unterhalb der Bandlücke und damit weit unterhalb der ersten Patch-Resonanz (1) sind die einzelnen Patches elektrisch klein. Ein Modell für elektrisch kleine Parallelplatten-Strukturen wurde auf Basis einer einfachen induktiven Ersatzschaltbilddarstellung in [10]-[12] entwickelt. Für die Rechteckgeometrie wurden für die Induktivitäten geschlossene Formelausdrücke aufgestellt [10]. Wie in [13] gezeigt, berücksichtigt dieses zweidimensionale, quasistatische Modell auch die induktiven Anteile des Verschiebungsstroms und erlaubt somit eine genauere Modellierung im Gegensatz zu einem einfachen Leitungsmodell kurzer Länge (z.B. [1]).

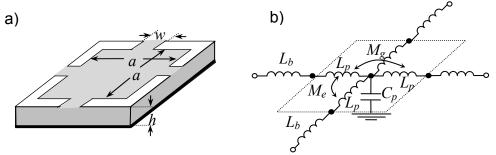

Die Netzwerkdarstellung eines einzelnen Patches mit angeschlossenen Mikrosteifenleitungen ist in Abb. 2 dargestellt, wobei nur ausgewählte Kopplungen eingezeichnet wurden.

**Bild 2:** Einzelner EBG-Patch mit vier Mikrostreifenleitungsanschlüssen (a), Ersatzschaltbilddarstellung mit verkoppeltem, induktivem Netzwerk und Plattenkapazität  $C_p$  (b)

#### 2.1 Randeffekte und effektive Permittivität

Für die betrachtete Anwendung sind die lateralen Abmessungen a eines Patches zwar größer als die Höhe h, jedoch nicht groß genug, um von idealen Randbedingungen auszugehen. Das Gleiche gilt für die Mikrostreifenleitung zwischen den Patches, bei denen die Breite w in etwa in derselben Größenordnung wie die Höhe h liegt.

Zur genauen Modellierung der Struktur müssen daher die Randeffekte an den offenen Rändern der Mikrostreifenleitungen und Patches berücksichtigt werden. Dazu wurde in [9] ein Vergrößerungsfaktor zur Berechnung einer effektiven Kantenlänge eingeführt, welcher nur vom Verhältnis h/w abhängt:

$$\eta(h/w) = \frac{w_e}{w} = \frac{4\pi(h/w)}{\ln(1+4(h/w)(8(h/w)+\sqrt{(8h/w)^2+\pi^2}))}.$$

(2)

Analog wird dieser Vergrößerungsfaktor zur Berechnung der effektiven Patch-Maße genutzt:

$$a_{e} = a \cdot \eta(a, h). \tag{3}$$

Für EBG-Strukturen, die sich auf der Unter- oder Oberseite einer Leiterplatte befinden, muss zusätzlich eine effektive Permittivität  $\varepsilon_e$  ermittelt werden, welche das inhomogene Medium berücksichtigt. Diese effektive Konstante berechnet sich aus [9],[14]:

$$\varepsilon_e = 1 + \frac{\varepsilon_r - 1}{4} \left( 1 + \left( 1 + 12 \frac{a}{h} \right)^{-1/2} \right)^2. \tag{4}$$

Die Kapazität eines Patches wird durch Einsetzen der effektiven Plattenabmessungen (3) sowie der effektiven Permittivität (4) aus der Formel für einen idealen Parallelplattenkondensator berechnet:

$$C_p = \varepsilon_0 \, \varepsilon_e \, \frac{a_e^2}{h} \,. \tag{5}$$

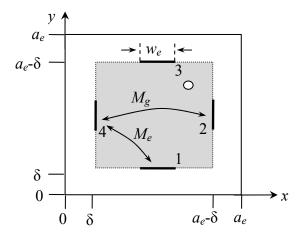

## 2.2 Berechnung der Ersatzschaltbildelemente

Für den symmetrischen EBG-Patch (Bild 2) können die allgemeinen Ausdrücke für die Eigen- und Gegeninduktivitäten der vier Ports deutlich vereinfacht werden. Da die Patch-Abmessungen zur Berücksichtigung der Randeffekte auf die effektiven Werte vergrößert sind (Abb. 3), liegen die Ports nicht mehr direkt an der Kante, sondern sind um den Abstand:

$$\delta = \frac{a_e - a}{2} = a \left( \frac{\eta(a, h) - 1}{2} \right) \tag{6}$$

verschoben (siehe Bild 3).

**Bild 3:** Lokales Koordinatensystem zur Berechnung der Eigen- und Gegeninduktivität innerhalb eines Patches mit den effiktiven Kantenabmessungen  $a_e \times a_e$

#### 2.2.1 Induktivität einer kurzen Mikrostreifenleitung

Analog zu [1] wird die kurze Mikrostreifenleitung durch eine Induktivtät beschrieben. Nutzt man die effektive Breite  $w_e$  einer idealen Parallelplattenleitung, berechnet sich diese aus [15]:

$$L_b = \frac{\mu \, l \, d}{w_e} \,. \tag{7}$$

## 2.2.2 Eigeninduktivität

Aufgrund der Symmetrie ist die Eigeninduktivität aller Ports gleich. Nutzt man eine Taylorreihenentwicklung aller Funktionen aus [10] mit kleinen Argumenten und einigen weiteren Näherungen, erhält man eine einfache Lösung für die Eigeninduktivität [9], welche für die hier betrachteten üblichen Geometrieparameter gültig ist:

$$L_{ii} \approx \frac{\mu h}{2\pi} \left( \ln \left( \frac{a_e^2}{w_e \, \delta} \right) - 0.79 \right). \tag{8}$$

## 2.2.3 Gegeninduktivitäten

Wie in Abb. 2 und Abb. 3 gezeigt, muss zwischen zwei unterschiedlichen Gegeninduktivitäten unterschieden werden. Für die Gegeninduktivität  $M_e$  zwischen zwei Ports an einer Ecke erhält man aus [10] nach mehreren Näherungen und Vereinfachungen den Ausdruck [9]:

$$M_e \approx \frac{\mu h}{2} \left( \left( \frac{\delta}{a_e} \right)^2 - 0.11 \right).$$

(9)

Die Gegeninduktivität  $M_g$  zwischen zwei Ports an gegenüberliegenden Kanten kann analog zu den vorherigen Formeln mit [9] genähert werden:

$$M_g \approx \frac{\mu h}{4\pi} \left( \left( \pi \frac{\delta}{a_e} \right)^2 - 2,07 \right).$$

(10)

#### 2.2.4 Induktivität eines vertikalen Ports

Zur Modellierung eines vertikalen Ports innerhalb eines Patches muss jeweils ein weiterer induktiver Zweig im Netzwerkmodell Abb. 2b hinzugefügt werden. Für die Berechnung der Eigeninduktivität des Ports sowie der Gegeninduktivitäten zu den Mikrostreifenports müssen die exakten Ausdrücke aus [10] ausgewertet werden.

## 3 Validierungsbeispiele

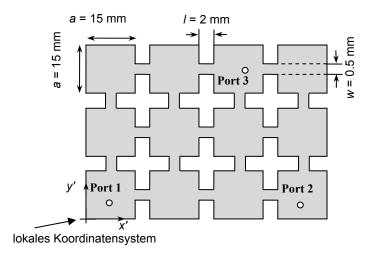

Zur Validierung des vorgestellten Netzwerkmodells wird eine 3D-Vollwellensimulation [16] verwendet. Die Geometrieparameter des ersten Beispiels sind in Abb. 4 gezeigt. Die EBG Struktur ist auf die obere Lage einer 51 mm × 68 mm Leiterplatte mit durchgehender Masselage aufgebracht. Drei Ports sind wie in Abb. 4 gezeigt in unterschiedlichen Patches und unterschiedlichen lokalen Positionen angeordnet.

**Bild 4:** 4×3 EBG-Validierungsbeispiel auf einer Leiterplatte mit h = 0.5 mm und  $\varepsilon_r = 4.4$  und drei Ports mit Radius  $r_0 = 0.1$  mm.  $([x_1, y_1] = [7, 5]$  mm,  $[x_2, y_2] = [7, 5]$  mm und  $[x_3, y_3] = [8.7; 5.7]$  mm)

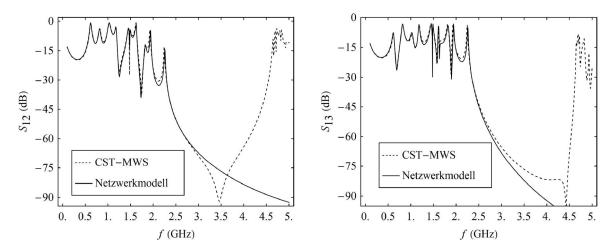

**Bild 5:** 4×3 EBG-Validierungsbeispiel auf einer Leiterplatte h = 0.5 mm, w = 0.5 mm und  $\varepsilon_r = 4.4$  Übertragungsverhalten zwischen Port 1 und 2 (links) bzw. Port 3 (rechts)

Abb. 5 zeigt die berechneten Frequenzgänge für die S-Parameter  $S_{12}$  und  $S_{13}$  zwischen Port 1 und 2 (links) bzw. Port 3 (rechts). Wie man anhand der numerischen Referenzergebnisse (CST-MWS) erkennt, wird das Frequenzverhalten bis hin zur Bandlücke sehr gut reproduziert. Da das induktive Ersatzschaltbild keine Hohlraummoden berücksichtigt, nehmen erwartungsgemäß die Abweichungen darüber hinaus mit steigender Frequenz zu. Die rechnerische Effizienz des entwickelten Netwerkmodells wird anhand des Rechenzeitvergleichs deutlich. Die Vollwellensimulation benötigte etwa 5 h auf 3 Kernen einer 16 × 3 GHz Intel CPU, während das Netzwerkmodell lediglich 10 s auf demselben Rechner benötigte.

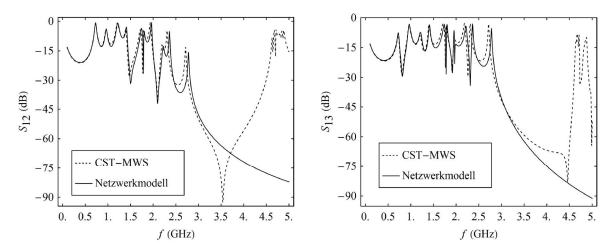

Als weiteres Validierungsbeispiel wird die Breite der Mikrostreifenleitungen verdreifacht (w = 1,5 mm). Die berechneten S-Parameter-Frequenzverläufe sind in Abb. 6 dargestellt. Wie zu erkennen ist, bewirkt die Verbreitung der Mikrostreifenleitung eine Verschiebung der unteren Grenze der Bandlücke um ca. 500 MHz nach oben. Der Vergleich mit den Referenzergebnissen der Vollwellensimulation weist bereits unterhalb der Bandlücke leichte Abweichungen auf. Die erzielte Genauigkeit ist dennoch zur Abschätzung der unteren Grenzfrequenz  $f_L$  vollkommen ausreichend.

**Bild 6:** 4×3 EBG-Validierungsbeispiel auf einer Leiterplatte h = 0.5 mm, w = 1.5 mm und  $\varepsilon_r = 4.4$  Übertragungsverhalten zwischen Port 1 und 2 (links) bzw. Port 3 (rechts)

## 4 Experimentelle Validierung

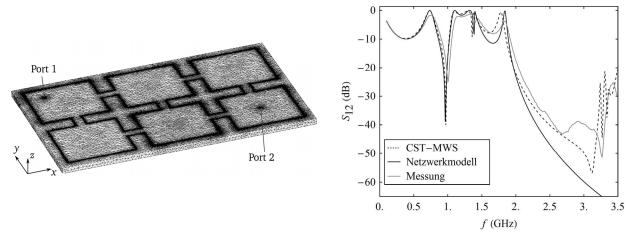

Zur experimentellen Validierung des Netzwerkmodells wird die in Abb. 7 gezeigte 3 × 2 EBG-Struktur betrachtet. Diese wurde auf eine handelsübliche FR4-Leiterplatte mit Höhe h = 1,6 mm aufgebracht. Da die dielektrischen Eigenschaften von FR4 starken Toleranzen unterworfen sind, wurde der exakte Wert von  $\varepsilon_r$  aus der Messung der Kapazität eines einzelnen Patches ermittelt. Die Patches mit der Kanten a=20 mm sind mit Mikrostreifenleitungen der Länge l = 5 mm und Breite w = 5 mm verbunden. Es wurde in zwei unterschiedlichen Patches jeweils ein Port mit dem Radius  $r_0$  = 0,6 mm an der lokalen Position  $[x_1, y_1] = [5 \text{ mm}, 5 \text{ mm}]$  bzw.  $[x_2, y_2] = [10 \text{ mm}, 10 \text{ mm}]$  angeordnet. Als zusätzliche Validierung wurde eine 3D-Vollwellensimulation der Struktur durchgeführt. Im Vergleich mit den vorherigen Simulationen wurde die Zellenanzahl deutlich erhöht, um eine aussreichende Konvergenz sicherzustellen. Das endgültige Simulationsmodell besteht aus ca. 2 Millionen Zellen (Abb. 7) und benötigt ca. 30 h Rechenzeit. Der Vergleich für den Transmissionsparameter  $S_{12}$  wird in Abb. 7 (rechts) gezeigt. Wie man erkennt, zeigen alle Ergebnisse eine zufriedenstellende Übereinstimmung im Frequenzbereich unterhalb der Bandlücke. Auch die für das Design interessante Untergrenze der Bandlücke wird gut vorausgesagt. Als möglicher Grund für die verbleibenden Abweichungen sind die Vernachlässigung der Verluste, die Frequenzabhängigkeit des Trägermaterials FR4 sowie die nichtideale Einspeisung im Messaufbau zu nennen.

Bild 7: Vergleich zwischen Messungen, Simulation und Netzwerkmodell einer 3 × 2 EBG-Struktur

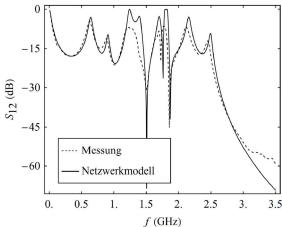

Als weiteres messtechnisches Beispiel wird die in Abb. 8 (links) dargestellte 4 × 4 EBG-Struktur betrachtet. Das Trägermaterial der Leiterplatte besteht aus PTFE (Teflon), dessen Permittivität mit dem Wert  $\varepsilon_r$  = 2,55 über einen größeren Frequenzbereich als konstant angenommen werden kann. Auch der dielektrische Verlustfaktor dieser Leiterplatte  $\tan\delta=0,005$  ist wesentlich geringer als der von herkömmlichen FR4-Leiterplatten. Auf dem Dielektrikum mit der Dicke h = 0,75 mm sind 20 mm × 20 mm große Patches aufgebracht, welche mit Mikrosteifenleitungen der Länge 5 mm und Breite 2 mm verbunden sind. Wie man in Abb. 8 erkennt, wurde jeweils ein Port im (1,1)-Patch und im (3,3)-Patch platziert. Sie befinden sich jeweils lokal an Koordinaten [ $x_1, y_1$ ] = [10 mm, 10 mm] und [ $x_2, y_2$ ] = [15 mm, 15 mm] und haben den Radius  $r_0$  = 0,6 mm. Die gemessenen S-Parameter-Freqeunzverläufe sind in Abb. 8 (rechts) dargestellt.

**Bild 8**: Messaufbau einer 4 × 4 EBG-Struktur (links) und Vergleich zwischen Messungen und Netzwerkmodell (rechts)

Auch bei diesem Beispiel zeigt sich eine zufriedenstellende Übereinstimmung zwischen Messung und Netzwerkmodell. Die untere Grenze der Bandlücke kann auch in diesem Fall mit guter Genauigkeit abgeschätzt werden.

#### Zusammenfassung

Zur Modellierung von EBG-Strukturen wurde eine neue Netzwerkdarstellung vorgestellt. Sie erlaubt die Berechnung des Frequenzverhaltens im Bereich untehalb der Bandlücke. Für die Bestimmung der Netzwerkelemente wurden einfache Formeln in geschlossener Form angegeben. Zur Berücksichtigung von Randeffekten wurden die Lösungen für Mikrostreifenleitungen für die betrachtete 3D-Geometrie erweitert. Das Netzwerkmodell erlaubt die direkte Einbettung der EBG-Versorgungslagen in eine SPICE-basierte Systemsimulation. Die Validierung des Modells anhand von 3D-Vollwellensimulationen und Messungen zeigen eine sehr gute Übereinstimmung in dem praktisch interessierenden Frequenzbereich unterhalb der Bandlücke.

#### Referenzen

- [1] de Paulis, F.; Raimondo, L.; Orlandi, A.; Liehui Ren; Jun Fan; , "Equivalent circuit models for evaluation of bandgap limits for planar electromagnetic bandgap structures," *Electromagnetic Compatibility (EMC), 2010 IEEE International Symposium on*, vol., no., pp.770-775, 25-30 July 2010

- [2] Di Febo, D.; Nisanci, M.H.; de Paulis, F.; Orlandi, A.; , "Impact of planar electromagnetic band-gap structures on IR-DROP and signal integrity in high speed printed circuit boards," *Electromagnetic Compatibility (EMC EUROPE)*, 2012 International Symposium on , vol., no., pp.1-5, 17-21 Sept. 2012.

- [3] F. De Paulis and A. Orlandi, "Accurate and efficient analysis of planar electromagnetic band-gap structures for power bus noise mitigation in the GHz band," *Progress In Electromagnetics Research B*, Vol. 37, 59-80, 2012.

- [4] Raimondo, L.; de Paulis, F.; Orlandi, A.; , "A Simple and Efficient Design Procedure for Planar Electromagnetic Bandgap Structures on Printed Circuit Boards," *Electromagnetic Compatibility, IEEE Transactions on*, vol.53, no.2, pp.482-490, May 2011

- [5] Mohajer-Iravani, B.; Ramahi, O.M.; , "Wideband Circuit Model for Planar EBG Structures," *Advanced Packaging, IEEE Transactions on* , vol.33, no.1, pp.169-179, Feb. 2010

- [6] de Paulis, F.; Raimondo, L.; Orlandi, A.; , "Impact of Shorting Vias Placement on Embedded Planar Electromagnetic Band Gap Structures Within Multilayer Printed Circuit Boards," *Microwave Theory and Techniques, IEEE Transactions on*, vol.58, no.7, pp.1867-1876, July 2010

- [7] Ki Hyuk Kim; Aine, J.E.S.; , "Analysis and Modeling of Hybrid Planar-Type Electromagnetic-Bandgap Structures and Feasibility Study on Power Distribution Network Applications," *Microwave Theory and Techniques, IEEE Transactions on*, vol.56, no.1, pp.178-186, Jan. 2008

- [8] Rogers, S.D.; "Electromagnetic-Bandgap Layers for Broad-Band Suppression of TEM Modes in Power Planes," *Microwave Theory and Techniues, IEEE Transactions on*, vol.53, no.8, pp. 2495-2505, Aug. 2005

- [9] M.Friedrich; C. Bednarz; M.Leone, "Efficient Equivalent Circuit Representation of Electromagnetic Bandgap Structures", ," *Electromagnetic Compatibility (EMC EUROPE), 2013 International Symposium on*, vol., no., pp.1-5, 2-6 Sept. 2013.

- [10] Friedrich, M.; Leone, M.; , "Inductive Network Model for the Radiation Analysis of Electrically Small Parallel-Plate Structures," *Electromagnetic Compatibility, IEEE Transactions on* , vol.53, no.4, pp.1015-1024, Nov. 2011

- [11] Jingook Kim; Liehui Ren; Jun Fan; , "Physics-Based Inductance Extraction for Via Arrays in Parallel Planes for Power Distribution Network Design," *Microwave Theory and Techniques, IEEE Transactions on*, vol.58, no.9, pp.2434-2447, Sept. 2010

- [12] Liehui Ren; Jingook Kim; Gang Feng; Archambeault, B.; Knighten, J.L.; Drewniak, J.; Jun Fan; , "Frequency-dependent via inductances for accurate power distribution network modeling," *Electromagnet-ic Compatibility, 2009. EMC 2009. IEEE International Symposium on*, vol., no., pp.63-68, 17-21 Aug. 2009

- [13] Friedrich, M.; Leone, M.; , "Quasi-Static Inductance of Vertical Interconnections in Parallel-Plane Structures," *Electromagnetic Compatibility, IEEE Transactions on* , vol.54, no.6, pp.1302-1305, Dec. 2012

- [14] Balanis, C.A.: Antenna Theory. John Wiley & Sons, Inc., New York, 1997.

- [15] S. Ramo, J.R. Whinnery, T. Van Duzer, Fields and Waves in Communication Electronics. Wiley, New York, 1965

- [16] Microwave Studio, Computer Simulation Technology (CST). (2013). Information online Available: <a href="https://www.cst.de">www.cst.de</a>