# Emulator- und kostenbasierte Analyse von Network-on-Chip

Von der Fakultät für Elektrotechnik und Informatik der Gottfried Wilhelm Leibniz Universität Hannover zur Erlangung des akademischen Grades Doktor-Ingenieur (abgekürzt: Dr.-Ing.) genehmigte Dissertation

von

Diplom-Ingenieur, Diplom-Kaufmann

**Martin Christian Neuenhahn**

Geboren am 9. Dezember 1976 in Herten

1. Referent: Prof. Dr.-Ing. Holger Blume

Korreferent: Prof. Dr.-Ing. Tobias Noll

Prüfungsvorsitz: Prof. Dr.-Ing. Bernhard Wicht

Tag der Promotion: 26. Juni 2019

Für Jutta, Carlotta und Hugo

#### Vorwort

Die vorliegende Arbeit wurde während meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Lehrstuhl für Allgemeine Elektrotechnik und Datenverarbeitungssysteme der Rheinisch-Westfälischen Technischen Hochschule in Aachen begonnen. Mein herzlicher Dank gehört Herr Univ.-Prof. Dr.-Ing. Tobias G. Noll für die interessante Themenstellung, die Unterstützung und Betreuung, sowie die Übernahme des Korreferates.

Des Weiteren möchte ich ebenso herzlich Herrn Univ.-Prof. Dr.-Ing. habil. Holger Blume, dem Leiter des Instituts für Mikroelektronische Systeme an der Leibniz Universität Hannover, danken. Er gab mir die Möglichkeit, diese Arbeit an seinem Institut zu beenden. Ausdrücklich möchte ich mich ich für sein außerordentliches Interesse an dieser Arbeit, die engagierten Diskussionen und die Betreuung in der finalen Phase dieser Doktorarbeit bedanken.

Allen ehemaligen Kollegen, studentischen Hilfskräften, Studien-, Master- und Diplomarbeitern gebührt ein besonderer Dank für die unterstützende Zusammenarbeit und für die angenehme und konstruktive Bereicherung.

Mein größter Dank gilt meiner Familie. Meiner Frau Jutta, meiner Tochter Carlotta, meinem Sohn Hugo, meinen Eltern, meinem Bruder, Schwägerinnen, Schwager, Neffen, Schwiegereltern, Tanten u Onkel. Ohne ihre bedingungslose Unterstützung und den gebotenen Rückhalt wäre dieser Lebensweg nicht möglich gewesen.

Ebenso möchte ich mich bei meinen engen Freunden bedanken, die immer an mich geglaubt haben.

Düsseldorf, im Juli 2019

Martin C. Neuenhahn

## Kurzfassung

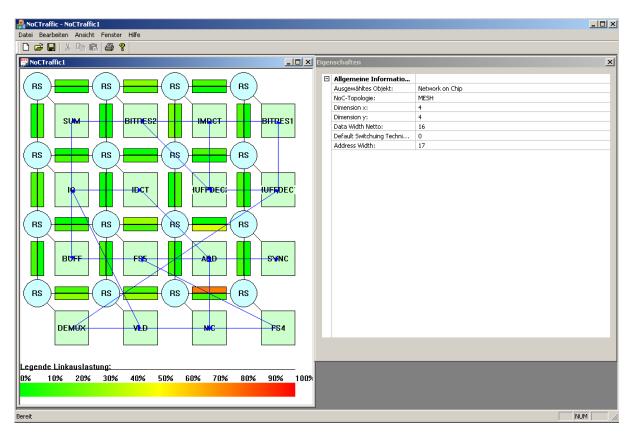

Die Komplexität der Kommunikation auf aktuellen und zukünftigen Multi-Kern System on Chip ist mit gängigen Kommunikationsarchitekturen wie Bussen oder Punkt-zu-Punkt Verbindungen kaum zu beherrschen. Network-on-Chip (NoC) stellen eine mögliche Lösung dieses Problems dar. Im Rahmen dieser Arbeit wurde ein modulares und parametrisierbares Network-on-Chip entwickelt. Dies unterstütze eine Vielzahl von NoC-Parametern wie zum Beispiel Topologie, Routing Algorithmus und Vermittlungstechnik. Die erstellte VHDL Bibliothek für NoC ermöglicht die automatische Generierung von NoC-Beschreibungen in VHDL.

Für die Untersuchung der Performance, Fläche und Verlustleistung der modellierten NoC wurden exemplarische VLSI-Implementierungen der NoC-Komponenten mit Hilfe von Standardzellen erstellt. Zur Reduzierung der Kosten und Steigerung der Performance sind physikalisch optimierte Kernkomponenten in Kombination mit Standardzellen verwendet worden. Dies reduziert die Kosten der NoC-Implementierungen signifikant wobei die Parametrisierbarkeit erhalten bleibt. Die Kosten für die NoC-Komponenten in Abhängigkeit der NoC-Parameter wurden mit mathematischen Modellen beschrieben. Diese Modelle erlauben die Abschätzung der zu erwartenden Kosten schon in frühen Entwurfsphasen.

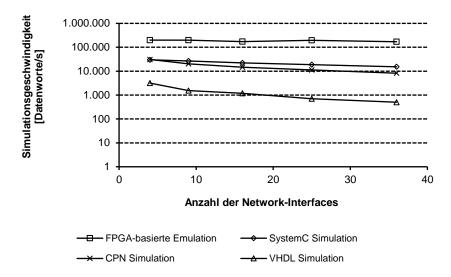

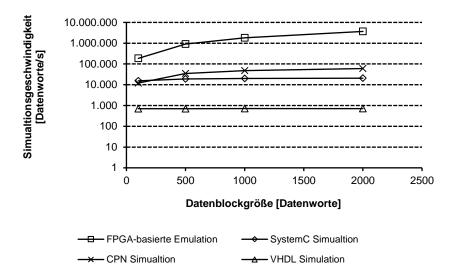

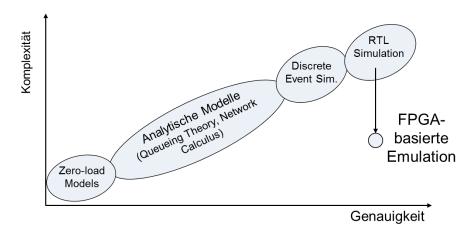

Neben den Kosten, die durch ein NoC verursacht werden, ist die Bestimmung der Performance eines NoCs wichtig. Es wurden verschiedene Techniken (z.B. Simulation auf unterschiedlichen Abstraktionsebenen, Emulation auf einem FPGA) implementiert, um die Performance von NoC zu bestimmen. Die Erweiterung der NoC-Beschreibung um weitere Bibliotheken zur Simulation mit SystemC und Colored-Petri-Nets, einer Emulation auf einem FPGA und der statischen Analyse ermöglichten einen Vergleich und eine Bewertung dieser Techniken. Die Analyse-Techniken wurden den unterschiedlichen Phasen im Entwurfsprozess von NoC zugeordnet.

Durch die Vielzahl an NoC-Parametern ist der Entwurf eines optimalen NoC sehr komplex und aufwändig. Die Erkenntnisse dieser Arbeit wurden in einer Entwurfsmethodik zusammengeführt. Dieses Spiral-Modell ermöglicht eine effiziente, automatisierte Implementierung von NoC.

Bei dem Vergleich der implementierten NoC-Komponenten mit Beispielen aus der Literatur konnte die Effizienz und Leistungsfähigkeit gezeigt werden. Für Anwendungsbeispiele aus der Literatur und zufälligen Datenverkehr konnte der Entwurfsraum für NoC erfolgreich untersucht und jeweils Pareto-optimale NoC identifiziert werden. Die Analyse des Kommunikationsverhalten eines realen Multi-Core Prozessors mit 61 Prozessorkernen und Abbildung auf den FPGA-basierten Emulator für NoC zeigen, dass die vorgestellte Methodik grundsätzlich gut für den Entwurf und die Analyse von NoC geeignet ist.

#### **Abstract**

The complexity of communication on current and future multi-core system on chip can hardly be mastered with common communication architectures such as buses or point-to-point connections. Networks-on-Chip (NoC) are a possible solution to this problem. In the context of this work a modular and parameterizable Network-on-Chip was developed. It supports a multitude of NoC parameters such as topology, routing algorithm and switching technology. The created VHDL library for NoC allows the automatic generation of NoC descriptions in VHDL.

For the investigation of the performance, area and power consumption of the modelled NoC exemplary VLSI implementations of the NoC components were created using standard cells. To reduce costs and increase performance, physically optimized core components are used in combination with standard cells. This significantly reduces the cost of NoC implementations while maintaining parameterizability. The costs for the NoC components depending on the NoC parameters are described with mathematical models. These models allow the estimation of the expected costs of a NoC already in early design phases.

Besides the costs caused by a NoC the determination of the performance of a NoC is important. There are different techniques (e.g. simulation on different abstraction levels, emulation on an FPGA) to verify this. The extension of the NoC description by further libraries for the simulation with SystemC and Colored-Petri-Nets, an emulation on an FPGA and the static analysis made a comparison and an evaluation of these techniques possible. Based on this, the analysis techniques were assigned to the different phases of the NoC design process.

Due to the large number of NoC parameters, the design of an optimal NoC is very complex and time-consuming. Therefore, the findings of this work were combined in a design methodology. This spiral model enables an efficient, automated implementation of NoC.

The comparison of the NoC components generated by the proposed method with implementations from the literature shows the efficiency of these components. For application examples from literature and for random data traffic, the design space for NoC could be successfully investigated and Pareto-optimal NoC identified. The analysis of the communication behavior of a real multi-core processor with 61 processor cores and mapping to the FPGA-based emulator for NoC shows that the presented methodology is well suited for the design and analysis of NoC.

Keywords: Emulation; Cost Estimation; Network-on-Chip; FPGA

Schlagwörter: Emulation; Kostenschätzung; Network-on-Chip; FPGA

## Inhaltsverzeichnis

| 1 | Einlei | tung                                                               | 1  |

|---|--------|--------------------------------------------------------------------|----|

| 2 | Netwo  | ork-on-Chip (NoC)                                                  | 7  |

|   | 2.1    | Einordnung in das ISO/OSI-Referenzmodell                           | 7  |

|   | 2.1.1  | Physikalische Schicht                                              | 8  |

|   | 2.1.2  | Sicherungsschicht                                                  | 9  |

|   | 2.1.3  | Vermittlungsschicht                                                | 9  |

|   | 2.1.4  | Transportschicht                                                   | 9  |

|   | 2.1.5  | Sitzungsschicht                                                    | 9  |

|   | 2.1.6  | Darstellungsschicht                                                | 9  |

|   | 2.1.7  | Anwendungsschicht                                                  | 9  |

|   | 2.2    | NoC-Parameterraum                                                  | 10 |

|   | 2.2.1  | Technologie                                                        | 10 |

|   | 2.2.2  | Implementierung der Links                                          | 11 |

|   | 2.2.3  | Maximale Datenrate                                                 | 12 |

|   | 2.2.4  | Datenfehlerschutz                                                  | 13 |

|   | 2.2.5  | Vermittlungstechnik                                                | 15 |

|   | 2.2.6  | Priorisierung von Daten und präemptiver Zugriff auf NoC-Ressourcen | 17 |

|   | 2.2.7  | Routing-Algorithmus                                                | 18 |

|   | 2.2.8  | Topologie                                                          | 20 |

|   | 2.2.9  | Verbindungsfehlerbehandlung                                        | 22 |

|   | 2.2.10 | Quality-of-Service (QoS)                                           | 22 |

|   | 2.3    | Bewertungskriterien                                                | 23 |

|   | 2.3.1  | Kosten                                                             | 24 |

|   | 2.3.2  | Performance                                                        | 24 |

|   | 2.4    | Entwurfsproblematik                                                | 27 |

| 3 | Effizi | ente, emulatorgestützte NoC-Entwurfsmethodik                       | 29 |

|   | 3.1    | Systemanalyse                                                      | 30 |

ii Inhaltsverzeichnis

|   | 3.2     | Parameterauswahl                                                                    | 30 |

|---|---------|-------------------------------------------------------------------------------------|----|

|   | 3.3     | Kostenschätzung                                                                     | 31 |

|   | 3.4     | Mapping                                                                             | 31 |

|   | 3.4.1   | Mapping-Algorithmus                                                                 | 32 |

|   | 3.4.2   | Statische Performance-Analyse                                                       | 37 |

|   | 3.5     | Automatisierte Generierung von NoC                                                  | 38 |

|   | 3.6     | Dynamische Performance-Analyse und funktionale Verifikation                         | 39 |

|   | 3.6.1   | FPGA-basierte Emulation                                                             | 39 |

|   | 3.6.1.1 | 1 Emulationsumgebung Altera-FPGAs                                                   | 40 |

|   | 3.6.1.2 | 2 Emulationsumgebung BEEcube                                                        | 42 |

|   | 3.6.2   | SystemC-basierte Simulation                                                         | 42 |

|   | 3.6.3   | Analyse mit Hilfe von Colored Petri Nets                                            | 43 |

|   | 3.6.4   | Simulation des VHDL-Codes                                                           | 45 |

|   | 3.6.5   | Quantitativer Vergleich der Analysemöglichkeiten                                    | 45 |

|   | 3.7     | VLSI-Implementierung                                                                | 51 |

|   | 3.7.1   | Standardzellenbasierte Implementierung                                              | 51 |

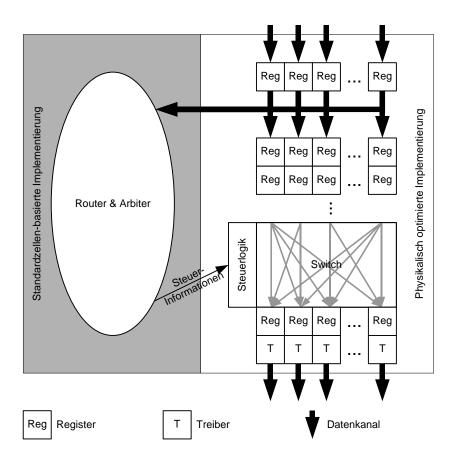

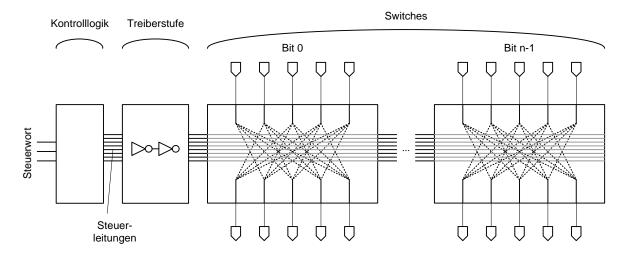

|   | 3.7.2   | Standardzellenbasierte Implementierung mit physikalisch optimierten Kernkomponenten | 52 |

|   | 3.8     | Spiral-Modell                                                                       | 54 |

| 4 | Imple   | ementierung und Bewertung ausgewählter NoC und NoC-Komponenten                      | 60 |

|   | 4.1     | Modulares und generisches NoC                                                       | 60 |

|   | 4.2     | NoC-Protokoll                                                                       | 63 |

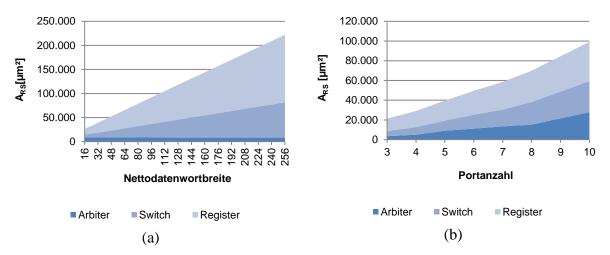

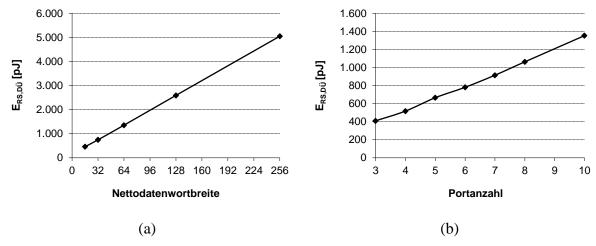

|   | 4.3     | Kosten- und Performance-Bestimmung von NoC-Komponenten                              | 66 |

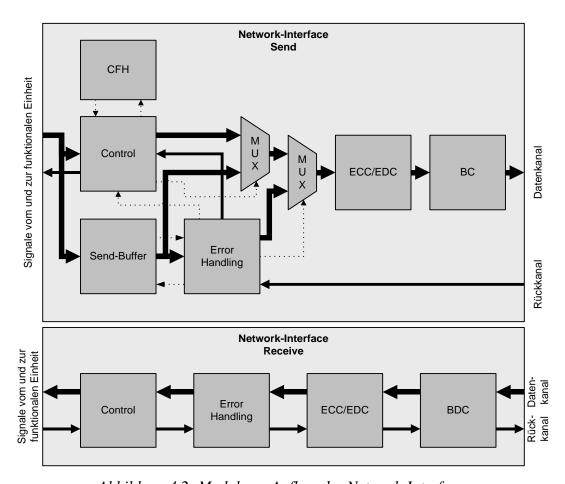

|   | 4.4     | Network-Interface.                                                                  | 67 |

|   | 4.4.1   | Vermittlungstechnik                                                                 | 71 |

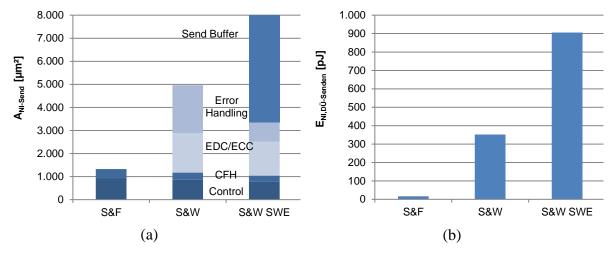

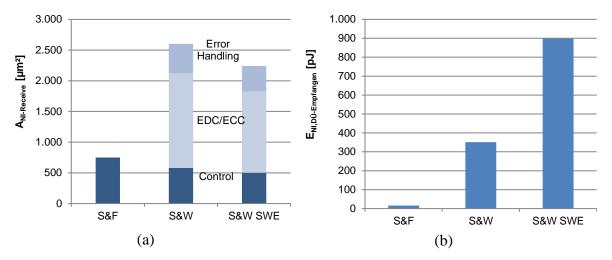

|   | 4.4.2   | Datenfehlerschutz                                                                   | 73 |

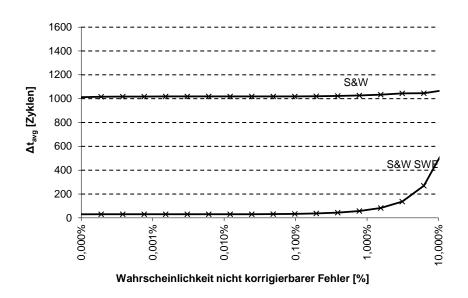

|   | 4.4.3   | Verbindungsfehlerbehandlung                                                         | 78 |

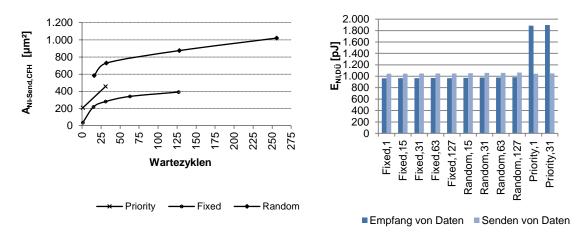

|   | 4.4.4   | Send-Buffer                                                                         | 80 |

|   | 4.5     | Routing-Switch                                                                      | 83 |

|   |         |                                                                                     |    |

|   | 4.5.1           | Vermittlungstechnik                                                                  | 86          |

|---|-----------------|--------------------------------------------------------------------------------------|-------------|

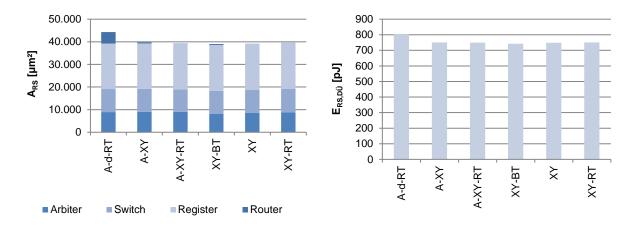

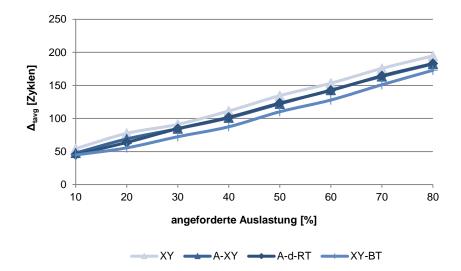

|   | 4.5.2           | Routing-Algorithmus                                                                  | 89          |

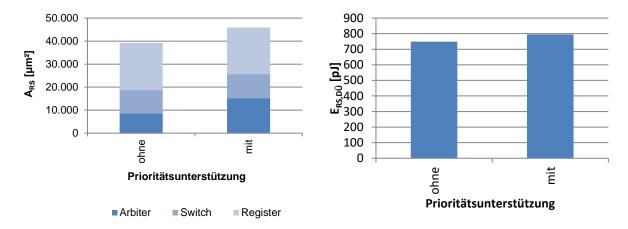

|   | 4.5.3           | Priorisierung von Verbindungen                                                       | 93          |

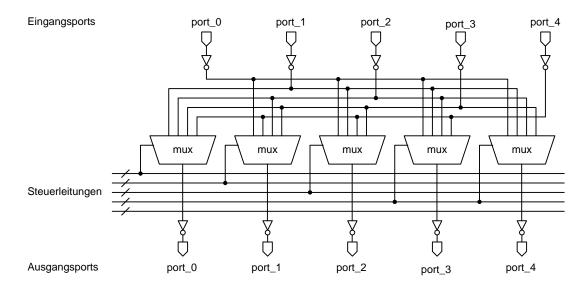

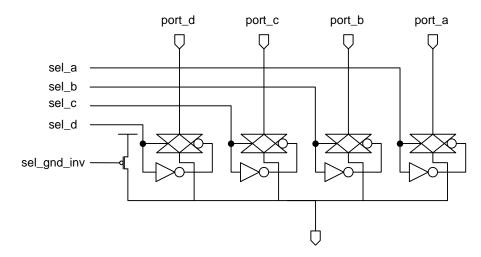

|   | 4.5.4           | Implementierung von Switch und Registern als physikalisch optimierte Kernkomponenten |             |

|   | 4.6             | Einfluss der Topologie                                                               | 98          |

|   | 4.7             | Einfluss der Vermittlungstechnik                                                     | 100         |

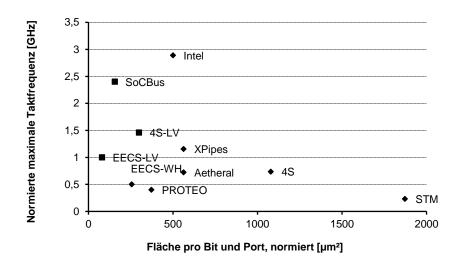

|   | 4.8             | Vergleich mit Referenzimplementierungen                                              | 100         |

|   | 4.9             | Zusammenfassende Bewertung der NoC-Parameter                                         | 103         |

| 5 | Koste           | enmodellierung von NoC                                                               | 105         |

|   | 5.1             | Modellierungsmethodik                                                                | 105         |

|   | 5.1.1           | Zeitliches Verhalten                                                                 | 105         |

|   | 5.1.2           | Fläche                                                                               | 106         |

|   | 5.1.3           | Energie und Verlustleistung                                                          | 107         |

|   | 5.2             | Bewertung der Modellierungsqualität                                                  | 109         |

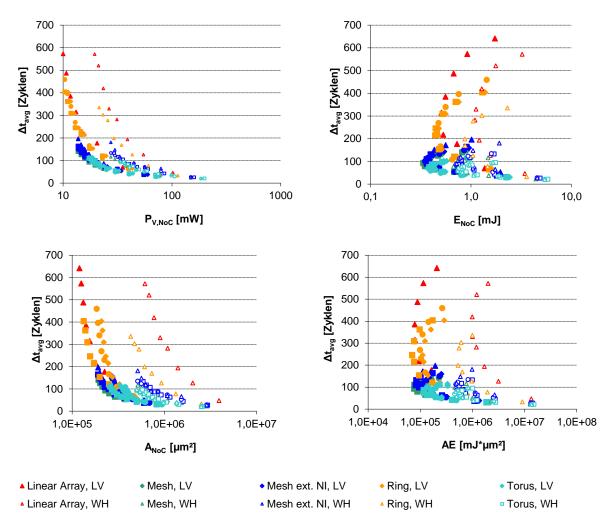

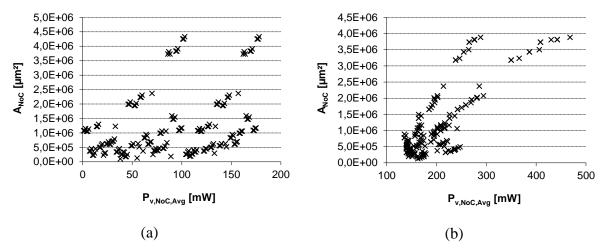

|   | 5.3             | Untersuchung des Entwurfsraumes für zufälligen Datenverkehr                          | 109         |

| 6 | Anwe            | endungsbeispiel Entwicklungsmethode                                                  | 113         |

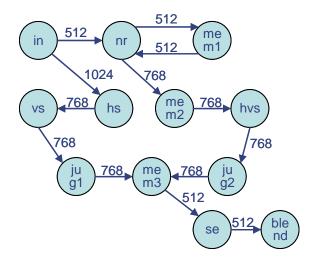

|   | 6.1<br>Signal-V | Anwendung der Entwurfsmethodik für Systeme aus dem Bereich erarbeitung               |             |

|   | 6.1.1           | Iteration 1Topologie                                                                 | 115         |

|   | 6.1.2           | Iteration 2 – Vermittlungstechnik                                                    | 117         |

|   | 6.1.3           | Iteration 3 - Taktfrequenz und Wortbreite                                            | 118         |

|   | 6.1.4           | Iteration 4 – Routing-Algorithmus                                                    | 119         |

|   | 6.1.5           | Pareto-Optimale NoC                                                                  | 120         |

|   | 6.1.6           | Einfluss der Datenblockgröße auf die Performance von NoC                             | 120         |

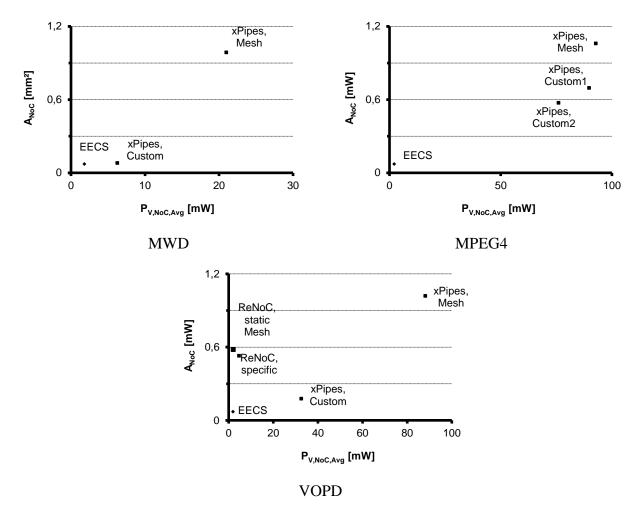

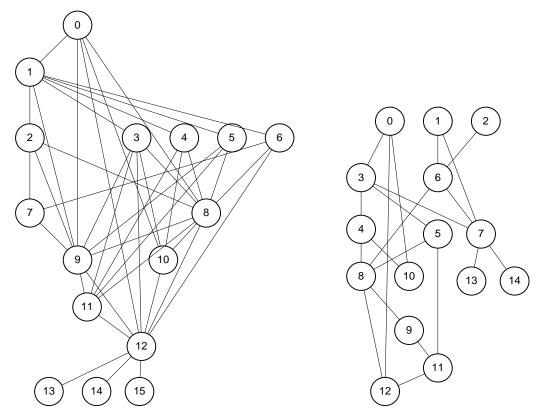

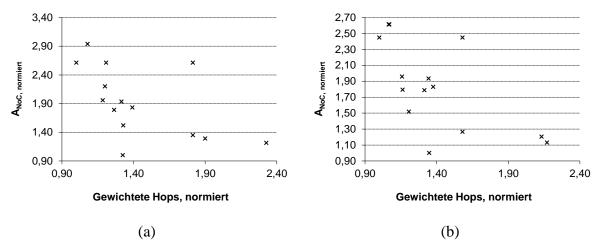

|   | 6.1.7           | Benchmark der Ergebnisse                                                             | 122         |

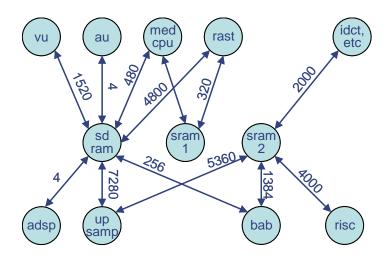

|   | 6.2<br>Kommui   | Anwendung der Entwurfsmethodik für s                                                 | ynthetische |

|   | 6.2.1           | Iteration 1 – Topologie                                                              | 126         |

iv Inhaltsverzeichnis

| 6.2.2       | $Iteration\ 2-Vermittlung stechnik,\ Routing-Algorithmus,\ Taktfrequenz\ und$ |     |

|-------------|-------------------------------------------------------------------------------|-----|

|             | Wortbreite                                                                    | 128 |

| 6.3         | Bewertung                                                                     | 131 |

| 7 Anwe      | endungsbeispiel HOG Algorithmus auf dem Xeon Phi Multicore Prozessor          | 133 |

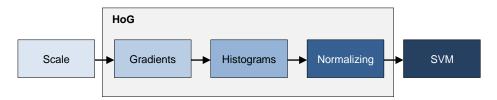

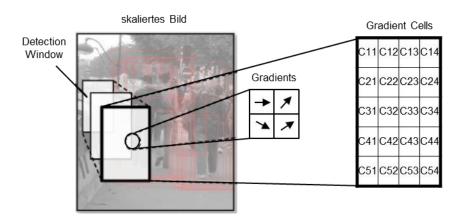

| 7.1         | Beschreibung HOG-Algorithmus                                                  | 134 |

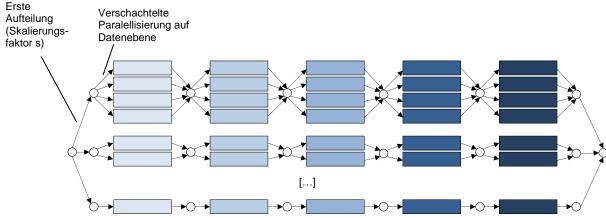

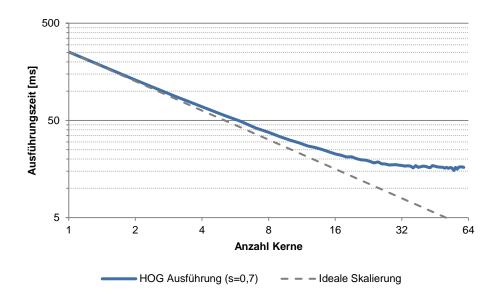

| 7.1.1       | Parallele Implementierung                                                     | 135 |

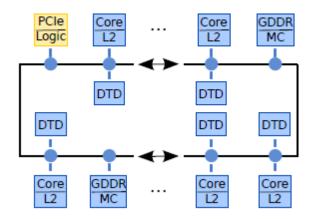

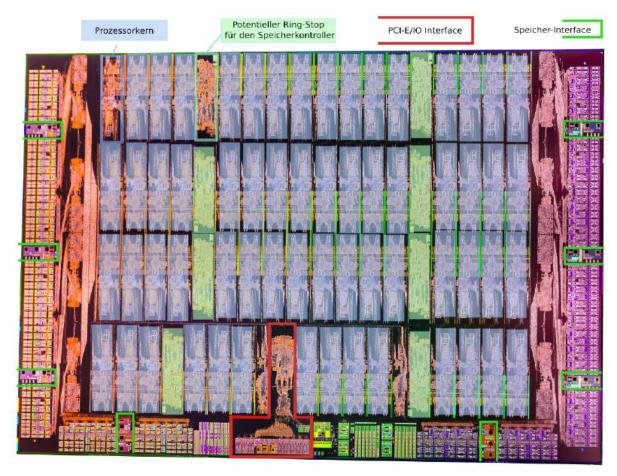

| 7.2         | Beschreibung Xeon Phi                                                         | 136 |

| 7.3         | Hardware Modell                                                               | 137 |

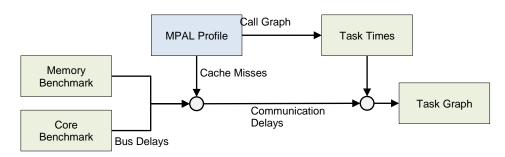

| 7.4         | Profiling-Ergebnisse und Task-Graph                                           | 138 |

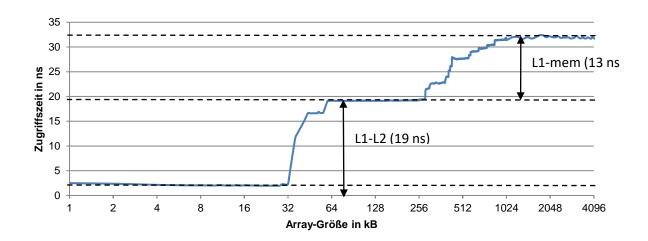

| 7.4.1       | Memory Delay Benchmark                                                        | 140 |

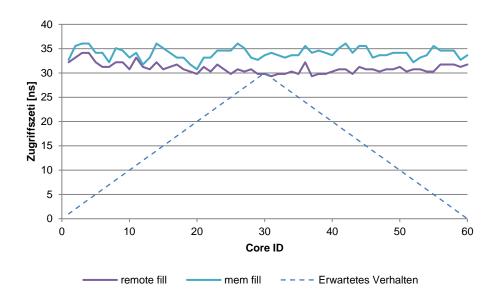

| 7.4.2       | Core Communication Benchmark                                                  | 141 |

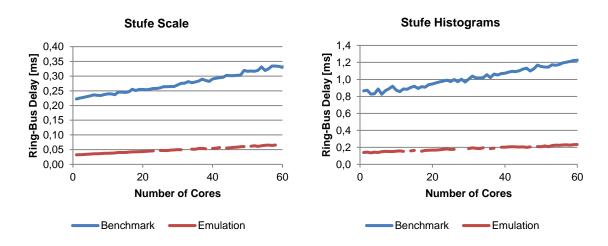

| 7.5         | NoC-Emulation                                                                 | 142 |

| 8 Zusai     | mmenfassung                                                                   | 145 |

| Wissenscha  | aftlicher Werdegang                                                           | 149 |

| Publikation | sverzeichnis                                                                  | 151 |

| Literaturve | rzeichnis                                                                     | 153 |

| Anhang A    | Unterstützte NoC-Parameter                                                    | 163 |

| Anhang B    | Abkürzungen und Formelzeichen                                                 | 165 |

| Anhang C    | Beschreibung des künstlichen Datenverkehrs                                    | 171 |

| Anhang D    | Funktionen zur Modellierung der Fläche und Verlustleistung                    | 173 |

## 1 Einleitung

Aktuelle und zukünftige Systeme der digitalen Signalverarbeitung, wie mobile Telekommunikations- oder Multimedia-Anwendungen, haben einen stetig wachsenden Bedarf an Rechenleistung. Gleichzeitig sollen Systeme, auf denen diese Anwendungen ausgeführt werden, eine möglichst geringe Verlustleistung verursachen. Eine weitere Anforderung ist eine kurze Entwicklungszeit der benötigten Hard- und Software, sowie eine möglichst große Flexibilität. Dies bedeutet, dass Anwendungen dem System hinzugefügt oder vom System entfernt werden können.

Durch die Fortschritte der VLSI-Technologie lassen sich immer kleinere Strukturen auf einem Chip realisieren. Bei gleichbleibender Chipfläche führt dieser Trend zu immer mehr Transistoren auf einem Chip [1], welche die Realisierung so genannter Systems-on-Chip (SoC) ermöglichen. SoC integrieren komplette Hardwaresysteme auf einem einzelnen Chip, der aus mehreren funktionalen Einheiten (Prozessorkerne, DSP-Kerne, Speicher, eingebettete FPGAs (eFPGA) etc.) bestehen kann. Die funktionalen Einheiten eines SoC können aus Architekturblöcken (homogene SoC) oder unterschiedlichen identischen aus Architekturblöcken bestehen (heterogene SoC) [2]. Damit sind SoC eine Möglichkeit, um die oben genannten Anforderungen an Systeme der digitalen Signalverarbeitung zu erfüllen. Aktuell werden SoC mit bis zu 64 funktionalen Einheiten kommerziell gefertigt.

Die steigende Komplexität dieser Chips erforderte neue Design-Techniken. Dies bezieht sich sowohl auf die Entwicklung der Hardware, als auch auf die Entwicklung von Software für SoC [3]. Für die Hardware-Entwicklung wird ein modularer Aufbau des SoC angestrebt, bei dem einzelne funktionale Einheiten über spezifizierte Schnittstellen verfügen und so an einer anderen Stelle im SoC oder auch in einem anderen SoC wieder eingesetzt werden können (IP-Reuse). Eine weitere Maßnahme, die sowohl den Hardware- wie auch den Software-Entwurf eines SoC betrifft ist die Entkopplung von Kommunikation und Funktion, wie sie bereits im ISO/OSI-Referenzmodell für Computersysteme vorgestellt wurde [4]. Durch diese Trennung können funktionale Einheiten und die Kommunikationsstruktur eines SoC parallel entwickelt werden. Darüber hinaus können funktionale Einheiten, ohne genaue Kenntnis der Kommunikationsstruktur, über eine spezifizierte Schnittstelle Daten austauschen.

An die Kommunikationsstruktur werden von den Systemen, die auf ein SoC abgebildet werden, hohe Anforderungen gestellt. Die Kommunikationsstruktur soll einen hohen Datendurchsatz bei gleichzeitig geringer Latenz ermöglichen. Zusätzlich können, je nach Systemanforderungen, weitere Quality-of-Service-Anforderungen (QoS), wie beispielsweise garantierte Durchsatzraten oder eine maximal zulässige Datenfehlerrate gefordert werden. Eine Kommunikationsstruktur sollte darüber hinaus flexibel und skalierbar sein in dem sie für unterschiedliche Anwendungen und Systeme geeignet [5] und auch für zukünftige, größere

2 1 Einleitung

SoC zu verwenden ist. Dies führt zu geringeren Entwicklungszeiten und geringerem Entwicklungsaufwand [6]. Die vorgenannten Anforderungen sollen bei möglichst geringen Kosten erfüllt werden, die sich auf einem SoC beispielsweise in der Fläche und/oder der Verlustleistung des SoC ausdrücken lassen.

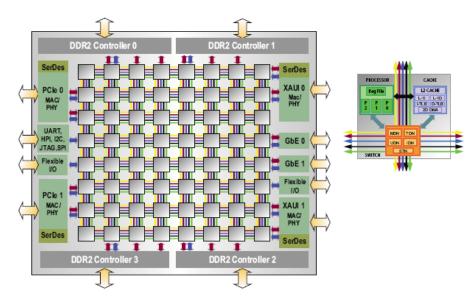

Abbildung 1.1: Exemplarisches homogenes SoC mit 64 Prozessorkernen [7]

Ein weiteres Problem, was insbesondere für zukünftige CMOS-Prozesse und entsprechend kleine Strukturgrößen an Relevanz gewinnt, ist die relative Verzögerung, die durch eine Verbindungsleitung verursacht wird. Diese steigt bei Technologien mit kleineren Strukturgrößen für globale Leitungen weiter an. Verursacht wird dieser Effekt durch die trotz Strukturverkleinerung unveränderte Länge der globalen Leitungen bei gleichzeitig steigendem Widerstand der Leitung.

Die Länge der globalen bleibt häufig konstant, da durch die sinkende Strukturgröße die Siliziumfläche der Chips nicht kleiner wird, sondern mehr Transistoren auf derselben Siliziumfläche verwendet werden. Durch zusätzliche Maßnahmen (Repeater, Booster) kann dieser Anstieg reduziert, jedoch nicht komplett kompensiert werden [8]. Im Gegensatz dazu sinkt die Verzögerung, die durch logische Gatter verursacht wird. Für zukünftige Technologien wird bei langen, globalen Leitungen die Übertragungsgeschwindigkeit in den logischen Gattern bestimmt. Daher sind möglichst kurze Leitungen für die globale Kommunikation mit hohen Datenraten wünschenswert.

Klassische Kommunikationsarchitekturen, wie zum Beispiel Busse oder Punkt-zu-Punkt-Verbindungen können diese Anforderungen nicht erfüllen [9]. Insbesondere sind diese Strukturen nicht beliebig skalierbar. Neben segmentierten oder hierarchischen Bus-Systemen [10] sind Network-on-Chip (NoC) eine häufig vorgeschlagene Lösung, um diesen Anforderungen an die Kommunikationsstruktur gerecht zu werden [11,12,13].

1 Einleitung 3

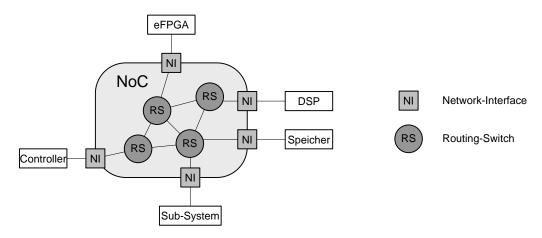

Abbildung 1.2: Exemplarisches NoC das funktionale Einheiten (eFPGA, DSP, Kontroller, Speicher und Sub-System) miteinander verbindet.

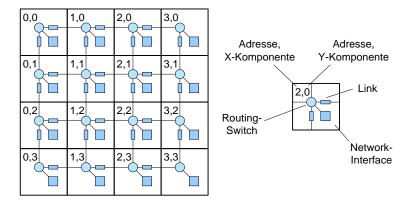

NoC übertragen Daten von einer funktionalen Einheit zu einer anderen, wobei die Daten zunächst von einer funktionalen Einheit an ein sogenanntes Network-Interface (NI) übergeben werden. Anschließend werden die Daten von diesem Network-Interface über einen oder auch mehrere Routing-Switches (RS) an die empfangende funktionale Einheit übertragen, die über ein Network-Interface an das NoC angeschlossen ist (vgl. Abbildung 1.2).

Die Eigenschaften und Kosten von NoC werden durch eine Vielzahl an NoC-spezifischen Parametern bestimmt. Diese reichen von der Ausprägung der Verbindungsleitungen über Routing-Algorithmen bis hin zur Vermittlungstechnik und Topologie des NoC und spannen daher einen großen Entwurfsraum auf. Die Achsen dieses Entwurfsraumes bilden zum einen durch das NoC verursachte Kosten, aber auch Performance-Maße, die sich gut quantitativ erfassen lassen. Die Flexibilität, die Unterstützung von QoS-Aspekten oder auch der Entwurfsaufwand und die Entwurfszeit stellen weitere Dimensionen des Entwurfsraumes dar, die jedoch schwierig zu quantifizieren sind.

Da verschiedene Systeme unterschiedliche Anforderungen an die Kommunikationsstruktur stellen, kann und muss ein NoC an die jeweiligen Anforderungen angepasst werden [14]. Es wird dazu die Kombination NoC-spezifischer Parameter benötigt, welche die Anforderungen bei möglichst geringen Kosten erfüllt. Zur Identifizierung dieser Parameterkombination ist es notwendig, den Entwurfsraum für NoC zu untersuchen.

Für eine systematische Untersuchung des Entwurfsraumes eines gegebenen Systems und gegebenen funktionalen Einheiten wird eine Entwurfsmethodik benötigt, die zum Einen den Entwurfsaufwand minimiert und zum Anderen eine Bewertung des NoC bezüglich Kosten und Performance ermöglicht.

Voraussetzung für einen geringen Entwurfsaufwand ist ein modulares und generisches NoC, bei dem einzelne Parameter mit geringem Aufwand variiert werden können. Die 4 1 Einleitung

Beschreibung eines solchen NoC sollte möglichst abstrakt erfolgen. Mit Hilfe dieser abstrakten Beschreibung ist es dann möglich eine NoC-Implementierung zu generieren.

Bei der Performance-Bewertung wird überprüft, ob die durch das System definierten Kommunikationsanforderungen erfüllt werden. Diese Bewertung des NoC erfolgt auf unterschiedlichen Abstraktionsebenen. Zu einem frühen Zeitpunkt im NoC-Entwurf erfolgt die Bewertung zunächst auf einer hohen Abstraktionseben, die eine erste Kosten- und Performance-Schätzung mit geringem Aufwand ermöglicht. Die damit verbundene geringere Genauigkeit ist in diesem Entwurfsstadium akzeptabel. Am Ende des Entwurfsprozesses ist hingegen eine genaue Bestimmung der Kosten sowie der Performance des NoC notwendig. Um die Performance eines NoCs für ein System exakt bestimmen zu können, werden Testbenches benötigt, die den Datenverkehr realer Anwendungen abbilden.

Im Rahmen dieser Arbeit wurde eine solche Entwurfsmethodik für NoC entwickelt. Diese Entwurfsmethodik ermöglicht es auch Entwicklern mit wenig Erfahrung im Entwerfen und Dimensionieren von NoC, den Entwurfsraum für NoC systematisch zu untersuchen. Damit lässt sich für eine gegebene Applikation bzw. Klasse von Applikationen und ein gegebenes SoC ein NoC identifizieren, welches für diese Anforderungen (Pareto-)optimal ist.

Das Ergebnis dieser Entwurfsmethodik sind die für die Aufgabenstellung Pareto-optimalen NoC. Diese werden durch die NoC-Parameter und den daraus generierten VHDL-Code beschrieben. Für die Generierung wird eine VHDL-Bibliothek benötigt, die für diese Arbeit erstellt wurde. Die Parameter, die für ein NoC vorgegeben werden können, sind in Anhang A angegeben und umfassen unter anderem die Topologie, Vermittlungstechnik, Datenwortbreite und Routing-Algorithmus. Neben der Beschreibung in VHDL werden die Elemente des NoC (Network-Interfaces und Routing-Switches) mit Hilfe von Standard-Zellen und physikalisch optimierten Kernkomponenten synthetisiert.

Eine Bewertung von NoC hinsichtlich der Performance und Kosten auf unterschiedlichen Abstraktionsebenen ist elementarer Bestandteile dieser Methodik. Um die Performancebewertung durchführen zu können, wurden verschiedene Analysemethoden (statischen Analyse, Simulation mit Petri-Netzen, SystemC und VHDL sowie FPGA-basierte Emulation) für NoC auf implementiert, analysiert und bewertet.

Die Bestimmung der Kosten in einer frühen Entwurfsphase basiert auf mathematischen Kostenmodellen für die einzelnen NoC-Komponenten. Diese wurde in umfangreichen Untersuchungen für die in Anhang A angegeben Parameter erstellt. Die Modelle unterstützen eine Implementierung mit Standardzellen sowie mit Standardzellen in Kombination mit physikalisch optimierten Kernkomponenten. Die Kosten eines NoC werden durch die benötigte Fläche und die Verlustleistung beschrieben.

1 Einleitung 5

Diese Entwurfsmethode wurde automatisiert, d.h. die einzelnen Phasen werden automatisch durchgeführt (inkl. Emulation und Synthese). Durch eine manuelle Optimierung kann eine weitere Reduzierung der Kosten bzw. Steigerung der Performance erzielt werden.

Die in dieser Arbeit vorgeschlagene, automatisierte Methodik unterstützt symmetrische NoC-Topologien. Mit Hilfe der VHDL-Bibliothek lassen sich auch asymmetrische und hierarchische Topologien abbilden. Diese werden nicht in der automatischen Entwurfsmethodik berücksichtigt. Durch den modularen Aufbau des NoC und der NoC-Komponenten kann die VHDL Beschreibung um bisher nicht unterstützte Parameter und Funktionen erweitert werden.

Für die Kostenmodellierung und Synthese wird in der Entwurfsmethode nur eine Technologie verwendet. Für eine Übertragung der Methode auf weitere Technologien müssen die Kostenmodelle überarbeitet werden. In erster Näherung können diese skaliert werden, für eine höhere Genauigkeit müssen die Modelle jedoch neu erstellt werden. Die physikalisch optimierten Kernkomponenten sind ebenfalls technologiespezifisch und müssen dementsprechend bei einem Wechsel der Technologie neu erstellt werden.

Diese Arbeit ist wie folgt gegliedert: Zunächst wird eine Übersicht über den Stand der Forschung bei NoC gegeben. In Kapitel 3 wird die erarbeitete, emulatorgestützte Entwurfsmethodik vorgestellt. Dabei wird insbesondere auf die verschiedenen Möglichkeiten der Performance-Analyse eingegangen. Das modulare und generische NoC, auf dem diese Entwurfsmethodik basiert, wird in Kapitel 4 vorgestellt. Weiterhin wird anhand exemplarischer Implementierungen der Einfluss verschiedener NoC-spezifischer Parameter auf die Kosten und Performance eines NoCs quantitativ untersucht. Im Anschluss werden Implementierungen des Routing-Switches mit Referenz-Implementierungen aus der Literatur verglichen.

Kapitel 5 beschreibt die Modellierungsmethodik, anhand derer Modellfunktionen für die von NoC verursachten Kosten bestimmt wurden. Mit Hilfe der in diesem Kapitel angegebenen Modellfunktionen wird der Entwurfsraum bezüglich der Verlustleistung, Siliziumfläche und Performance für zufälligen Datenverkehr aufgespannt. Im Kapitel 6 werden anwendungsspezifisch optimierte NoC mit Hilfe der zuvor beschriebenen Entwurfsmethodik für reale Systeme aus dem Bereich der Video-Signal-Verarbeitung erzeugt und anschließend mit optimierten NoC aus der Literatur verglichen. Weiterhin wird die Leistungsfähigkeit der Methodik an exemplarischen, synthetischen Kommunikationsanforderungen demonstriert. Die Anwendung der FPGA-basierten Emulation eines NoC für ein reales Beispiel (Histograms of Oriented Gradients Algorithmus für Fahrassistenz-Systeme) und der Vergleich mit einer Implementierung auf einem Mehrkern-Prozessor ist in Kapitel 7 beschrieben. Die Arbeit schließt mit einer Zusammenfassung.

## 2 Network-on-Chip (NoC)

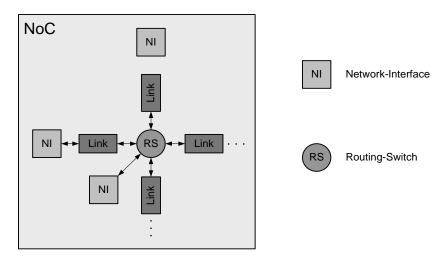

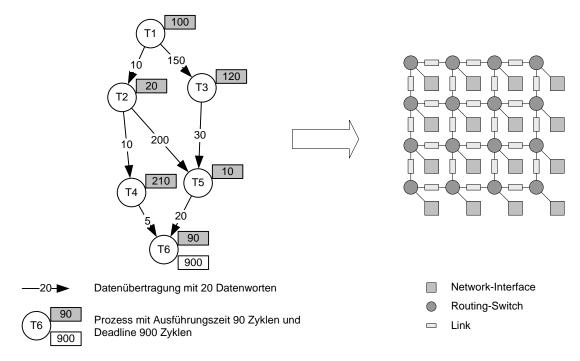

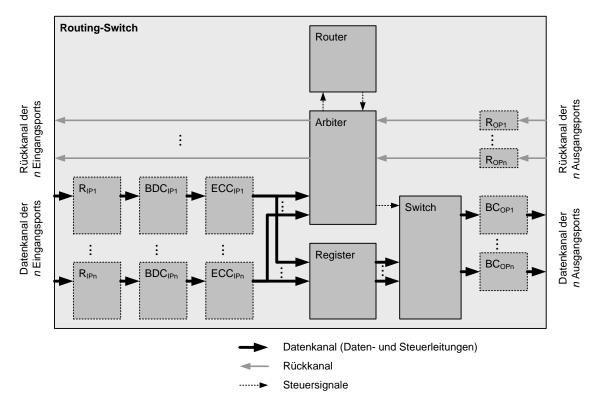

Networks-on-Chip ermöglichen eine skalierbare, flexible Kommunikation auf einem Chip und werden aus unterschiedlichen Modulen aufgebaut: Network-Interfaces, welche die Anbindung an eine funktionale Einheit vornehmen, Routing-Switches, die Daten durch das NoC verteilen und Links, welche die physikalischen Verbindungen in einem NoC darstellen. Das NoC, wie auch die einzelnen NoC-Komponenten, besitzen dabei eine Vielzahl von Parametern.

Abbildung 2.1: Allgemeiner Aufbau von NoC

Zur Strukturierung dieser Vielzahl von Parametern lassen sich die einzelnen NoC-Komponenten und deren Funktionen in das ISO/OSI-Referenzmodell einordnen [4,13]. Parameter, die einen signifikanten Einfluss auf die Leistungsfähigkeit bzw. die durch ein NoC verursachten Kosten haben, werden im Verlauf des Kapitels erläutert. Ein weiteres Unterkapitel behandelt Bewertungskriterien für NoC. Ausgehend von diesen Betrachtungen wird auf die Entwurfsproblematik von NoC eingegangen.

### 2.1 Einordnung in das ISO/OSI-Referenzmodell

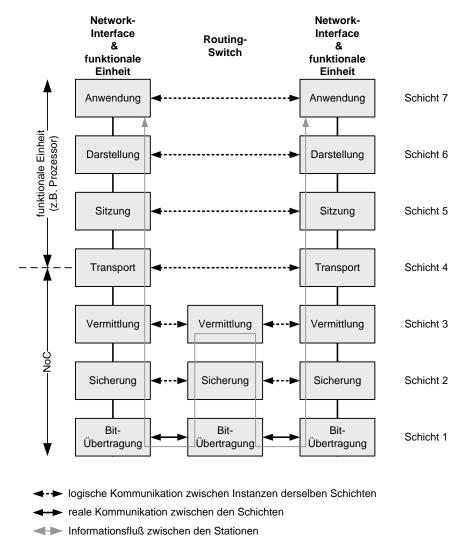

Das ISO/OSI-Referenzmodell dient dazu, den Informationsaustausch zwischen verteilten Teilnehmern zu schematisieren und in einzelne, präzise definierte Schichten (Layer) zu unterteilen. Jede dieser Schichten bietet der nächsthöheren Schicht Dienste (Services) an. In Abbildung 2.2 ist die Kommunikation zwischen zwei Anwendungen, die in verschiedenen funktionalen Einheiten unterteilt werden, mittels des ISO/OSI-Referenzmodells beschrieben. Die Kommunikation erfolgt dabei über ein NoC unter Zuhilfenahme eines Routing-Switches. Die logische Informationsübertragung (gestrichelte Pfeile) erfolgt immer zwischen zwei Instanzen derselben Schicht über Protokolle. Dazu stehen der übertragenden Schicht lediglich

die Dienste der nächst niedrigeren Schicht zur Verfügung. Der Informationsfluss (grauer Pfeil) erfolgt unter Verwendung der darunter liegenden Schichten.

Es wird zwischen den netzabhängigen Schichten 1-3 und den netzunabhängigen Schichten 5-7 unterschieden. Die Schicht 4 stellt das Bindeglied zwischen den netzabhängigen und den netzunabhängigen Schichten dar. Dieses allgemeine Modell wird im Folgenden für NoC angepasst.

Um den Parameterraum von NoC zu strukturieren, wurden zunächst Dienste und die dazugehörigen Parameter den einzelnen netzabhängigen Schichten zugeordnet. Die Funktionen der netzunabhängigen Schichten werden im Folgenden skizziert.

Abbildung 2.2: ISO/OSI-Referenzmodell

#### 2.1.1 Physikalische Schicht

Die Bitübertragungsschicht, oder auch physikalische Schicht, ermöglicht die Übertragung von Bits über ein Kommunikationsmedium. Hier werden die funktionalen und elektrischen

Schnittstellen zum Übertragungsmedium definiert, wie z.B. die Buscodierung, die Taktfrequenz oder die Wortbreite der zu übertragenden Daten.

#### 2.1.2 Sicherungsschicht

Die Aufgaben der Sicherungsschicht beinhalten sowohl Funktionen zum Verbindungsaufbau, das Zugriffsprotokoll auf das Medium sowie Maßnahmen zum Fehlerschutz.

Im Detail sind dies für NoC die Vermittlungstechnik, z.B. Leitungsvermittlung oder Paketvermittlung, der Datenfehlerschutz sowie weitere Dienste zur Unterstützung von QoS-Diensten höherer Schichten.

#### 2.1.3 Vermittlungsschicht

Die Vermittlungsschicht ist für das Einrichten, den Betrieb und das Auflösen von Netzwerkverbindungen verantwortlich. Eine wichtige Aufgabe ist hier das Routing von Daten über das NoC.

#### 2.1.4 Transportschicht

In der Transportschicht wird der End to End-Datentransport realisiert, d.h. es werden Datentransfers initiiert und beendet und somit der Datenfluss gesteuert. Die Fehlerbehandlung, die Realisierung von QoS und die Zuordnung von NoC-Adresse und virtueller Adresse finden in dieser Schicht statt.

#### 2.1.5 Sitzungsschicht

Die Sitzungsschicht sorgt für die Prozesskommunikation zwischen zwei Systemen. In dieser Schicht werden Dienste für einen organisierten und synchronisierten Datenaustausch zur Verfügung gestellt.

#### 2.1.6 Darstellungsschicht

Die Darstellungsschicht übersetzt Daten von einer systemabhängigen Darstellung in eine systemunabhängige Darstellungsform. Dabei können auch Dienste wie Verschlüsselung und Datenkompression verwendet werden.

#### 2.1.7 Anwendungsschicht

Die Anwendungsschicht oder auch Verarbeitungsschicht ist die oberste der sieben hierarchischen Schichten und stellt der Anwendungssoftware eine Vielzahl von Funktionalitäten zur Verfügung. Die eigentliche Anwendung liegt über der Schicht 7 und wird vom ISO/OSI-Referenzmodell nicht erfasst.

#### 2.2 NoC-Parameterraum

Den im vorherigen Abschnitt vorgestellten Schichten des ISO/OSI-Referenzmodells lassen sich NoC-spezifische Parameter zuordnen, die im weiteren Kapitel genauer erläutert werden. Die NoC-spezifischen Parameter beeinflussen nicht immer die Implementierung aller NoC-Komponenten. So hat beispielsweise der verwendete Routing-Algorithmus keinen Einfluss auf die Implementierung eines Network-Interfaces, da die Logik des Routing-Algorithmus komplett in den Routing-Switches implementiert ist.

#### 2.2.1 Technologie

Ein wichtiger Parameter, der starken Einfluss auf die Leistungsfähigkeit und die durch NoC verursachten Kosten hat, ist die verwendete Technologie. Aktuell werden SoC, wie auch die zur Kommunikation verwendeten NoC in CMOS-Technologie gefertigt. Die Strukturgröße der verwendeten Technologien sinkt dabei stetig [15]. Die Technologie beeinflusst zum einen die Implementierung der Routing-Switches und Network-Interfaces, und damit insbesondere die erreichbare Taktfrequenz, die benötigte Fläche und die Verlustleistung. Zum anderen sind die Eigenschaften der elektrischen Verbindungsleitungen stark von der Technologie und der Strukturgröße abhängig.

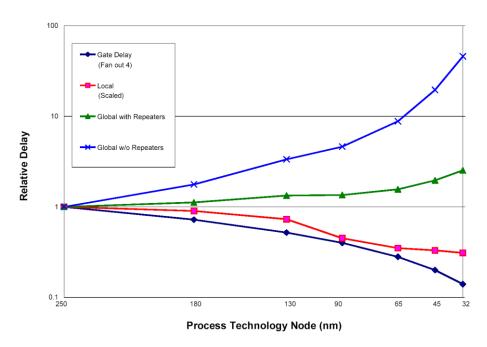

Abbildung 2.3: Relative Verzögerung auf Verbindungsleitungen für verschiedene Strukturgrößen [15]

Sinkende Strukturgrößen führen zu einer größeren Verzögerung auf den Verbindungsleitungen (vgl. [8] und Kapitel 1). Andererseits wird die Verzögerung durch logische Gatter (Gate Delay) immer geringer, wie in Abbildung 2.3 dargestellt ist. Daher wird

in Zukunft im Deep-Submicron-Bereich nicht mehr die Verzögerung durch logische Gatter, sondern die Verzögerung durch Verbindungsleitungen die Leistungsfähigkeit eines SoC bestimmen [16].

#### 2.2.2 Implementierung der Links

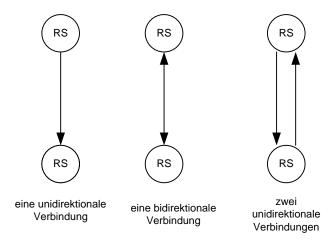

Links verbinden NoC-Komponenten (Routing-Switches und Network-Interfaces) miteinander. Die Konnektivität der Links kann variiert werden. So kann ein Link, wie in Abbildung 2.4 abgebildet, aus ein oder zwei unidirektionalen Verbindungen bestehen, oder auch aus einer bidirektionalen Verbindung.

Abbildung 2.4: Konnektivität von Links

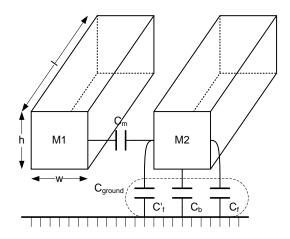

Die Verbindungen sind aus einem Satz von Verbindungsleistungen aufgebaut. Diese physikalischen Verbindungsleitungen besitzen verschiedene Parameter. Die Dimensionierung der für eine Verbindungsleitung benötigten Treiber ist abhängig von der Kapazität und dem elektrischen Widerstand der Verbindungsleitung. Diese Parameter werden zum einen durch die Länge der Verbindungsleitungen und deren Dimensionierung (Breite und Höhe der Leitung) wie auch durch den Abstand zu benachbarten Leitungen bestimmt. Die Kapazität  $C_{total}$  setzt sich dabei aus der Kapazität gegenüber dem Null-Potenzial  $C_{ground}$  und den Kapazitäten zu benachbarten Metallleitungen  $C_m$  zusammen (Abbildung 2.5). Die Kapazität  $C_m$  beeinflusst dabei nicht nur die die Kapazität der Leitung, sondern ist auch ein Maß für das Übersprechen zwischen den Leitungen (Cross-Talk). Je größer die Kapazität  $C_m$  ist, desto stärker beeinflussen sich die beiden Leitungen [18].

Wenn das Übersprechen zwischen den Leitungen minimiert wird, wird gleichzeitig die Verlässlichkeit der Datenübertragung erhöht. Dazu kann zum einen der Abstand zwischen den Leitungen erhöht, oder die Leitungen elektrisch entkoppelt werden. Die Entkopplung zweier Leitungen kann durch eine Leitung, die konstant auf dem Null-Potenzial liegt, erfolgen. Beide Maßnahmen resultieren jedoch in einem höheren Flächenbedarf für die Verbindungsleitungen.

Insbesondere bei langen Verbindungsleitungen und hohen Taktfrequenzen können zur Einhaltung der Timing-Vorgaben weitere Maßnahmen wie beispielsweise Repeater oder regenerative Booster eingesetzte werden [19]. Häufig werden auch Register vorgeschlagen, um so die Taktfrequenz des NoC weiter zu erhöhen [20].

Abbildung 2.5: Einfaches Kapazitätsmodell [18]

#### 2.2.3 Maximale Datenrate

Die maximale Datenrate kann auf eine einzelne NoC-Komponente oder auf das gesamte NoC bezogen sein. In beiden Fällen muss zwischen der Brutto- und Nettodatenrate unterschieden werden. Die Bruttodatenrate misst dabei alle über das NoC bzw. den Link übertragenen Daten pro Zeiteinheit, inklusive aller Kontrolldaten und hinzugefügter Redundanz, z.B. durch Fehlerschutzcodierung. Bei der Nettodatenrate werden nur die übertragenen Nutzdaten pro Zeiteinheit gezählt. Die maximal zu erreichende Nettodatenrate ist rechnerisch nicht exakt zu bestimmen. Sie hängt unter anderem von den hinzugefügten Kontrollinformationen, fehlgeschlagenen Verbindungsaufbauten bzw. Datenübertragungen, von der Auslastung des NoC und weiteren Faktoren ab. Zur Bestimmung der Nettodatenrate ist eine Simulation bzw. Emulation des NoC für einen definierten Datenverkehr notwendig. Dies ist in Kapitel 3.6 beschrieben.

Die maximale Bruttodatenrate ( $r_{L,brutto,max}$ ) eines Links bestimmt sich hingegen aus der Bruttodatenwortbreite (w') eines Links multipliziert mit der maximalen Taktfrequenz ( $f_{max}$ ), mit der die Datenworte über den Link gesendet werden. Die maximale Taktfrequenz wird neben der verwendeten Technologie auch von der Implementierung und Dimensionierung der NoC-Komponenten begrenzt.

$$r_{\text{L,brutto,max}} = f_{\text{max}} \cdot w' \tag{2.1}$$

Um die maximale Bruttodatenrate des gesamten NoCs zu bestimmen, wird davon ausgegangen, dass von jedem Network-Interface des NoC gleichzeitig mit der maximal möglichen Datenrate, der maximalen Bruttodatenrate einer NoC-Komponente, gesendet wird.

$$r_{\text{brutto,max}} = \sum_{i=1}^{\text{NI}} r_{\text{L,brutto,max}}$$

(2.2)

Die maximale Bruttodatenrate ist dabei jedoch ein Wert, der in der Regel nicht erreicht wird. Er wird zum einen durch zusätzlichen Aufwand für Kontrolldaten und zum anderen durch Überlastung einzelner NoC-Komponenten beschränkt.

#### 2.2.4 Datenfehlerschutz

Durch die immer weitere Technologieskalierung werden Verbindungsleitungen immer sensitiver für Fehler [15]. Diese Fehler lassen sich in die Fehlerklassen transiente Fehler, permanente Fehler und alterungsbedingte Fehler aufteilen. Transiente Fehler werden beispielsweise durch Übersprechen zwischen Verbindungsleitungen, Rauschen der Versorgungsspannung oder durch Leckströme initiiertes Rauschen hervorgerufen. Permanente Fehler können durch Prozessvariationen verursacht werden. Durch Elektromigration und den Hot Carrier-Effekt werden Fehler durch Alterung verursacht [18]. Den größten Einfluss bei NoC haben transiente Fehler durch Übersprechen zwischen Verbindungsleitungen [21].

Um diese Fehler auf den Verbindungsleitungen zu vermeiden oder zu korrigieren, wurden in der Literatur verschiedene Verfahren vorgestellt. Sie lassen sich grundsätzlich in die Fehlervermeidung, Fehlererkennung und -korrektur sowie Fehlerbehandlung unterteilen.

Zur Vermeidung von Fehlern durch Übersprechen werden beispielsweise spezielle Formen von Datencodierung verwendet. Diese nutzen Datenmuster auf den Verbindungsleitungen welche ein starkes Übersprechen vermeiden [22, 23].

| Abkürzung | Funktion                  | Fehlerschutzcode      |

|-----------|---------------------------|-----------------------|

| SED       | Einzelfehlererkennung     | Parity Code           |

| SEC       | Einzelfehlerkorrektur     | Hamming Code          |

| DED       | Doppelfehlererkennung     | Hamming Code          |

| SEC/DED   | Einzelfehlerkorrektur und | Enhanced Hamming Code |

|           | Doppelfehlererkennung     |                       |

| TED       | Dreifachfehlererkennung   | Enhanced Hamming Code |

Tabelle 2.1: Übersicht Fehlerschutzcodes

Die Fehlererkennung und -korrektur wird mit Hilfe von Codes ermöglicht, die den Daten Redundanz hinzufügen. Durch das Hinzufügen von Redundanz lassen sich so einzelne oder auch mehrere Fehler erkennen und ggf. korrigieren. Die Anzahl der erkennbaren und korrigierbaren Fehler hängt von dem verwendeten Code ab. Bei NoC werden vielfach Parity und Hamming Codes verwendet [24, 25]. Zur Erkennung von 1-, 2- oder 3-Bitfehlern kann

ein Parity, Hamming bzw. Enhanced Hamming Code verwendet werden. Zur Fehlerkorrektur eignet sich der Hamming Code bei 1-Bitfehlern und der Enhanced Hamming Code bei 2-Bitfehlern, vgl. Tabelle 2.1. Die Anzahl der zusätzlich zu übertragenden Bits ist, sowohl vom Code als auch von der Wortbreite abhängig. Dies ist in Tabelle 2.2 dargestellt.

Die Fehlerschutzcodierung erfolgt im sendenden Network-Interface. Die Fehlererkennung und -korrektur kann sowohl im empfangenden Network-Interface wie auch in den Routing-Switches erfolgen.

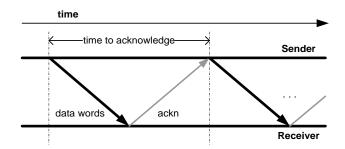

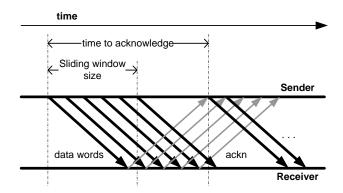

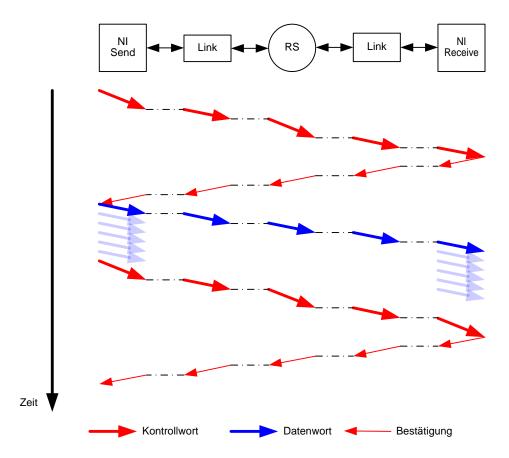

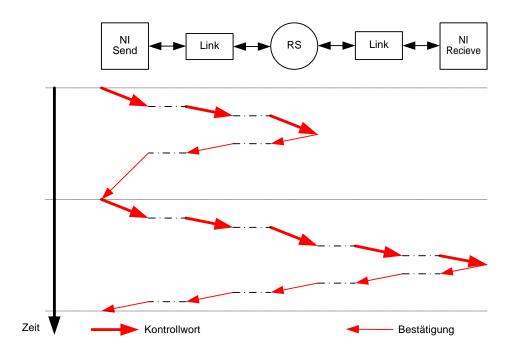

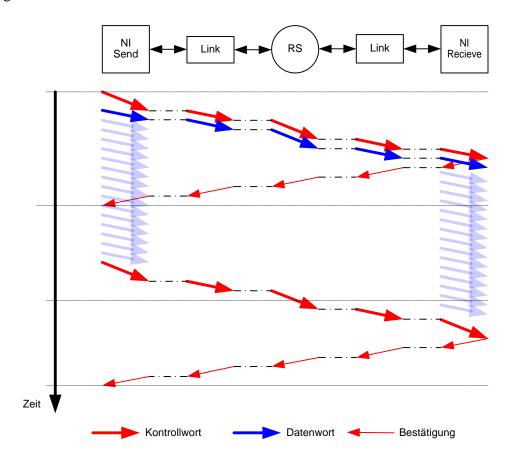

Sollte eine Fehlerkorrektur nicht möglich sein, müssen die nichtkorrigierbaren Fehler behandelt werden. Dabei werden drei Möglichkeiten unterschieden: Send and Forget, bei der auftretende Fehler akzeptiert werden, sowie Send and Wait und Send and Wait mit Sliding Window Enhancement. Bei den letzteren Protokollen werden fehlerhaft übertragene Daten erneut übertragen. Bei dem Send and Wait-Protokoll wird nach dem Senden eines Datenwortes die Bestätigung des korrekten Empfangs dieses Datenwortes (*ackn*) abgewartet bevor das nächste Datenwort gesendet wird. Bleibt die Bestätigung innerhalb einer festgelegten Zeitspanne (*time to acknowledge*) aus, wird das Datenwort erneut übertragen.

Tabelle 2.2: Paritätsbits für Fehlerschutzcodes in Abhängigkeit von der Bruttodatenwortbreite

| Bruttodatenwortbreite | Anzahl der Paritätsbits |                     |                              |  |

|-----------------------|-------------------------|---------------------|------------------------------|--|

|                       | Parity Code             | <b>Hamming Code</b> | <b>Enhanced Hamming Code</b> |  |

| 5 11                  | 1                       | 5                   | 6                            |  |

| 12 26                 | 1                       | 6                   | 7                            |  |

| 27 57                 | 1                       | 7                   | 8                            |  |

| 58 120                | 1                       | 8                   | 9                            |  |

| 121 246               | 1                       | 9                   | 10                           |  |

Durch dieses Vorgehen wird die maximal erzielbare Datenrate stark reduziert. Um dies zu vermeiden, wird hier das Send and Wait-Protokoll mit Sliding Window Enhancement verwendet. Bei diesem Protokoll muss nicht auf die Bestätigung eines einzelnen Datenwortes gewartet werden, sondern die Bestätigung muss innerhalb einer Zeitintervalls (*Sliding Window Size*) erfolgen, bevor die Datenübertragung angehalten wird. Dadurch können die Daten kontinuierlich übertragen werden solange keine nichtkorrigierbaren Fehler auftreten. Tritt ein nichtkorrigierbarer Fehler auf, müssen das fehlerhaft übertragene Datenwort sowie alle auf dieses Datenwort folgenden Datenworte erneut übertragen werden. Aus diesem Grund müssen alle noch nicht bestätigten Datenworte im sendenden Network-Interface gespeichert werden.

Abbildung 2.6: Ablauf des Send and Wait-Protokolls

Die Anzahl der Datenworte, die ohne den Erhalt einer Bestätigung gesendet werden können, wird durch das Zeitintervall Sliding Window Size definiert, welches auch die Größe des Speichers im Network-Interface bestimmt. Wenn die Sliding Window Size größer oder gleich der Zeit ist, die für eine Bestätigung benötigt wird, treten keine Leistungseinbußen bei einer fehlerfreien Datenübertragung auf.

Abbildung 2.7: Ablauf des Send and Wait-Protokolls mit Sliding Window Enhancement

#### 2.2.5 Vermittlungstechnik

Die Vermittlungstechnik definiert, wie Daten über das NoC transportiert werden. Sie hat einen großen Einfluss auf die Performance eines NoC wie auch auf die verursachten Kosten. Häufig in NoC verwendete Vermittlungstechniken sind Leitungsvermittlung und Paketvermittlung. Bei der Leitungsvermittlung wird eine physikalische Verbindung zwischen dem Sender und dem Empfänger aufgebaut, über welche anschließend die Daten übertragen werden [26]. Da bei der Leitungsvermittlung keine Daten innerhalb der Routing-Switches zwischengespeichert werden müssen, kann auf einen Speicher in den Routing-Switches verzichtet werden.

Bei der Paketvermittlung werden die Daten in Datenpakete fester Größe aufgeteilt und mit Steuerinformationen erweitert. Jedes dieser Datenpakete wird individuell über das Netz übertragen. Da die Datenpakete auf unterschiedlichen Wegen von einer Quelle zu einem Ziel übertragen werden können, ist die Reihenfolge, in der die Datenpakete beim Empfänger ankommen, nicht zwangsläufig die Reihenfolge, in der sie abgeschickt wurden. Diese muss im

Network-Interface wiederhergestellt werden. Bei Paketvermittlung werden drei Varianten unterschieden, die sich durch die Latenz und den benötigten Speicher innerhalb der Routing-Switches unterscheiden:

Beim Paketvermittlungsprotokoll *Store and Forward* [26, 27] wird ein Datenpaket vom Routing-Switch zunächst komplett empfangen, bevor es an den nächsten Routing-Switch weitergeleitet wird. Daraus resultiert eine Latenz in jedem Routing-Switch, die proportional zur Paketgröße ist. Außerdem benötigt jeder Routing-Switch einen Speicher, der mindestens ein Datenpaket zwischenspeichern kann.

Eine Weiterentwicklung ist das *Virtual cut through-Protokoll* [26]. Das in einem Routing-Switch empfangene Datenpaket wird, sobald der Kopf mit den Steuerinformationen empfangen wurde, an den nächsten Routing-Switch weitergeleitet. Dieser Routing-Switch empfängt das Datenpaket nur, wenn das komplette Datenpaket auch zwischengespeichert werden kann. Dadurch ist die Latenz, die innerhalb eines Routing-Switches verursacht wird, nur noch von der Größe der Steuerinformationen abhängig. Der Speicher des Routing-Switches muss aber immer noch ein komplettes Datenpaket speichern können.

Ein drittes, und bei NoC sehr verbreitetes Protokoll, ist das *Wormhole*-Protokoll [28]. Dabei wird das Datenpaket in sogenannte Flits aufgeteilt. Das erste Flit enthält dabei die Steuerinformationen, die benötigt werden, um das Datenpaket über das Netzwerk zu übertragen. Die restlichen Flits, die nur noch minimale Steuerinformationen enthalten, folgen dabei immer dem ersten Flit. Neben der, wie beim *Virtual cut through*-Protokoll, geringen Latenz wird hier zusätzlich der innerhalb der Routing-Switches benötigte Speicher reduziert, da minimal ein Flit gespeichert werden muss.

Die jeweiligen Vermittlungstechniken weisen verschiedene Vor- und Nachteile auf: Bei der Leitungsvermittlung ist die auftretende Latenz, sobald die Verbindung aufgebaut ist, minimal. Auch die Latenz, die durch den Verbindungsaufbau entsteht, ist bei kleinen bis mittleren Netzwerken vergleichbar mit der, die bei Verwendung des *Wormhole*- oder des *Virtual cut through*-Protokolls entsteht.

Der Speiche im Routing-Switch nimmt einen signifikanten Teil der Fläche des Routing-Switches ein. Die Größe des Speichers bestimmt auch die Leistungsfähigkeit. Neben der Größe des Speichers beeinflusst die Organisation und die Verteilung des Speichers die Leistungsfähigkeit des Routing-Switches [29, 30]. Allein durch eine Vergrößerung des Speichers ist eine Blockade des Routing-Switches durch Überlastung des Speichers nicht zu vermeiden [27]. Eine optimale Dimensionierung und Organisation des Speichers in den Routing-Switche ist daher unerlässlich [31].

Über ein Netzwerk, das Paketvermittlung verwendet, könne in der Regel mehr Daten pro Zeiteinheit übertragen werden, als über ein identisches Netzwerk, in dem Leitungsvermittlung eingesetzt wird. Dies liegt an der besseren Ausnutzung der Netzwerkressourcen. Diese werden bei der Paketvermittlung nur belegt, wenn Daten übertragen werden. Im Gegensatz dazu ist eine Netzwerkressource bei Leitungsvermittlung belegt, sobald eine Verbindung aufgebaut ist, unabhängig davon, ob Daten übertragen werden [26].

Die Art des Datenverkehrs hat auch eine Auswirkung auf die Wahl einer optimalen Vermittlungstechnik. Wenn vornehmlich große, zusammenhängende Datenmengen übertragen werden sollen, ist die Leitungsvermittlung vorteilhaft, sind es jedoch viele kleine Datenblöcke, kann das Netzwerk besser durch Paketvermittlung ausgenutzt werden.

Bei Leitungsvermittlung können, wenn eine Verbindung bereits aufgebaut ist, Quality-of-Service-Dienste wie garantierte Bandbreite oder garantierte Antwortzeiten sicher eingehalten werden. Bei Paketvermittlung ist dies nur durch das Einführen weiter Maßnahmen, wie zum Beispiel virtueller Kanäle (Virtual Channels), möglich [32, 33]. Eine weitere Möglichkeit einen garantierten Service bei einer gleichzeitig hohen Auslastung sicher zu stellen, ist die Anwendung einer Kombination von Time-Division Multiplex (TDM) und Space-Division Multiplex, wie sie in [36] für NoC untersucht wurde.

Im Gegensatz zu Prozessornetzwerken, in denen sehr häufig das Store and Forward-Protokoll verwendet wird, wird es in NoC wegen der hohen auftretenden Latenz und des hohen Speicherbedarfs im Routing-Switches selten eingesetzt [27]. Um dennoch eine möglichst hohe Auslastung der NoC-Ressourcen zu erreichen, werden häufig Wormhole- oder Virtual Cut Through-Protokolle verwendet [12]. Leitungsvermittlung wird vornehmlich in NoCs verwendet, die Datenverkehr mit einer garantierten Dienstgüte übertragen müssen.

#### 2.2.6 Priorisierung von Daten und präemptiver Zugriff auf NoC-Ressourcen

Damit die in Schicht 4 des ISO/OSI-Referenzmodells erwähnten QoS-Dienste realisiert werden können, müssen die darunterliegenden Schichten entsprechende Dienste bereitstellen, welche dies ermöglichen. Eine Möglichkeit garantierte Antwortzeiten als QoS-Aspekt zu realisieren, ist die Verwendung von priorisierten Daten.

Dabei besitzen die über das Netz zu übertragenden Daten eine Priorität, die über den Zugriff auf Netzwerkressourcen entscheidet. Diese Priorität wird bei der in Kapitel 2.2.5 vorgestellten Leitungsvermittlung an die Verbindung, die aufgebaut werden soll, bzw. die aus den Daten gebildeten Datenpakete, vererbt. Wenn eine Netzwerkressource bereits von einer Verbindung mit einer niedrigeren Priorität belegt ist, besteht bei einem präemptiven Zugriff auf diese Netzwerkressource die Möglichkeit, die bestehende Verbindung abzubrechen und den Zugriff auf diese Ressource der Verbindung mit der höheren Priorität zu gestatten.

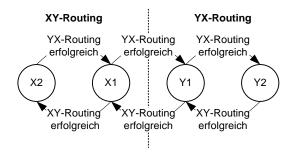

#### 2.2.7 Routing-Algorithmus

Der Routing-Algorithmus legt den Pfad im Netzwerk fest, auf dem die Daten von einer Quelle zu einem Ziel übertragen werden. Dabei muss der verwendete Routing-Algorithmus an die verwendete Netzwerktopologie angepasst sein. Es müssen Daten von jeder Quelle zu jedem Ziel im Netzwerk übertragen werden können. Dabei sollen die zur Verfügung stehenden Netzwerkressourcen bei minimalem Aufwand optimal ausgenutzt werden. Zusätzlich muss sichergestellt werden, dass der Routing-Algorithmus in Kombination mit der verwendeten Vermittlungstechnik keine Deadlock bzw. Livelock Situation erzeugt.

Ein Deadlock, der in [34] für Netzwerke definiert wurde, tritt dann auf, wenn zwei Datenpakete gegenseitig auf das Freigeben einer Netzwerkressource warten, die jeweils von dem anderen Datenpaket belegt wird. Ein spezieller Deadlock ist der Livelock [26]. Dieser tritt zum Beispiel dann auf, wenn ein Datenpaket in einem Netzwerk weitergeleitet wird, ohne jemals das Ziel zu erreichen.

Es existieren drei Strategien Deadlocks zu behandeln: Prävention, Vermeidung und Behandlung [35]. Prävention ist eine konservative Methode, um Deadlocks zu vermeiden. Dabei werden Netzwerkressourcen nur blockiert, wenn dadurch kein Deadlock entstehen kann. Ein Beispiel ist die Leitungsvermittlung, bei der nach dem versuchten Zugriff auf eine bereits belegte Netzwerkressource, alle zuvor reservierten Netzwerkressourcen freigegeben werden. Bei der Vermeidung von Deadlocks werden die benötigten Netzwerk-Ressourcen direkt belegt, auch wenn dadurch potentiell ein Deadlock verursacht werden kann. Dieser muss durch geeignete Maßnahmen vermieden werden. Ein Beispiel ist das Wormhole-Protokoll. Hier werden Deadlocks durch spezielle Routing-Algorithmen [37] oder durch das Einfügen virtueller Kanäle [38] vermieden.

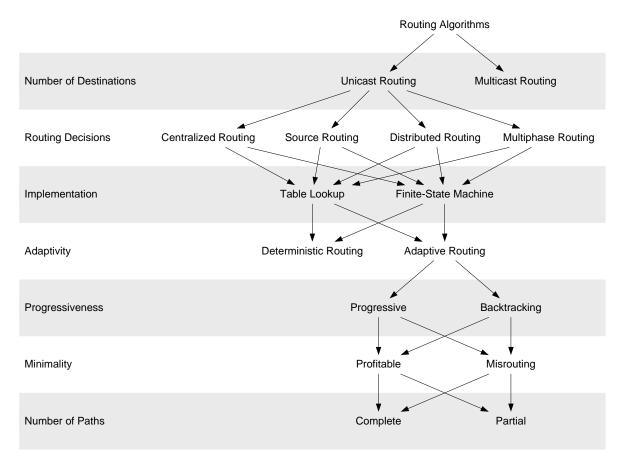

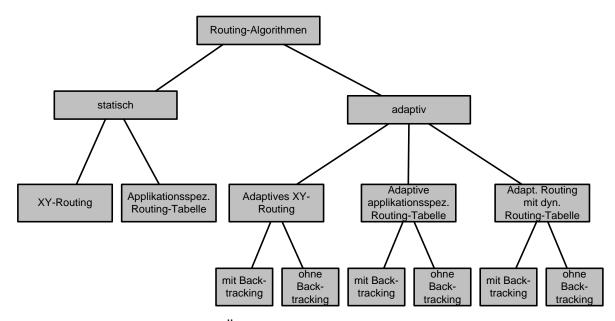

Eine allgemeine Übersicht und Klassifikation von Routing-Algorithmen wurden in [39] vorgestellt und in [26] erweitert (siehe Abbildung 2.8). Diese Einteilung lässt sich auf NoC übertragen. Routing-Algorithmen werden zunächst bezüglich der Anzahl der Verbindungsziele (Number of Destinations) in Unicast- und Multicast Routing-Algorithmen unterschieden. Bei Unicast Routing-Algorithmen werden die Daten nur zu einem Ziel weitergeleitet, wohingegen bei Multicast Routing-Algorithmen die Daten an mehrere Ziele gleichzeitig gesendet werden können.

Abbildung 2.8: Allgemeine Klassifizierung von Routing-Algorithmen [26]

Im nächsten Schritt wird eine Unterteilung nach dem Ort vorgenommen, in dem die Routing-Entscheidung getroffen wird (Routing-Decisions). Beim Centralized Routing trifft eine zentrale Stelle die Routing-Entscheidung, beim Source Routing werden die Routing-Entscheidungen bereits beim Sender getroffen, wohingegen beim Distributed Routing die Routing-Entscheidung verteilt in jedem Routing-Switch getroffen wird. Das Multiphase Routing ist eine Mischform aus den zuvor genannten Möglichkeiten. Jede dieser Möglichkeiten kann beim Unicast-Routing verwendet werden.

Das dritte Klassifizierungskriterium ist die Art der Implementierung (Implementation) des Routing-Algorithmus. Er kann in Form einer Tabelle (Table Lookup) oder als endliche Zustandsmaschine (Finite-State Machine) realisiert werden.

Bei der Adaptivität (Adaptivity) eines Routing-Algorithmus unterscheidet man zwischen deterministischem Routing (Deterministic Routing), bei dem die Daten immer den gleichen Weg von einer Quelle zu einem Ziel durch das NoC nehmen. Bei einem adaptiven Routing-Algorithmus (Adaptive Routing) hingegen ist das Routing-Ergebnis auch vom aktuellen Zustand des Netzwerkes abhängig. Bei den deterministischen Routing-Algorithmen ist keine weitere Unterteilung möglich.

Ein weiteres Unterscheidungsmerkmal ist die Reaktion auf blockierte Netzwerkressourcen (Progressiveness). Bei progressiven Algorithmen wird entweder so lange gewartet, bis die benötigte Ressource wieder verfügbar ist (Delay Model), oder die bisher gesendeten Daten werden verworfen (Loss-Model) und müssen erneut übertragen werden (siehe auch Kapitel 2.2.9). Bei Routing-Algorithmen, die Backtracking unterstützen, wird der Weg, den die Daten genommen haben, zurückverfolgt. Bei jedem Routing-Switch, der auf dem Rückweg besucht wird, wird nach einem alternativen Weg zum Ziel gesucht.

Routing-Algorithmen, die Daten immer auf direktem Weg zu ihrem Ziel leiten, werden mit Profitable oder auch Minimal Path-Routing bezeichnet. Wenn aufgrund der Routing-Entscheidung die Daten auch auf Umwegen das Ziel erreichen, spricht man von Misrouting oder Non Minimal Path-Routing.

Das letzte Differenzierungsmerkmal bezieht sich auf die Anzahl der Pfade von einer Quelle zu einem Ziel, die durch einen Routing-Algorithmus erreicht werden können. Können alle möglichen Pfade erreicht werden, handelt es sich um einen Complete- oder auch Fully Adaptive Routing-Algorithmus. Ansonsten spricht man von einem Partial Adaptive Routing-Algorithmus.

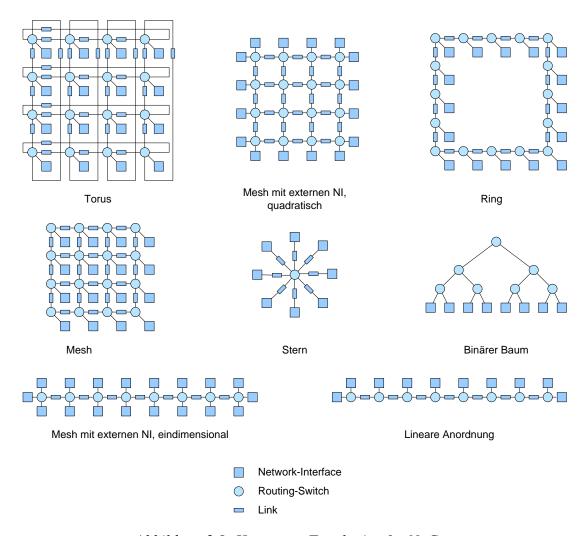

#### 2.2.8 Topologie

Ein wichtiger NoC-Parameter ist die gewählte Topologie, d.h. die Anordnung der Netzwerkressourcen untereinander. Sie hat großen Einfluss auf die Implementierungskosten und die Performance des NoC. Die meisten in NoC verwendeten Topologien wurden aus den Topologien von Multiprozessornetzwerken abgeleitet und für NoC adaptiert. Grundsätzlich lassen sich die Topologien in homogene Topologie wie z.B. Mesh, Torus, Stern (vgl. Abbildung 2.9, [40, 41, 42, 43]) und applikationsspezifische Topologien [44] unterscheiden.

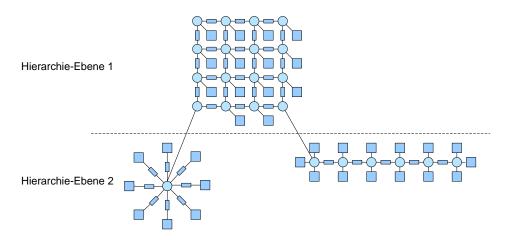

Applikationsspezifische NoC-Topologien sind häufig hierarchisch aufgebaut, d.h. das NoC ist aus mehreren Sub-NoCs aufgebaut, die eine homogene Topologie besitzen. In Abbildung 2.10 ist eine exemplarische hierarchische NoC-Topologie dargestellt, die aus einem Mesh in der obersten Hierarchiestufe und einem Stern in der unteren Hierarchiestufe besteht.

Abbildung 2.9: Homogene Topologien für NoC

Die Länge der Links hängt neben der Topologie maßgeblich von der Geometrie der funktionalen Einheiten, also dem resultierenden Layout des SoC, ab und muss bei der Topologie-Wahl des NoC berücksichtigt werden [40].

Abbildung 2.10: Exemplarische hierarchische Topologie

#### 2.2.9 Verbindungsfehlerbehandlung

Verbindungsfehler treten immer dann auf, wenn eine Verbindung bei Leitungsvermittlung nicht aufgebaut bzw. ein Datenpaket nicht übertragen werden kann. Dies ist der Fall, wenn eine benötigte Netzwerkressource bereits belegt oder nicht bereit ist, Daten zu übernehmen. In diesem Kapitel wird erläutert, wie auf diese Verbindungsfehler reagiert wird. Wenn ein Verbindungsfehler erkannt wird, muss zunächst direkt entschieden werden, ob gewartet werden soll, bis die nicht zur Verfügung stehende Netzwerkressource wieder zur Verfügung steht (Wait-Model), oder ob der Verbindungsaufbau bzw. die Datenübertragung abgebrochen werden soll, und bereits gesendete Daten verworfen und blockierte Netzwerkressourcen wieder freigegeben werden sollen (Loss-Model).

Bei dem Wait-Model wird der Verbindungsaufbau/die Datenübertragung direkt an der Stelle fortgesetzt, an der der Fehler aufgetreten ist. Dadurch können der Verbindungsaufbau bzw. die Datenübertragung sehr schnell wieder aufgenommen werden. Allerdings sind bereits belegte Netzwerk-Ressourcen auch während der Wartezeit belegt und die Wahrscheinlichkeit von Deadlocks steigt.

Wenn das Loss-Modell angewendet wird, werden die belegten Netzwerkressourcen sofort wieder freigegeben. In dem sendenden Network-Interface kann dann entschieden werden, wie auf diesen Verbindungsfehler reagiert werden soll. Der Verbindungsaufbau bzw. die Datenübertragung können direkt, nach einer festen Wartezeit oder nach einer zufälligen Wartezeit neu initiiert werden. Währen der Wartezeit können die zunächst belegten Netzwerkressourcen auch für andere Datenübertragungen genutzt werden, so dass die Wahrscheinlichkeit von Deadlocks gering ist. Eine Vermeidung von Deadlocks lässt sich durch diese Maßnahmen nicht erreichen.

Für NoC, welche die in Kapitel 2.2.6 eingeführten Prioritäten unterstützen, besteht zusätzlich die Möglichkeit, die Priorität der Daten, die übertragen werden sollen, mit jedem erfolglosen Übertragungsversuch zu erhöhen. So lässt sich die maximal in einem NoC für eine Anwendung auftretende Latenz minimieren.

#### 2.2.10 Quality-of-Service (QoS)

QoS wird als Dienst definiert, der von einem NoC einer anfordernden funktionalen Einheit bereitgestellt wird. Dies umfasst zwei Aspekte: die Definition des Dienstes und die Aushandlung des Dienstes. Die Aushandlung besteht dabei aus dem Ausgleichen der von der funktionalen Einheit angeforderten Dienste mit den, vom NoC bereitgestellten, Diensten. Ein Dienst kann dabei Aspekte wie garantierten Durchsatz, minimale Latenz, geringe Verlustleistung, Grenzen bezüglich Jitters, Datenfehlerfreiheit etc. umfassen [17].

Für NoC werden in der Literatur meistens zwei Klassen von QoS unterschieden, best effort services (BE) für Datenübertragungen die keine speziellen QoS-Anforderungen haben und guaranteed services (GS) für Übertragungen mit speziellen Anforderungen [45, 46]. Die speziellen QoS-Anforderungen werden in Korrektheit des Ergebnisses, Abschluss der Datenübertragung und Grenzen für Performance-Werte definiert. BE-Datenverkehr erhöht dabei die Auslastung des NoCs. GS-Datenverkehr steigert die Vorhersagbarkeit auf Kosten der Ausnutzung des NoC. Eine hohe Vorhersagbarkeit wird insbesondere bei Echtzeitsystemen benötigt [47]. Daher wird in [48] eine Kombination von BE- und GS-Datenverkehr gefordert.

Häufig wird GS-Datenverkehr aufgrund von statistischen Verteilungen garantiert. Diese werden als *soft* oder *statistischer* GS-Datenverkehr bezeichnet. Soll dagegen eine absolute Vorhersagbarkeit realisiert werden, spricht man von hartem GS-Datenverkehr.

Um GS-Datenverkehr zu realisieren, werden Dienste wie zum Beispiel der in Kapitel 2.2.4 vorgestellte Datenfehlerschutz, oder die in Kapitel 2.2.6 eingeführte Priorisierung von Daten benutzt. Auch die verwendete Vermittlungstechnik (Kapitel 2.2.5) hat Einfluss auf den QoS: paketbasierte Ansätze werden häufig bei BE-Datenverkehr verwendet, leitungsbasierte Techniken für GS-Datenverkehr. Eine weitere Möglichkeit, um Performance-Anforderungen zu erfüllen, insbesondere von hartem GS-Datenverkehr, sind virtuelle Kanäle. Sie können verwendet werden, um mit Hilfe von time division multiplexing eine verbindungsorientierte Paketvermittlung zu realisieren.

Beispiele für NoC, die soft GS-Datenverkehr unterstützen, sind QNoC [49], [32] und [50]. Eine Sonderstellung nimmt SoCBUS [51] ein. Hier werden Verbindungen aufgebaut, die grundsätzlich harten GS-Datenverkehr unterstützen. Jedoch erfolgt der Verbindungsaufbau als soft GS-Datenverkehr.

NoC die harten GS-Datenverkehr unterstützen sind AETHERAL [52], NOSTRUM [53], MANGO [54], SONICS [55], aSoC [56], sowie die in [57], [58] und [59] vorgestellten NoC.

#### 2.3 Bewertungskriterien

Ein einheitliches Bewertungsschema, mit dem NoC verglichen werden können, ist nur in Grundzügen vorgeschlagen worden [60]. Um ein NoC bewerten zu können, müssen zunächst verschiedene Bewertungsmaße definiert werden. Diese Bewertungsmaße lassen sich grundsätzlich in Bewertungsmaße, welche die Leistungsfähigkeit eines NoC beurteilen, und Bewertungsmaße, welche die Kosten bewerten, die von dem NoC verursacht werden, unterteilen. Weitere Aspekte sind die Verlässlichkeit des NoC und die Einhaltung von QoS-Anforderungen. Je nach Anwendung und Vorgaben für das NoC können diese Kriterien unterschiedlich gewichtet werden.

#### **2.3.1** Kosten

Die durch ein NoC verursachten Kosten werden durch die benötigte Fläche des NoC, die Verlustleistung und die benötigte Entwurfszeit ausgedrückt. Die Fläche eines NoC lässt sich aus dem Layout des NoC bestimmen. Die Verlustleistungsaufnahme ist jedoch dynamisch und hängt auch von der Auslastung des NoC und den übertragenen Daten ab. Neben diesen Kosten, die sich quantitativ erfassen lassen, gibt es weitere, "weiche" Kostenfaktoren. Dazu zählen beispielsweise die Entwicklungszeit oder die Erfahrung, die ein Entwickler für die Implementierung eines NoCs benötigt.

#### 2.3.2 Performance

Um zu belegen, dass die von einer Anwendung an das NoC gestellten Kommunikationsanforderungen erfüllt werden, muss die Performance des NoC bestimmt werden. Dies kann auf unterschiedliche Arten erfolgen, welche sich sowohl in ihrer Genauigkeit wie auch in dem Aufwand zur Bestimmung der Performance unterscheiden.

Die genaueste Möglichkeit, die Performance eines NoC zu bestimmen, ist die Ausführung einer Anwendung auf einem SoC. Dazu müssen sowohl die funktionalen Einheiten wie auch gegebenenfalls die Software für die funktionalen Einheiten auf dem SoC implementiert, und das SoC gefertigt sein.

Eine weitere Möglichkeit das NoC innerhalb des SoC zu testen, ohne das SoC zu fertigen, ist die Emulation bzw. Simulation des gesamten SoC. Die Simulation des gesamten SoC ist in der Regel zu langsam, um komplette Anwendungen auszuführen. Bei der Emulation eines SoC werden schnell die Kapazitätsgrenzen der meist zur Emulation verwendeten FPGAs erreicht, oder es werden aufwändige Emulationsumgebungen [61] benötigt. Ein weiteres Problem bei diesem Vorgehen ist, dass das komplette SoC, wie auch die benötigte Software, sowohl bei der Emulation wie auch bei der Simulation bereits implementiert sein muss.

Um dies Problem zu lösen, lassen sich die funktionalen Einheiten des SoC abstrahieren. So kann anstelle des SoC lediglich das NoC als Teil des SoC untersucht werden. Der Datenverkehr, der von den funktionalen Einheiten erzeugt wird, muss in diesem Fall modelliert werden. Dadurch lässt sich das NoC simulieren bzw. auf einem FPGA emulieren. Die verschiedenen Möglichkeiten zur Performance-Bestimmung werden in Kapitel 3.4 und Kapitel 3.6 vorgestellt und bewertet. Ein weiterer Vorteil der Abstraktion der funktionalen Einheiten ist, dass sowohl die funktionalen Einheiten des SoC wie auch die Software, die auf den funktionalen Einheiten des SoC ausgeführt werden soll, noch nicht implementiert sein müssen. Dadurch kann bereits in einem frühen Entwurfsstadium die Performance von NoC bestimmt werden.

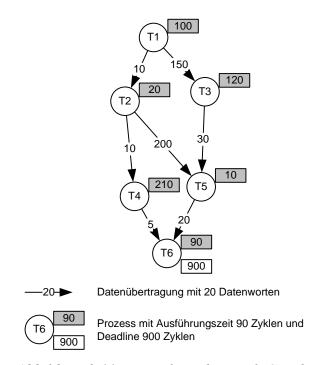

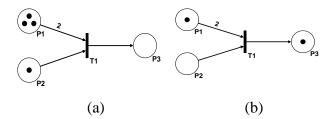

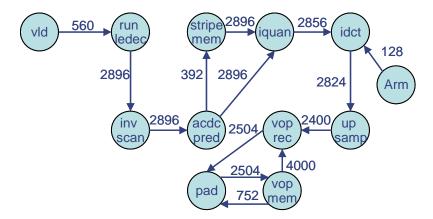

Der auf einem NoC durch die funktionalen Einheiten erzeugte Datenverkehr einer Anwendung kann in Form eines sogenannten Task-Graphen beschrieben werden [62]. Dieser, in Abbildung 2.11 exemplarisch dargestellte, gerichtete Graph  $G_{TG}(V,A)$  besteht aus einer Menge Knoten V, die Prozesse repräsentieren, und aus einer Menge Kanten A, die den Datenverkehr zwischen zwei Prozessen darstellen. Jeder Knoten  $v_i$  besitzt eine definierte Ausführungszeit  $t_{A,i}$ . Optional kann einem Knoten eine Deadline zugewiesen werden. Dabei handelt es sich um einen Zeitpunkt, zu dem der zugehörige Prozess abgearbeitet sein muss. Die Kante  $a_{i,j}$  vom Knoten  $v_i$  zum Knoten  $v_j$  werden mit einer Datenmenge D gewichtet, die von dem Startknoten zu dem Zielknoten übertragen werden soll. Mit Hilfe eines solchen Task-Graphen lassen sich die Kommunikations-Anforderungen darstellen, die eine auf ein SoC abgebildete Anwendung besitzt.

Abbildung 2.11: Exemplarischer Task-Graph

Zur Analyse der Performance verschiedener NoC-Implementierungen für nicht definierten Datenverkehr werden Benchmarks benötigt. Diese können den Datenverkehr realer, repräsentativer Anwendungen und/oder auch synthetischen Datenverkehr auf einem NoC beschreiben. Allgemeine Benchmarks, wie sie zum Beispiel bei der Bewertung von Prozessoren [63] oder auch Multiprozessoren eingesetzt werden, existieren für NoC nicht [60]. In der Literatur werden häufig Benchmarks, die auf synthetischem Datenverkehr oder repräsentative Anwendungen wie Videocodierung [56, 64, 65] oder WLAN-Baseband Processing [66] beruhen, verwendet.

Ein häufig benutzter synthetischer Datenverkehr ist Random Traffic. Dabei werden Datenquelle, Datensenke, sowie die zu übertragende Datenmenge und Datenrate für jede

einzelne Datenübertragung zufällig ausgewählt. Es wird zwischen uniform Random Traffic [43, 67, 68] und Localized Random Traffic [69, 70, 71] unterschieden. Bei Uniform Random Traffic ist die Wahrscheinlichkeit, mit der eine Datensenke für eine Datenübertragung ausgewählt wird, für alle Datensenken gleich. Die Wahrscheinlichkeit, dass eine Datensenke in der Nähe einer Datenquelle liegt, ist bei lokalem Random Traffic erhöht. Dies wird häufig durch Poisson- oder Exponentialverteilungen realisiert [26].

Eine Alternative ist die Bestimmung der Datensenke nach einem festgelegten Algorithmus, wie zum Beispiel beim Bit Reversal, Perfect Shuffle, Butterfly, Matrix Transpose oder Complement Traffic (vgl. Tabelle 2.3 und [26]).

|                  | Binäre Koordinate           | Binäre Koordinaten                           |                                                         |

|------------------|-----------------------------|----------------------------------------------|---------------------------------------------------------|

|                  | Datenquelle                 | Datensenke                                   |                                                         |

| Bit Reversal     | $a_{n-1}, a_{n-2},,a_1,a_0$ | $a_0, a_1,, a_{n-2}, a_{n-1}$                |                                                         |

| Perfect Shuffle  | $a_{n-1}, a_{n-2},,a_1,a_0$ | $a_{n-2}, a_{n-3},, a_0, a_{n-1},$           | Linksrotation um 1 Bit                                  |

| Butterfly        | $a_{n-1}, a_{n-2},,a_1,a_0$ | $a_0, a_{n-2},,a_1, a_{n-1}$                 | Austauschen des<br>höchst- und<br>niederwertigsten Bits |

| Matrix Transpose | $a_{n-1}, a_{n-2},,a_1,a_0$ | $a_{n/2-1},,a_0,a_{n-1},,a_{n/2}$            |                                                         |

| Complement       | $a_{n-1}, a_{n-2},,a_1,a_0$ | $\overline{a_{n-1}, a_{n-2},, a_{1}, a_{0}}$ |                                                         |

Tabelle 2.3: Synthetische Datenverkehrsarten

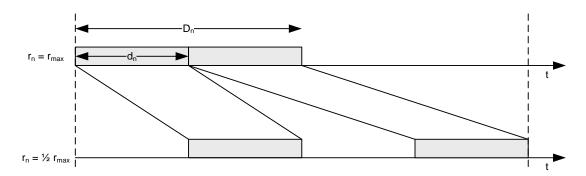

Sowohl durch Task-Graphen beschriebener Datenverkehr, als auch synthetischer Datenverkehr, besteht aus einzelnen Datenübertragungen. Diese werden durch eine Datenmenge  $D_n$ , eine Datenblockgröße  $d_n$  und eine angeforderte Datenrate  $r_n$  definiert. Dabei muss  $D_n$  ein ganzzahliges Vielfaches von  $d_n$  sein.

Abbildung 2.12: Format einer Datenübertragung

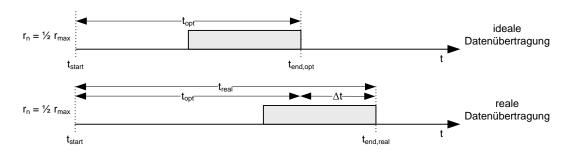

Die Performance eines NoC kann durch verschiedene Bewertungsmaße dargestellt werden. Ein verbreitetes und wichtiges Maß ist dabei die Latenz [5], die bei einer Datenübertragung auftritt. Diese berechnet sich aus der Zeit, die für die Datenübertragung insgesamt benötigt wird ( $t_{real}$ ), und der Zeit, die für eine sofortige Übertragung (ohne NoC) benötigt worden wäre

(siehe Abbildung 2.13). Diese Zeit  $t_{opt}$  lässt sich aus der Datenrate  $r_n$  und der übertragenen Datenmenge  $D_n$  einer Datenübertragung berechnen

$$t_{opt} = \frac{D_n}{r_n}. (2.3)$$

Die Latenz lässt sich in zwei Teilzeiten aufteilen: die erste Zeit wird durch die Verzögerung der Network-Interfaces, Routing-Switches und Links verursacht. Verzögerungen, die durch belegte Netzwerkressourcen verursacht werden, sind nicht berücksichtigt. Die zweite Teilzeit berücksichtigt diese dynamischen Effekte. Die Größe dieses Anteils ist stark von der Auslastung des NoC abhängig. Für Datenverkehr, der aus mehreren Datenübertragungen besteht, lässt sich so eine minimale, durchschnittliche und maximale Latenz bestimmen.

Abbildung 2.13: Definition der Latenz einer Datenübertragung

Die Datenrate  $r_n$  wird in diesem Fall von der Datenquelle vorgegeben und entspricht dem Intervall, in dem Datenpakete versendet werden. Die realisierte Datenrate lässt sich wie folgt berechnen:

$$r_{real} = \frac{D_n}{\Delta t + \frac{D_n}{d_n} t_{opt}} \tag{2.4}$$

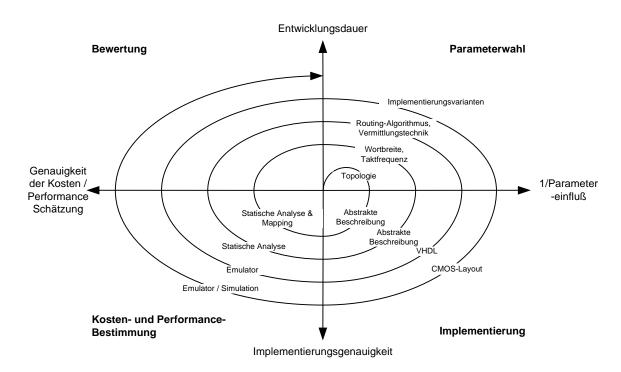

# 2.4 Entwurfsproblematik

NoC-spezifische Parameter spannen einen großen Entwurfsraum auf. Die Dimensionen dieses Entwurfsraums repräsentieren dabei zum einen die in Kapitel 2.3.1 vorgestellten Kosten (Verlustleistung, Siliziumfläche, Entwicklungszeit und -aufwand) wie auch die in Kapitel 2.3.2 präsentierten Performance-Maße. Zusätzlich existieren noch weitere Dimensionen des Entwurfsraums wie beispielsweise QoS-Anforderungen, Effizienz (beispielsweise Energie/Bit), Testbarkeit (Testability) oder Flexibilität des NoC. Testbarkeit bezeichnet hier die Möglichkeit zur Verifikation der korrekten Funktion des NoC auf dem gefertigten Chip.

Innerhalb dieses Entwurfsraumes kann durch Variation von NoC-Parametern manövriert werden, wobei jeder Punkt des Entwurfsraums eine NoC-Implementierung repräsentiert. Um eine optimale NoC-Implementierung für ein System zu identifizieren, müssen die einzelnen

Implementierungen bewertet werden. Dazu muss eine Gewichtung der einzelnen Kostenfaktoren erfolgen.

Insbesondere die Entwicklungszeit und der Entwicklungsaufwand hängen neben den gewählten NoC-Parametern von dem verwendeten Entwicklungsprozess ab. Die Entwicklungszeit umfasst neben der Zeit zur Identifizierung der geeigneten NoC-Parameter auch die Zeit zur Implementierung, Bewertung und Verifizierung der NoC-Implementierung.

Um die Entwicklungszeit so gering wie möglich zu halten, ist eine systematische Entwurfsmethodik notwendig, um in dem komplexen Entwurfsraum die NoC-Implementierung zu identifizieren und zu realisieren, welch die durch das System gegebenen Anforderungen bei minimalen Kosten erfüllt. Eine solche Entwurfsmethodik wird im folgenden Kapitel vorgestellt.

Voraussetzung für eine systematische Untersuchung des Entwurfsraumes ist eine modulare und generische Beschreibung des NoC. Auf Basis dieser Beschreibung soll eine Implementierung eines NoCs unter Minimierung des dazu erforderlichen Entwurfsaufwands ermöglicht werden. Weiterhin muss eine Änderung einzelner NoC-Parameter möglich sein, ohne das NoC komplett neu zu beschreiben. Eine NoC-Beschreibung, die diesen Anforderungen genügt, wird in Kapitel 4.1 eingeführt.

Eine Untersuchung des Entwurfsraums für SoC wurde bereits in [75] eingeführt. Dabei wurde jedoch die Kommunikation zwischen den einzelnen funktionalen Einheiten des SoC nicht berücksichtigt. Diese hat jedoch eine nicht unerhebliche Auswirkung auf die Performance sowie die Kosten eines SoC, insbesondere bei SoC mit vielen funktionalen Einheiten. Daher wurde im Rahmen dieser Arbeit diese Ansätze aus [75] auf die Untersuchung des Entwurfsraums von SoC mit NoC erweitert.

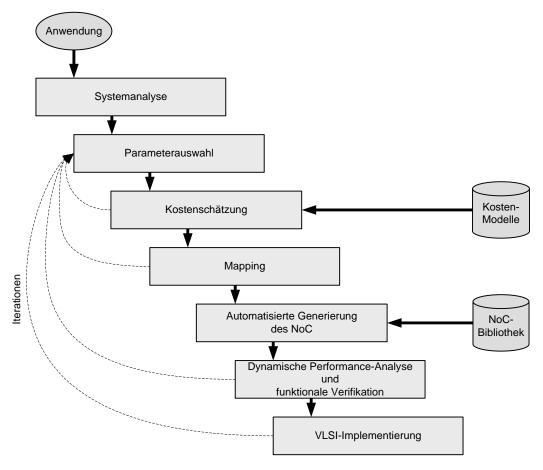

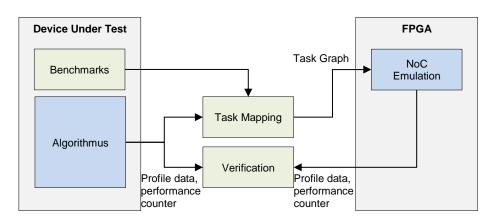

# 3 Effiziente, emulatorgestützte NoC-Entwurfsmethodik

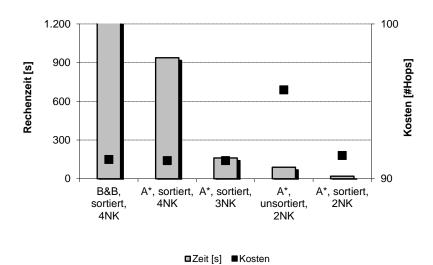

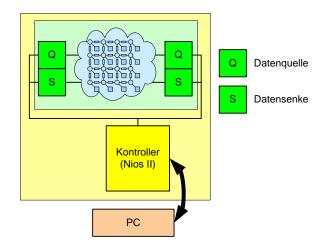

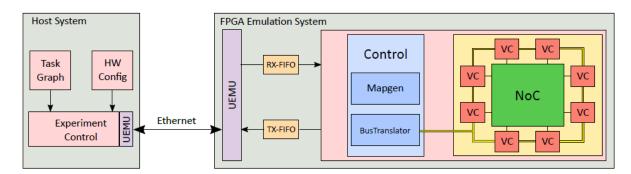

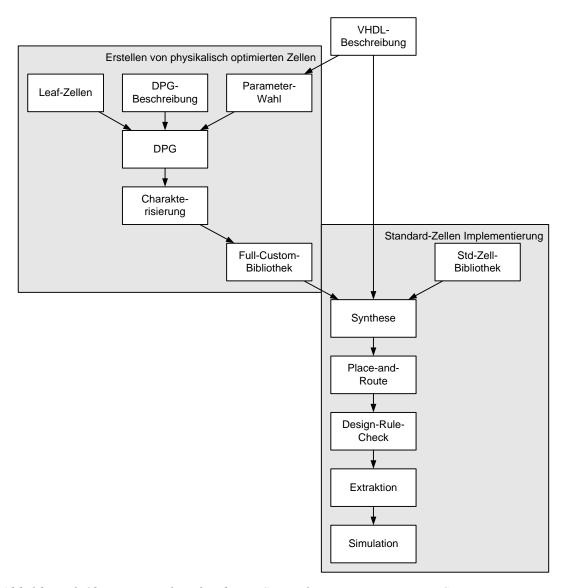

Durch die Vielzahl von NoC-spezifischen Parametern ergibt sich ein umfangreicher Entwurfsraum für NoC. Daher ist ein systematischer NoC-Entwurf notwendig, um in einer möglichst kurzen Entwurfszeit ein NoC zu implementieren und zu verifizieren, das die gestellten Anforderungen optimal erfüllt. Diese Anforderungen sind von Anwendung zu Anwendung bzw. von Anwendungsklasse zu Anwendungsklasse unterschiedlich. Daher muss jeweils individuell ein passendes NoC entworfen werden. Eine solche Entwurfsmethodik, die im Rahmen dieser Arbeit entwickelt wurde, wird in diesem Kapitel vorgestellt: Sie umfasst alle Schritte von der Systemanalyse über die automatisierte NoC-Generierung, Verifikation und Performance-Bewertung bis hin zur physikalisch optimierten VLSI-Implementierung. Dieser automatisierte Entwurfsablauf ist in Abbildung 3.1 schematisch dargestellt.

Abbildung 3.1: Entwurfsmethodik für NoC

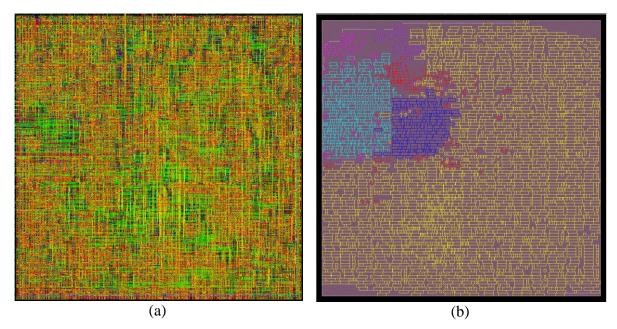

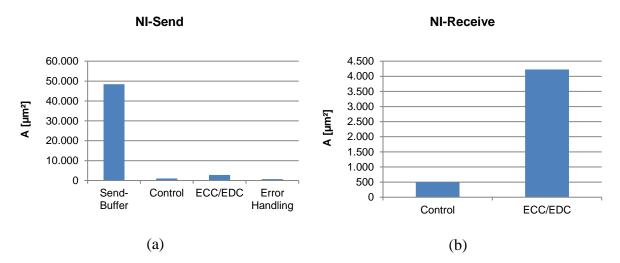

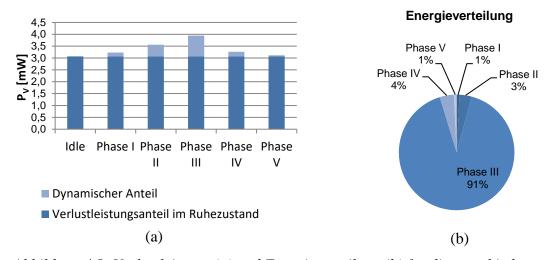

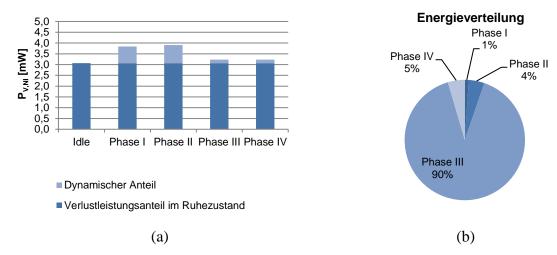

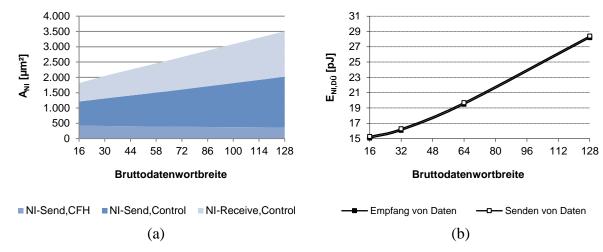

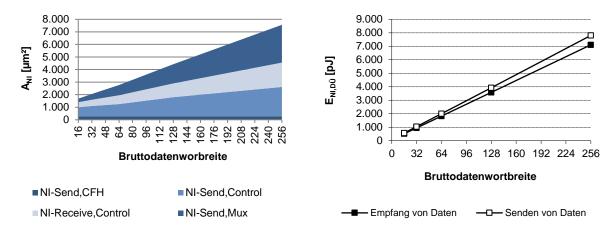

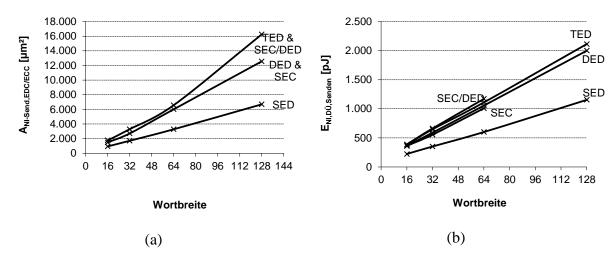

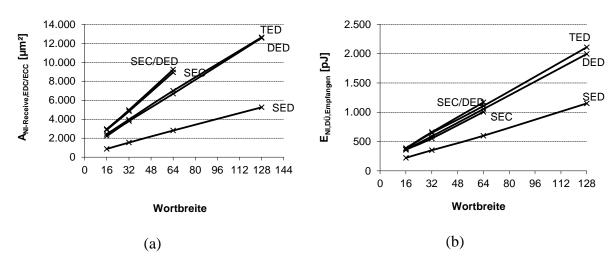

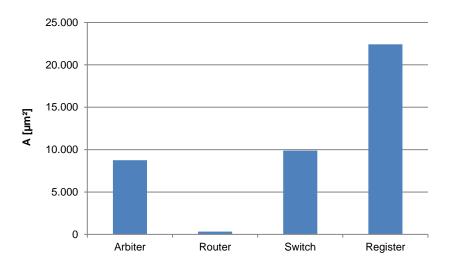

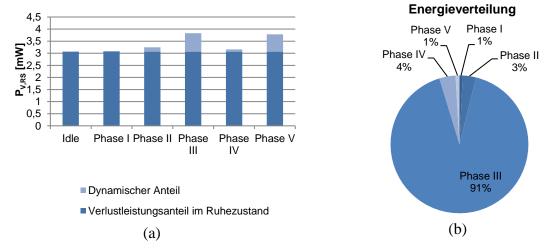

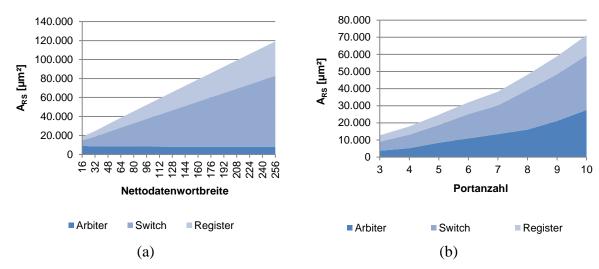

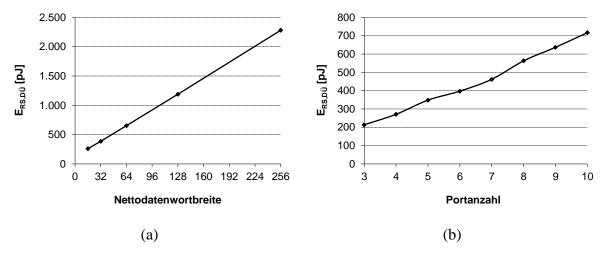

Das Identifizieren des passenden NoC bzw. der NoC-Parameterkombination, die dieses NoC beschreibt, ist ein iterativer Prozess. Sobald während des Entwurfsprozesses festgestellt wird, dass die Kosten zu hoch sind, oder die Performance nicht ausreichend ist, wird diese Iteration abgebrochen und ein neuer Versuch mit veränderten NoC-Parametern gestartet. Um die Entwurfszeit zu minimieren muss sowohl die Anzahl der Iterationen, wie auch die