# **Dual-Loop Gate Drivers with Analog and Digital Slope Shaping**

Von der Fakultät für Elektrotechnik und Informatik der Gottfried Wilhelm Leibniz Universität Hannover zur Erlangung des akademischen Grades Doktor-Ingenieurin/Doktor-Ingenieur (abgekürzt: Dr.-Ing.) genehmigte Dissertation

von

## Johannes Matthias Gröger, M. Sc.

geboren am 29.09.1986 in Ulm

2019

- 1. Referent: Prof. Dr.-Ing. Bernhard Wicht (Leibniz Universität Hannover)

- 2. Referent: Prof. Dr. techn. Bernd Deutschmann (Technische Universität Graz)

Tag der Promotion:16.09.2019

# Abstract

Setting the values of the switching transients  $(dV_{CE}/dt \text{ and } dI_C/dt)$  has become more and more important especially for modern power semiconductor technologies, like insulated gate bipolar transistors (IGBTs) in the newest trench-/fieldstop technologies, Superjunction MOSFETs or silicon carbide (SiC). The extremely fast switching speeds of these devices have led to switching losses of almost close to zero, but has also complicated the control of voltage and current spikes or electromagnetic compatibility (EMC) in switched applications like motor drives, switched-mode power supplies (SMPS) and power factor correction (PFC) stages. The focus of this work is on a new hardware concept for an active gate driver that is capable of flexible switching behavior optimization by using a dual-loop approach. This enables regulated  $dV_{CE}/dt$  and  $dI_C/dt$  transients to be optimal for specific application requirements. Conventional gate drivers, as used in most commercial products, are commonly designed in passive architectures and are therefore unsuitable for an effective and flexible optimization of the switching behavior, due to their limited capabilities to influence the switching transients ( $dV_{CE}/dt$  and  $dI_C/dt$ ). Closed-loop gate drivers offer a sophisticated approach to achieve a desired trade-off between switching losses, delay, EMC and safe operating area (SOA) and can be realized in the analog or in the digital domain. The dual-loop design adressed in this work comprises both analog and digital closed-loop control on  $dV_{CE}/dt$  and  $dI_C/dt$ . Hence, it combines high speed and linearity of a closed-loop analog gate driver, that is able to perform continous-time regulation, with the advantages of adaptive digital control, like flexibility and parameter independency.

As the analog loop is the critical element, setting the dynamics and stability of the system, it is modeled and analyzed in the small-signal domain with focus on non-linearity of parameters and operating point dependencies. The model parameters are extracted from experimental data for an IGBT and a Superjunction MOSFET. Major parameters of influence, such as gate resistor and the capacitance in the summing node, are investigated to achieve stable control. Another important detail is the sensing of  $dV_{CE}/dt$  and  $dI_C/dt$ to generate input data for the signal processing blocks of the digital loop. This guarantees for accurate interaction between the analog and the digital loop. The sensing blocks are optimized for accuracy and bandwidth. Different circuit concepts for the gate driver are evaluated and the full system is designed in hardware. Experimental results show that the combination of a digital and an analog loop increases the accuracy of the  $dV_{CE}/dt$  and  $dI_C/dt$  control compared to a pure analog loop system by more than 10%, independent of the actual device technology utilized. Precise slew rate control is demonstrated for IGBT,

### Superjunction MOSFET and SiC.

Due to the device-independency, the gate driver enables the flexible use of different device technologies in a given application. The more accurate control helps to control voltage and current overshoots. In motor drives, the control of  $dV_{CE}/dt$  helps to protect the motor from destruction and therefore increases the lifetimes.

Index terms: Slope shaping, gate drivers, multi-loop control

# Zusammenfassung

Die Einstellbarkeit der Schalttransienten ( $dV_{CE}/dt$  und  $dI_C/dt$ ) gewinnt heutzutage erheblich an Bedeutung, insbesondere bei der Nutzung moderner Leistungshalbleiter-Technologien wie Trench-/Fieldstop-IGBTs, Superjunction MOSFETs oder Siliziumkarbid (SiC). Die extrem schnellen Schaltflanken dieser Bauelemente haben zwar die Schaltverluste auf ein Minimum reduziert, jedoch gleichzeitig die Kontrolle über Strom- und Spannungsspitzen sowie elektromagnetischer Verträglichkeit (EMV) in geschalteten Anwendungen wie Motorantrieben, Schaltnetzteilen (Switched-Mode Power Supplies, SMPS) oder Leistungsfaktorkorrekturstufen (Power Factor Correction, PFC) zum Teil deutlich erschwert. Der Schwerpunkt dieser Arbeit liegt auf einem neuartigen Hardware-Konzept für einen aktiven Gate-Treiber, der in der Lage ist, das Schaltverhalten durch Nutzung eines Dual-Loop-Ansatzes flexibel zu optimieren. Dieser ermöglicht über eine  $dV_{CE}/dt$  und  $dI_C/dt$  – Regelung, die Schaltflanken auf anwendungsseitig vorgegebene Spezifikationen einzustellen. Konventionelle Gatetreiber, die in den meisten kommerziellen Produkten genutzt werden, weisen häufig eine passive Architektur auf, die hierfür aufgrund der begrenzten und unflexiblen Beeinflussbarkeit der Schalttransienten ungeeignet ist. Gatetreiber mit geschlossener Regelschleife, die entweder analog oder digital ausgeführt werden kann, bieten hingegen einen geschickten Ansatz, einen Kompromiss zwischen Schaltverlusten, Schaltverzögerungen, EMV sowie sicherem Betriebsbereich (safe operating area, SOA) herzustellen. Das Dual-Loop-Design in dieser Arbeit beinhaltet sowohl eine analoge als auch eine digitale geschlossene Regelschleife für  $dV_{CE}/dt$  und  $dI_C/dt$ . Hierdurch wird die hohe Regelgeschwindigkeit und Linearität der analogen Regelung, die zeitkontinuierlich aktiv ist, mit den Vorteilen einer adaptiven digitalen Regelung, wie Flexibilität und Parameterunabhängigkeit, kombiniert. Da die analoge Regelschleife das kritische Element ist, das die Dynamik und Stabilität des Gesamtsystems festlegt, wird diese mit Hilfe eines Kleinsignalansatzes modelliert und analysiert, mit dem besonderen Fokus auf nichtlinearen Parametern sowie Arbeitspunktabhängigkeiten. Die Modellparameter werden dabei am Beispiel eines IGBT und eines Superjunction MOSFETs aus experimentell gewonnenen Datensätzen extrahiert. Die Parameter mit größerem Einfluss auf Stabilität und Systemdynamik werden vorgestellt. Ein weiteres wichtiges Detail ist die Erfassung von  $dV_{CE}/dt$  und  $dI_C/dt$  für die anschließende Signalverarbeitung in der digitalen Regelschleife. Diese Erfassung stellt die Genauigkeit im Zusammenspiel zwischen digitaler und analoger Regelschleife sicher. Aus diesem Grund wird die Messhardware in einem experimentellen Ansatz in ihrer Genauigkeit und Bandbreite optimiert. Mehrere Schaltungskonzepte für den Gatetreiber werden vorgestellt, ausgewertet und in Hardware ausgelegt und hergestellt. Experimentelle Ergebnisse zeigen, dass die Kombination aus analoger und digitaler Regelscheife die Genauigkeit der  $dV_{CE}/dt$  und  $dI_C/dt$ – Regelung im Vergleich zu einer rein analogen Regelschleife unabhängig vom eingesetzten Leistungshalbleiter um mindestens 10% erhöht. Die präzise Flankenregelung wird dabei für IGBT, Superjunction MOSFET und SiC nachgewiesen. Aufgrund der Unabhängigkeit vom verwendeten Bauelement ermöglicht der Gatetreiber den sicheren und flexiblen Einsatz verschiedener Technologien in einer vorgegebenen Anwendung. Die genauere Regelung unterstützt dabei, während des Schaltvorgangs auftretende Strom- und Spannungsspitzen im Griff zu halten. In Motorantrieben hilft die  $dV_{CE}/dt$ -Regelung, den Motor vor Zerstörung zu schützen und damit die Laufzeiten zu erhöhen.

Schlagworte: Schaltflankenregelung, Gate-Treiber, Multi-Loop-Regelung

# Acknowledgements

This work is the result of my employment as a research assistant at the Robert Bosch Center of Power Electronics (rbz) of Reutlingen University.

I would like to express my deepest gratitude to my advisor Prof. Dr.-Ing. Bernhard Wicht for the opportunity to work on my Ph.D. thesis in his research group, for his continous support and for the time he invested for this work. Our numerous interesting and fruitful discussions have constantly motivated me to advance my research work.

Many thanks belong to the high voltage gate drive group at Infineon Technologies Austria AG, Villach, which provided financial and technical support for this work. Special thanks to Karl Norling for his constant interest in the topic and his continous support. He was always available for in-depth technical discussions. I am grateful to many colleagues at Infineon Technologies in Villach, who provided help on various details throughout this research.

I would like to adress many thanks to Prof. Dr. Bernd Deutschmann, TU Graz, for being part of the jury of my doctoral defense. I would also like to thank Prof. Dr.-Ing. Axel Mertens for taking over the chair of the jury. Prof. Deutschmann and Prof. Mertens have contributed several outstanding publications to the research field, which have encouraged me and supported the progress of my work.

I am very grateful to all colleagues of Prof. Wicht's research group at Reutlingen University and Leibniz University Hannover, for their support and for the constructive collaboration.

I would like to thank my wife Sabrina as well for her constant support and for her patience during my long working hours. My further thanks belong to my whole family.

# Contents

| 1 Introduction |     |         |                                                                      |    |  |  |

|----------------|-----|---------|----------------------------------------------------------------------|----|--|--|

|                | 1.1 | Introdu | uction                                                               | 1  |  |  |

|                | 1.2 | Scope   | of this Work                                                         | 3  |  |  |

|                | 1.3 | Contri  | bution of this Work                                                  | 4  |  |  |

|                | 1.4 | Outlin  | e                                                                    | 7  |  |  |

| 2              | Fun | dament  | tals                                                                 | 9  |  |  |

|                | 2.1 | Device  | es and Circuits in Power Electronics                                 | 9  |  |  |

|                |     | 2.1.1   | Modern Generation Power Semiconductor Devices                        | 9  |  |  |

|                |     | 2.1.2   | Half-Bridge Circuits in Electrical Converters                        | 10 |  |  |

|                | 2.2 | Switch  | ning Behavior of Gate-Controlled Devices                             | 11 |  |  |

|                |     | 2.2.1   | Equivalent Circuit for the Switching Dynamics                        | 11 |  |  |

|                |     | 2.2.2   | Turn-on Switching Behavior                                           | 13 |  |  |

|                |     | 2.2.3   | Turn-off Switching Behavior                                          | 16 |  |  |

|                |     | 2.2.4   | Trade-offs Resulting from the Slew Rates of the Switching Transients | 18 |  |  |

|                | 2.3 | State-o | of-the-Art Gate Drive Concepts                                       | 24 |  |  |

|                |     | 2.3.1   | Passive Gate Drivers                                                 | 25 |  |  |

|                |     | 2.3.2   | Active Gate Drivers with Open-Loop Slope Shaping                     | 27 |  |  |

|                |     | 2.3.3   | Active Gate Drivers with Closed-Loop Slope Shaping                   | 28 |  |  |

| 3              | The | Dual-I  | Loop Gate Driver Concept                                             | 33 |  |  |

|                | 3.1 | Introdu | uction                                                               | 33 |  |  |

|                | 3.2 | The A   | nalog Loop Concept                                                   | 34 |  |  |

|                | 3.3 | Model   | ing and Analysis                                                     | 36 |  |  |

|                |     | 3.3.1   | Small-Signal Modeling of the Gate Driver                             | 36 |  |  |

|                |     | 3.3.2   | Small-Signal Stability Analysis                                      | 39 |  |  |

|                |     | 3.3.3   | Large Signal Transient Domain Analysis                               | 43 |  |  |

|                |     |         |                                                                      |    |  |  |

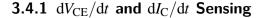

|   | 3.4 | Optimi  | ized $dV_{CE}/dt$ , $dI_C/dt$ Sensing                                 | 44  |

|---|-----|---------|-----------------------------------------------------------------------|-----|

|   |     | 3.4.1   | $dV_{CE}/dt$ and $dI_C/dt$ Sensing                                    | 46  |

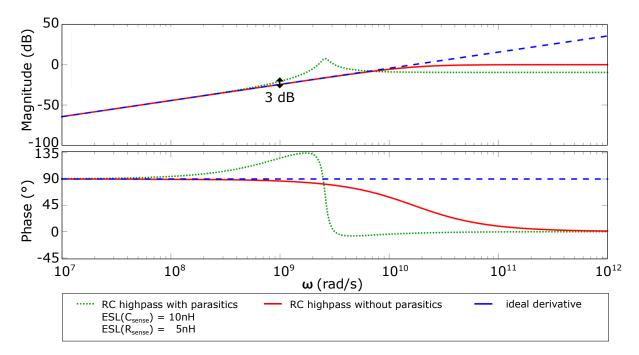

|   |     | 3.4.2   | Influences of Parasitics in $dV_{CE}/dt$ Sensing                      | 47  |

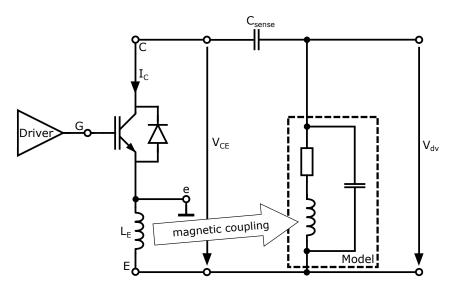

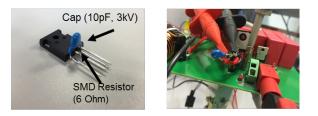

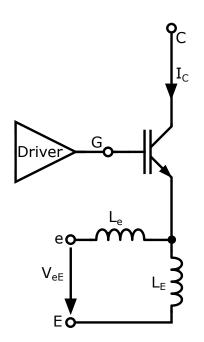

|   |     | 3.4.3   | Influences of Parasitics in $dI_C/dt$ Sensing                         | 50  |

|   |     | 3.4.4   | Optimized Setup                                                       | 52  |

|   | 3.5 | The Di  | gital Loop Concept                                                    | 54  |

|   | 3.6 | System  | n Requirements                                                        | 55  |

| 4 | Ana | log Loc | op Design and Evaluation                                              | 59  |

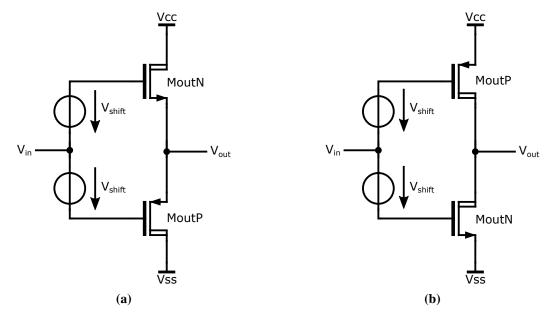

|   | 4.1 | Driver  | Stage Design                                                          | 59  |

|   |     | 4.1.1   | Requirement Analysis                                                  | 59  |

|   |     | 4.1.2   | General Approaches and Concepts                                       | 61  |

|   |     | 4.1.3   | Concept Evaluation                                                    | 62  |

|   |     | 4.1.4   | Concept of a common-source driver stage                               | 64  |

|   | 4.2 | Anti-W  | Vindup Method to Prevent Non-Linearities                              | 69  |

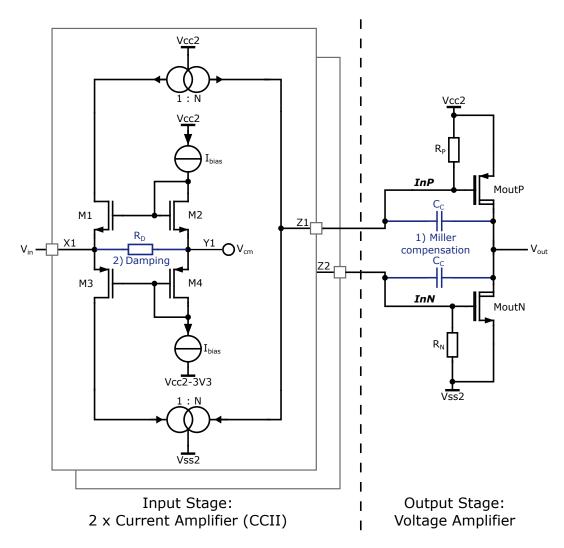

|   | 4.3 | Design  | a of the $dI_C/dt$ Feedback                                           | 75  |

|   |     | 4.3.1   | Requirement Analysis                                                  | 75  |

|   |     | 4.3.2   | Concept Evaluation                                                    | 76  |

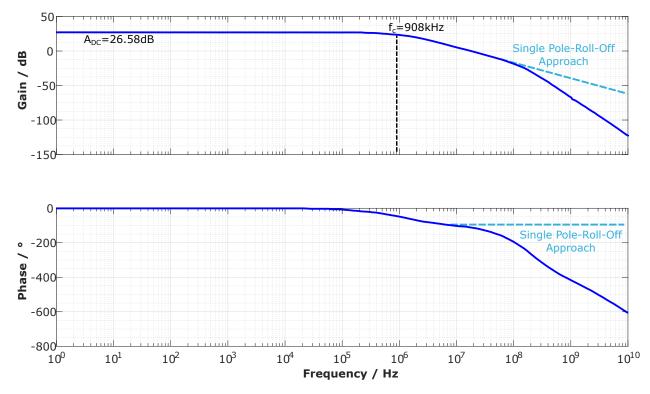

|   |     | 4.3.3   | Design and Simulation Results                                         | 77  |

|   | 4.4 | System  | Simulation Setup and Influence of Parasitics                          | 79  |

|   | 4.5 | Transie | ent Stability Analysis                                                | 82  |

|   |     | 4.5.1   | Test Bench for the Stability Analysis                                 | 82  |

|   |     | 4.5.2   | Analysis of the $dI_C/dt$ and $dV_{CE}/dt$ Control Loop               | 83  |

|   |     | 4.5.3   | Stability Improvement for the $dI_C/dt$ and $dV_{CE}/dt$ Control Loop | 85  |

|   |     | 4.5.4   | Analysis of the Anti-Windup Control Loop                              | 88  |

|   | 4.6 | Slope S | Shaping                                                               | 89  |

|   | 4.7 | Compa   | arison with Passive Gate Drivers                                      | 92  |

|   |     | 4.7.1   | Resistive Gate Driver                                                 | 94  |

|   |     | 4.7.2   | RC-compensated Gate Driver                                            | 95  |

| 5 | Con | nbined  | Digital and Analog Dual-Loop Slope Shaping                            | 97  |

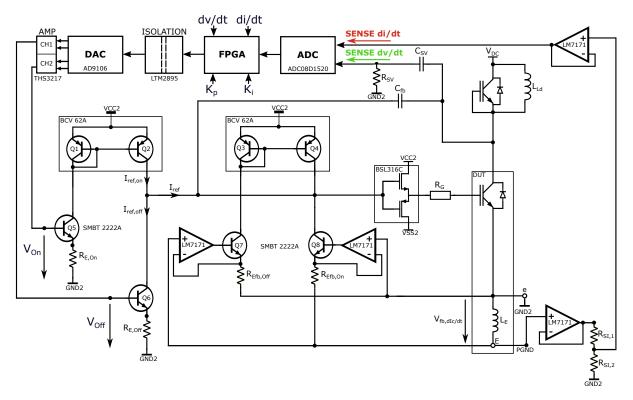

|   | 5.1 | Introdu | action and System Overview                                            | 97  |

|   | 5.2 | Analog  | g Loop                                                                | 98  |

|   |     | 5.2.1   | Analog Loop Hardware Concept                                          | 98  |

|   |     | 5.2.2   | Reference Current Source                                              | 99  |

|   |     | 5.2.3   | $dV_{CE}/dt$ Feedback                                                 | 101 |

|    |        | 5.2.4   | $dI_C/dt$ Feedback                                  | 101 |

|----|--------|---------|-----------------------------------------------------|-----|

|    |        | 5.2.5   | Base-Emitter Forward Voltage Compensation           | 102 |

|    |        | 5.2.6   | Driver Stage                                        | 103 |

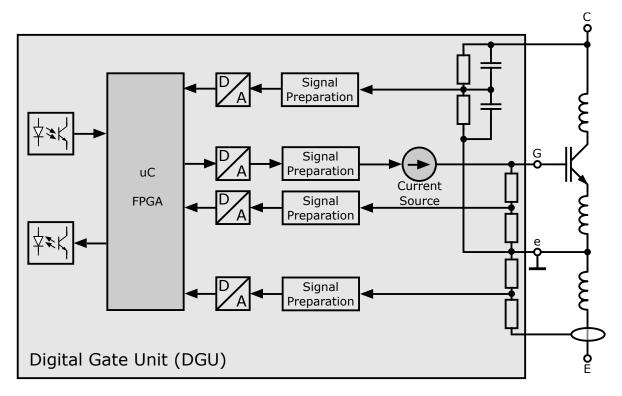

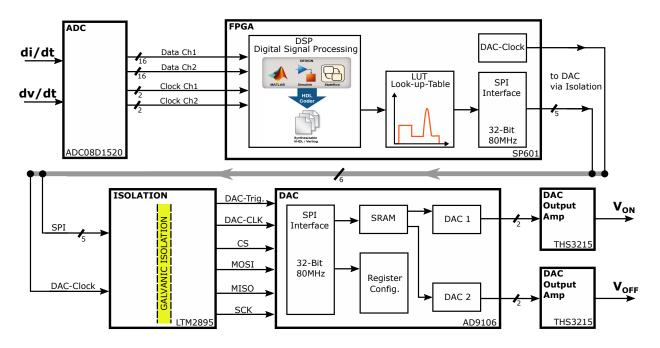

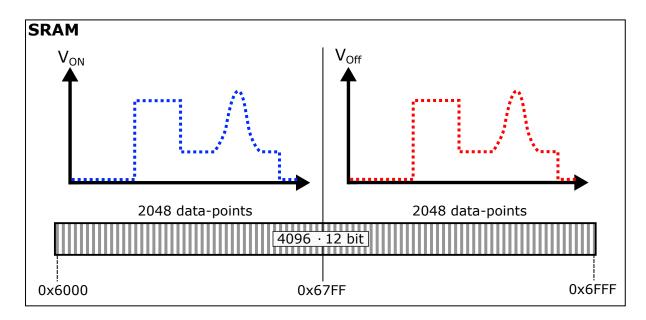

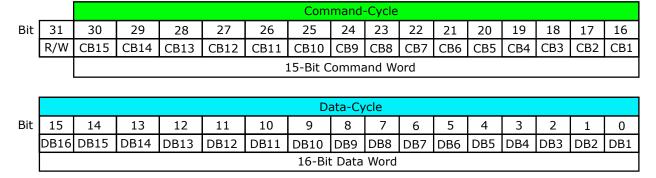

|    | 5.3    | Digital | Loop                                                | 104 |

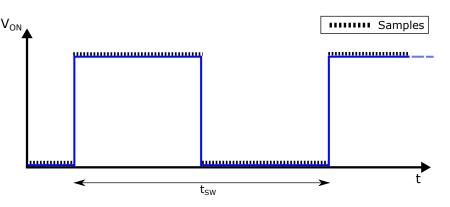

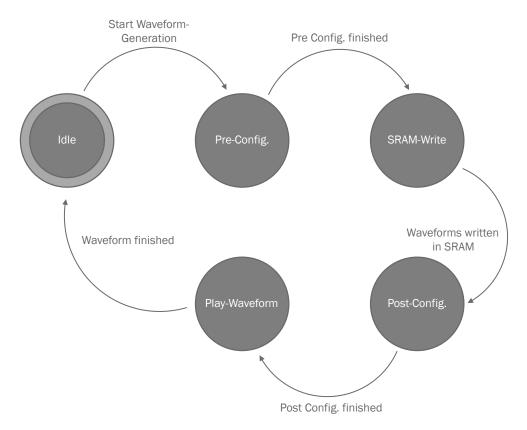

|    |        | 5.3.1   | Operating Principle                                 | 105 |

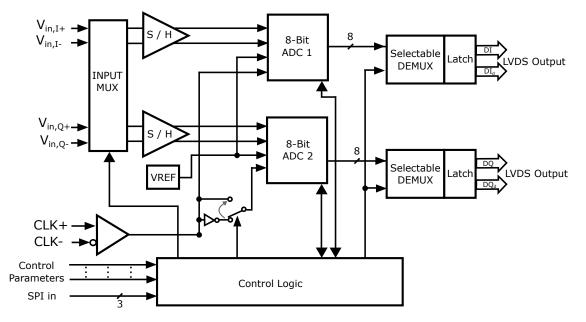

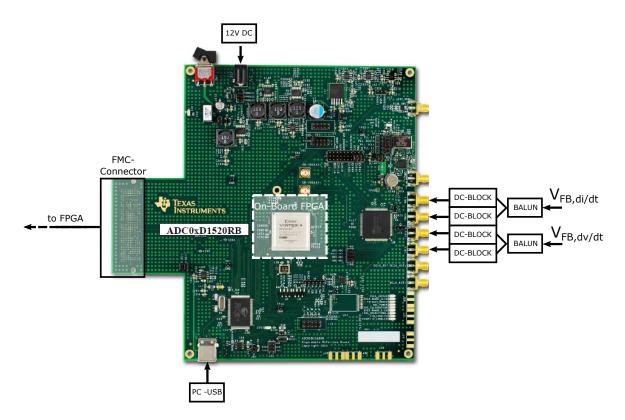

|    |        | 5.3.2   | Analog-to-Digital Converter (ADC)                   | 106 |

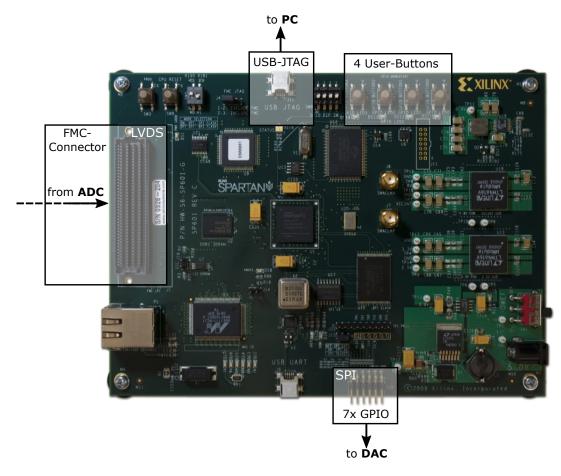

|    |        | 5.3.3   | Field-programmable Gate Array (FPGA)                | 108 |

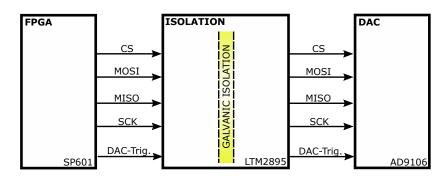

|    |        | 5.3.4   | Gate Driver Isolation                               | 109 |

|    |        | 5.3.5   | Digital-to-Analog Converter (DAC)                   | 111 |

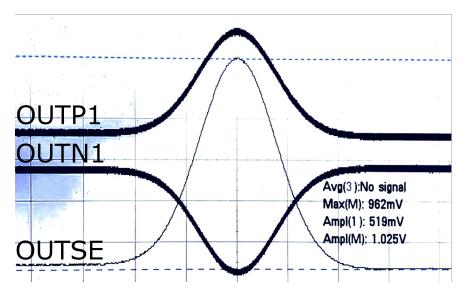

|    |        | 5.3.6   | DAC Output Amplifier                                | 114 |

|    |        | 5.3.7   | Summary                                             | 116 |

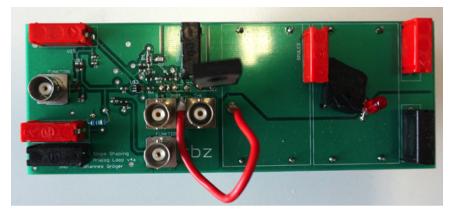

|    | 5.4    | Hardwa  | are Verification                                    | 117 |

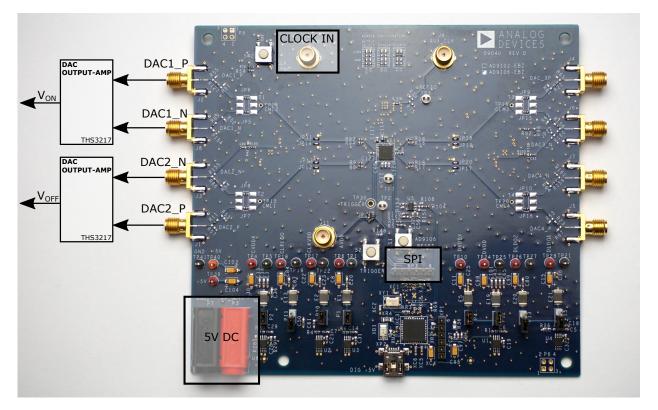

|    |        | 5.4.1   | Hardware Evaluation Module                          | 117 |

|    |        | 5.4.2   | Measurement Setup                                   | 118 |

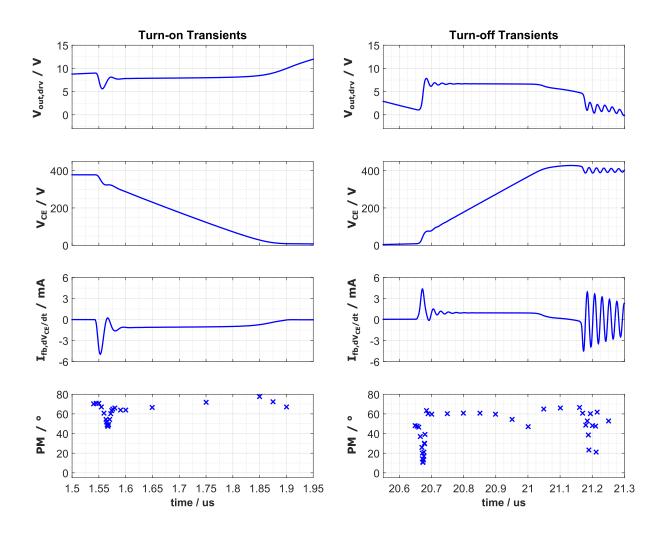

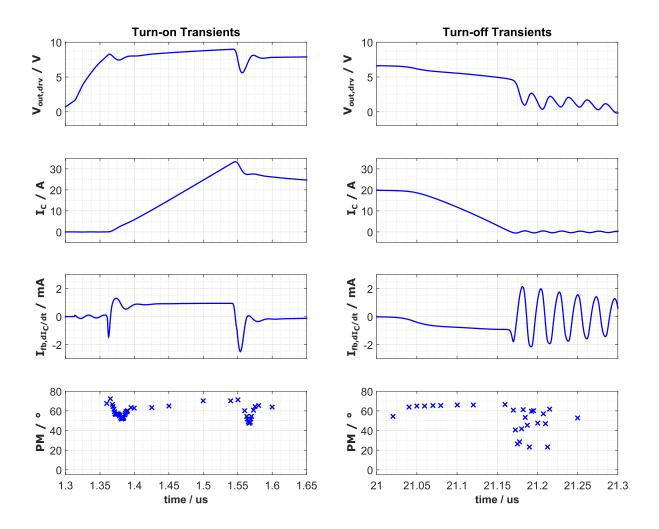

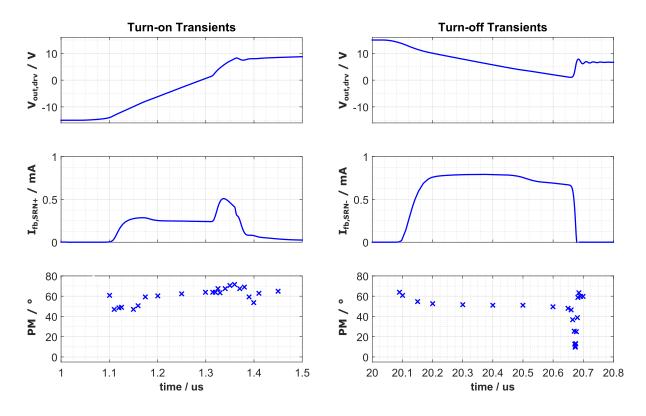

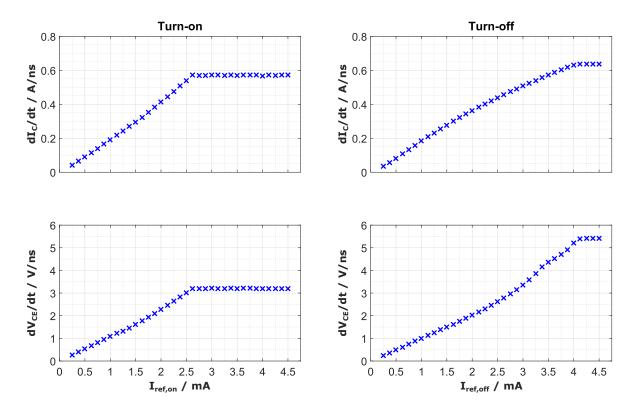

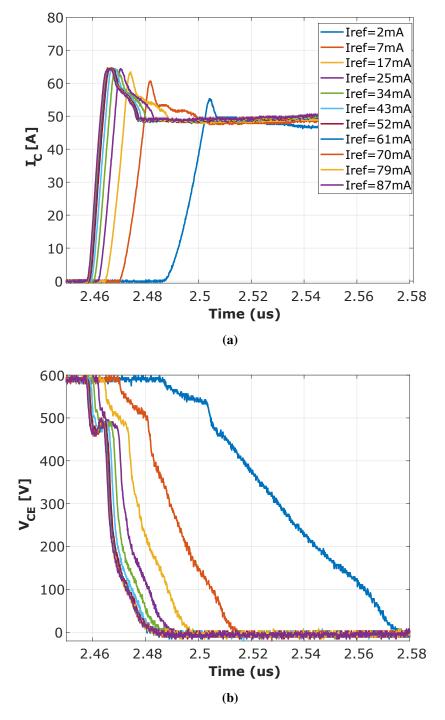

|    |        | 5.4.3   | Slew Rate Control Performance                       | 120 |

|    |        | 5.4.4   | Comparison with a Passive Gate Driver               | 120 |

|    |        | 5.4.5   | Comparison of Different Power Semiconductor Devices | 122 |

|    |        | 5.4.6   | Summary                                             | 126 |

| 6  | Con    | clusion | and Outlook                                         | 127 |

| U  | 6.1    |         |                                                     | 127 |

|    | 6.2    |         | k                                                   | 129 |

|    | 0.2    | ouroo   |                                                     | 122 |

| Bi | bliogı | raphy   |                                                     | 131 |

| Li | st of  | Abbrevi | iations                                             | 143 |

| Li | st of  | Symbol  | s                                                   | 147 |

| Li | st of  | Figures |                                                     | 151 |

| Li | st of  | Tables  |                                                     | 157 |

| A  | opend  | lix     |                                                     | 159 |

|    | А      | Additic | onal Results                                        | 159 |

|    |        | A.1     | Additional Results Class AB Source-Follower         | 159 |

|    |        | A.2     | Additional Results $dI_C/dt$ Feedback               | 162 |

|    |        | A.3     | Additional Results System Simulation                | 163 |

|    |        |         |                                                     |     |

| B SPI Interface                                 | 166 |

|-------------------------------------------------|-----|

| List of Publications, Patents, Presentations    | 168 |

| List of Student Theses Supervised by the Author | 171 |

| About the Author                                | 173 |

# **1** Introduction

# 1.1 Introduction

The development of power semiconductor devices is mainly driven by the increasing need for electrical energy. One of the strongest driver is industrial power control (IPC), along with the upward trend to electric and hybrid electric vehicles (EV/HEV) and the increasing employment of electric motors in industry applications [1]. Hence, the growth of semiconductor devices is expected to continue for the next decades [2].

Fig. 1.1: Applications in industrial power control.

Industrial power control covers the conversion of electrical energy in medium and high power industrial applications. This comprises a wide power range, from refrigerators of some hundred watts up to 50 MW

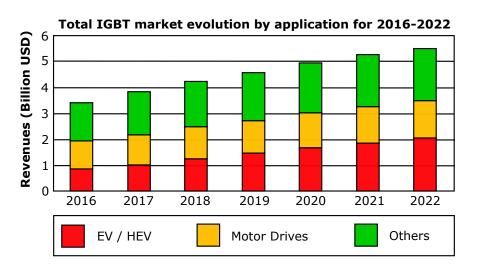

natural gas compressors [3]. Typical applications that fall into this category, depicted in Fig. 1.1, include renewable energies (photovoltaic inverters and wind power stations), home appliances (inductive cooking, dishwashers, air-conditioning, washing machines, etc.), industrial vehicles (forklifts, constructional vehicles, electric buses, etc.), rail vehicles, uninterruptable power supplies (UPS) and industrial drives (e.g. in elevators or traction motors). As an example for the continuous growth, Fig. 1.2 shows an expected market analysis for applications employing IGBTs [4], one of the standard switching components in IPC. Beside the high volume automotive sector, a further big field are motor drive applications, for which a compound annual growth rate (CAGR) of 4.6% is expected until 2022. Significant increase is also expected for further applications, such as welding or home appliances, which are labeled in green labeled as "Others".

Fig. 1.2: IGBT market evolution by application until 2022 [4].

Induced by the increasing volumes, the demand for higher efficiencies in power conversion is growing to cope with the limited energy ressources. Hence, there is a rapid development in the existing silicon-based power semiconductor technologies, such as for insulated gate bipolar transistors (IGBTs) in newest trench-/fieldstop technologies [5–8], and for metal oxide semiconductor field-effect transistors (MOSFETs) [9] [10]. Furthermore, new device technologies based on wide-bandgap (WBG) semiconductors, in particular SiC, have emerged [11–15]. These trends have lead to devices with steadily increasing switching speeds, along with lower switching losses, and therefore to higher converter efficiencies. The slew rates of modern semiconductor devices (collector-emitter/drain source voltage derivative  $dV_{CE}/dt$ , and collector/drain current derivative  $dI_C/dt$ ) may reach 100 V/ns and 1 A/ns. However, these fast voltage and current transients have turned out to be critical, as they cause violations in electromagnetic interference (EMI) and lead to extremely high voltage and current spikes, which may cause damage or even destruction of the power device [16]. In some cases, including a high amount of parasitic inductance apparent in the system, these overshoots can exceed the nominal values by more than 100%.

In motor drives, the fast switching typically leads to a fast change in the voltage across the motor terminals (high dV/dt). This can lead to destruction of the motor winding isolation due to partial discharge between the windings, and to destruction of the bearings due to displacement currents between rotor and stator [17] [18].

In order to achieve a suitable trade-off between the converter efficiency, switching delay times, EMC and SOA, gate drivers have to fulfill complex requirements [19]. The main task of gate drivers is to provide the appropriate energy to the gate of the semiconductor device in order to perform a full turn-on or turn-off transition. To achieve a desired trade-off, the transfer of charge to or from the gate has to be controlled, resulting in a limitation of the switching transients. However, conventional gate drivers have only limited technical capabilities in the independent control of both slew rates. Hence, there has been a trend to gate drivers with closed-loop slope shaping (closed-loop control of  $dI_C/dt$  and/or  $dV_{CE}/dt$ ) in recent years [20]. Closed-loop slope shaping gate drivers are either implemented as digital or analog gate drivers, which refers to the domain of the individual slew rate control design. They exhibit several advantages over conventional drivers. Closed-loop analog gate drivers offer continous-time control and, therefore, both high linearity and operating point independency, but are prone to statistical variations, leading to inaccurate control, which may not be acceptable for the fast transients of modern devices. Furthermore, their regulation parameters usually need to be tuned to a target power device to achieve control stability, which is difficult due to the inflexible analog design.

In contrast, digital gate drivers are highly flexible and accurate, as they provide programmable control parameters and employ the concept of adaptive learning. However, due to limited processing speed, they typically do not come with continous-time control, especially not for fast-switching devices. Thus, they need to be operated in cycle-by-cycle mode.

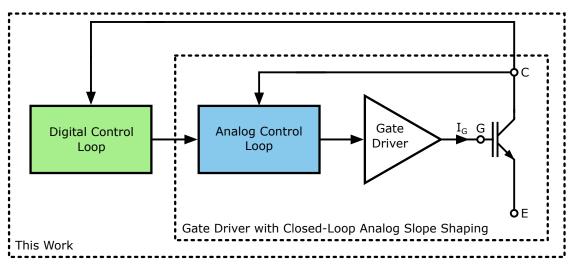

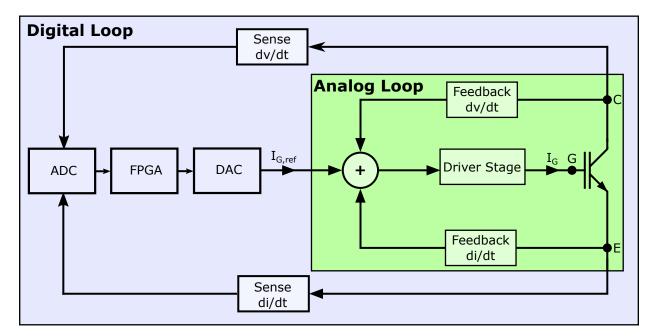

The concept pursued in this work combines the advantages of analog control and digital control in a dualloop approach. This enables precise and device-independent slope shaping, which is required to optimize the switching behavior of state-of-the-art power devices for multiple sets of application requirements.

## 1.2 Scope of this Work

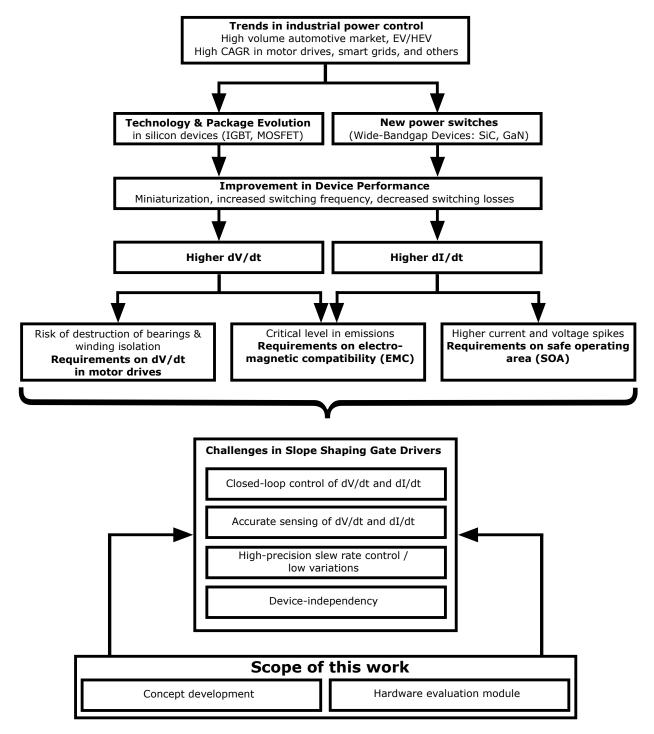

The scope of this work, based on the presented trends in industrial power control, is summarized and depicted in Fig. 1.3. The rapid evolution towards faster power switches in multiple applications continously increases the requirements on slope shaping gate drivers, due to the faster transients and larger differences in technology between the individual devices.

By combining analog and digital control in a dual-loop gate drive concept, the gate driver is able to cope with the statistical variations in the parameter set. It can establish flexible, linear and precise closed-loop control

on the switching transients, independent of the actual power device. In this regard, the main challenges are the required accuracy and bandwidth in sensing of  $dI_C/dt$  and  $dV_{CE}/dt$  for appropriate interaction between the analog and the digital loop, the required high precision in the control and to achieve stable closed-loop control independent of the power switch.

These challenges are adressed in this work as follows:

- 1. A small-signal model is created for the core blocks of the dual-loop gate driver. This is the basis for an analysis of dynamic stability. Requirements for reliable and stable control are derived.

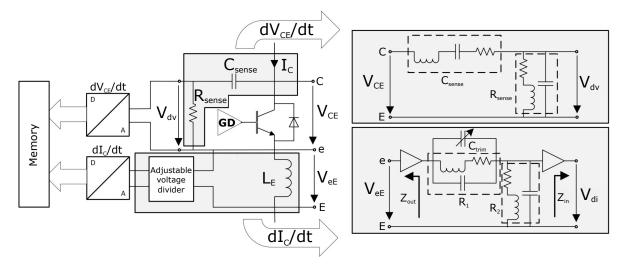

- 2. A concept for sensing of  $dI_C/dt$  and  $dV_{CE}/dt$  is developed and optimized in bandwidth and accuracy, both in theory and experimentally in hardware.

- 3. Circuit concepts for the analog and digital blocks are investigated, with respect to the requirements.

- 4. A hardware evaluation module is built up, to test and evaluate the proposed dual-loop concept in an arbitrary parameter set for different switches, and to compare it with an existing commercial gate driver.

# 1.3 Contribution of this Work

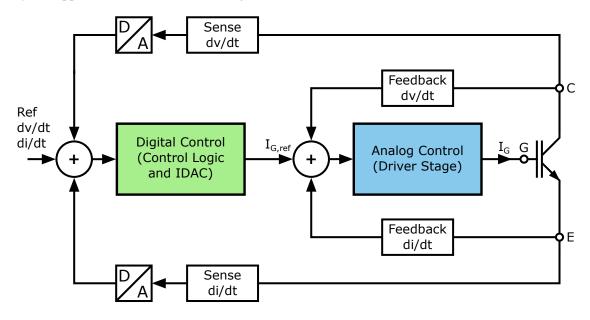

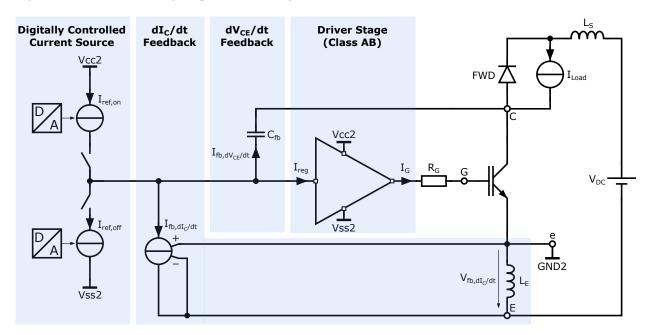

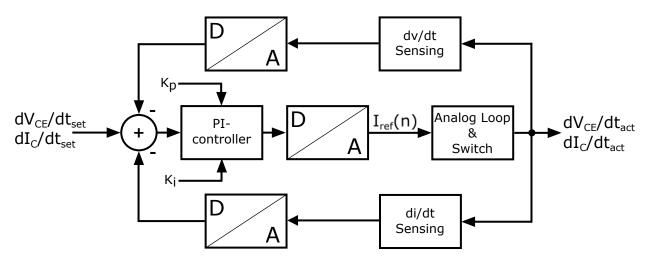

The contribution of this work is dedicated to a new hardware concept for an intelligent gate driver, that is capable of precise and device-independent slope shaping by using a dual-loop approach, combining the benefits of a closed-loop analog control with the advantages of a closed-loop digital control (see Fig. 3.1). In detail, this work advances the state-of-the-art by the following contributions:

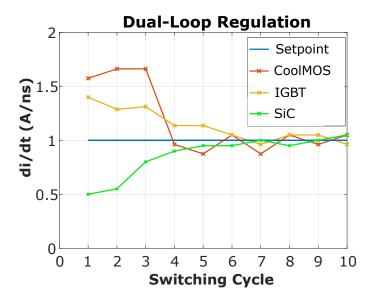

1. This work presents the first dual-loop concept in slope shaping, which consists of both analog and digital closed-loop control of  $dI_C/dt$  and  $dV_{CE}/dt$ . The concept is developed in this work. Simulations and measurements made throughout this work show that the advantages of the two domains add up together in one concept. Due to the continous-time control of the analog loop, the system exhibits high linearity in the switching transients and independency on the operating point. The digital controller adaptively compensates for statistical variations in the switching speed of the driven switch, as well as for statistical variations of the analog loop. This leads to a precise  $dV_{CE}/dt$  and  $dI_C/dt$  control, independent of the actual power device in use. The dual-loop approach has been presented at PRIME 2017 [22].

The dual-loop concept can be further extended by a new anti-windup method proposed in this thesis, that prevents the analog loop during the periods without active  $dV_{CE}/dt$  and  $dI_C/dt$  feedback, which is during the switching delay, from reaching the voltage limitation. This is required for a higher linearity

Fig. 1.3: Trends in industrial power control and scope of this work.

Fig. 1.4: This work: Dual-loop gate driver with combined digital and analog slope shaping.

in the beginning of the first transient, as it compensates for the windup-effect, which causes a nonlinearity in parts of the slew rates. In contrast to the prior art anti-windup concepts, which control the gate current during the switching delay phases, the voltage slew rate at the output of the driver  $(dV_{out,drv}/dt)$  is put in closed-loop control. Hence, the gate current level during the delay period adapts automatically if the power device is exchanged. The circuit can be designed with optional power-down switches to decrease the power consumption. The concept and circuitry referring to the anti-windup method have been filed as a patent application [23].

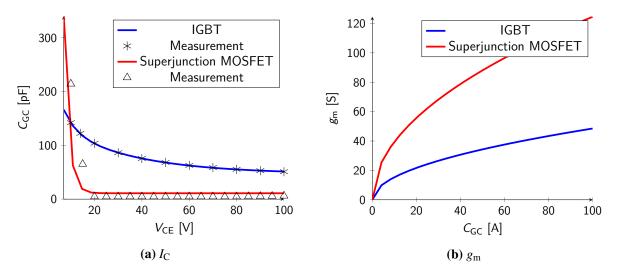

- 2. A requirement list for the slope shaping system, fitted to the application of motor drives, is provided. As part of this work, the dynamic stability of the gate driver core, represented by the analog closed-loop control of dV<sub>CE</sub>/dt and dI<sub>C</sub>/dt, is investigated in an analytical stability analysis. For this purpose, the system is paritioned into functional blocks and modeled in the small-signal domain. In advance to prior small-signal approaches in slope shaping, the created model also includes the non-linearity of parameters, which are taken into account via curve-fits on actual switch parameters. It is shown for two different power switch types, an IGBT in trench-/fieldstop technology and a Superjunction MOSFET, that control stability analysis is that the main impact on the dynamics (maximum regulation bandwidth, etc.) is determined by the power device under control. The analysis shows that major parameters of influence, which can be controlled externally, are the gate resistor, the summing node capacitance and an optional voltage gain in the driver. The analysis of dynamic stability has been presented at PRIME 2017 [22].

- 3. An optimized concept for a  $dV_{CE}/dt$  and  $dI_C/dt$  sensing circuitry is developed, which is required to guarantee for accurate interaction between the analog loop and the digital loop. In many state-of-

the-art slope shaping works, this is realized by monitoring the absolute values of  $V_{CE}$  and  $I_C$  [24]. However, better accuracy at lower DC power loss is achieved by sensing techniques for a reliable passive detection, which avoid any DC path from the high voltage network into the sensing network. The optimization of the sensing block is obtained by an experimental study based on equivalent circuit models including all relevant parasitics with effect on bandwidth and accuracy, which have been created in this work. The optimized sensing network supports all devices that exhibit fast  $dV_{CE}/dt$ and  $dI_C/dt$  up to 100 V/ns and 1 A/ns and beyond, making the sensing technique attractive for IGBTs, Superjunction MOSFETs and SiC. The sensing concept has been presented at APEC 2017 [25].

- 4. An experimental hardware evaluation module is implemented to investigate and verify the proposed circuit and system concepts. The full hardware realization of the dual-loop, in all its components, is presented in this work. The measurements demonstrate that the system is capable of the following features, advancing state-of-the-art concepts:

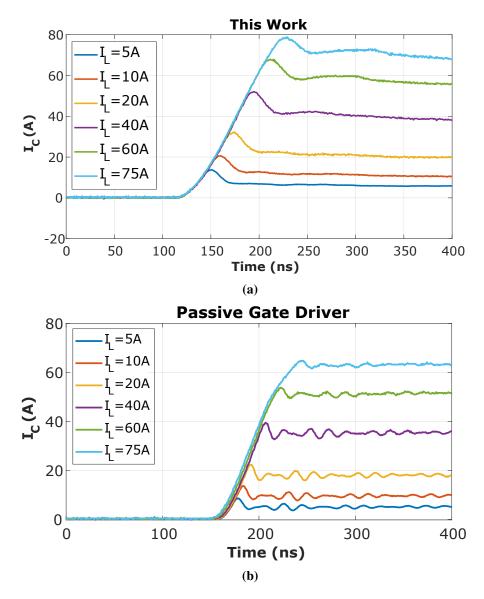

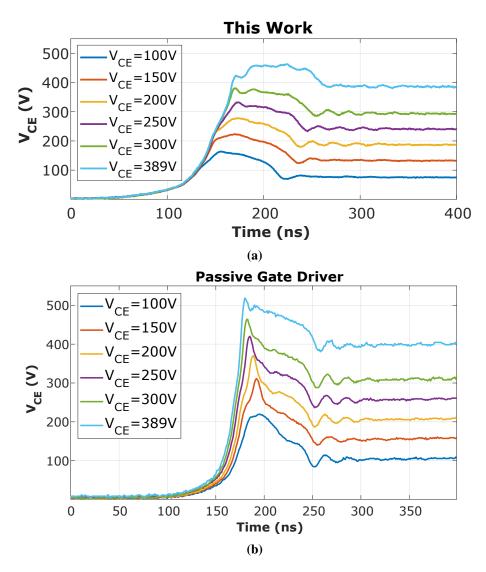

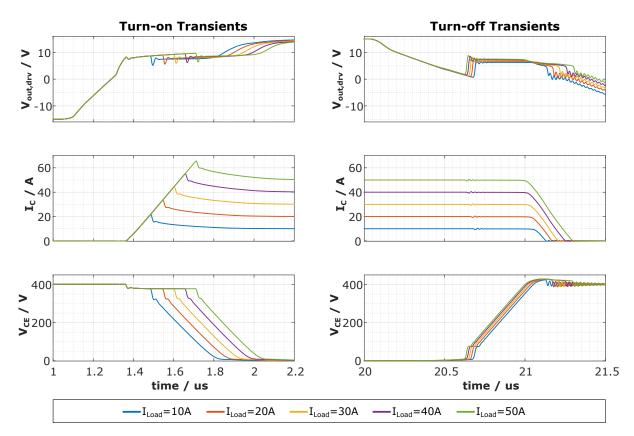

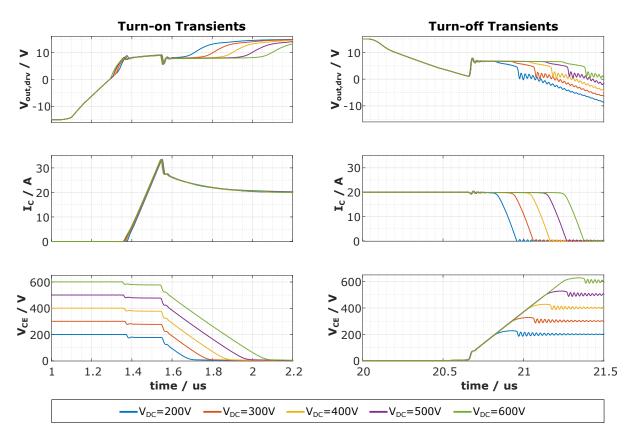

- Linear slope shaping of the voltage and current transients, independent of the actual operating point (DC link voltage and load current) and temperature, which offers the possibility to optimize the switching behavior for a given application, and during operation. This has been verified in experiment using a new generation trench-/fieldstop IGBT with 600 V and 50 A rating, for a DC link voltage range of  $V_{DC} = \{100V ... 400V\}$  and a load current range of  $I_{Load} = \{5A ... 75A\}$ .

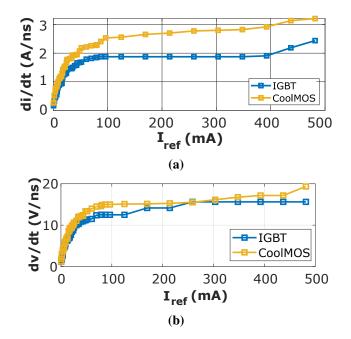

- Device-independent dV<sub>CE</sub>/dt, dI<sub>C</sub>/dt control of various modern gate-controlled power semiconductor devices, demonstrated for three state-of-the-art power switches with voltage rating up to 1200 V: Trench-/fieldstop IGBT, Superjunction MOSFET (CoolMOS<sup>TM</sup>), SiC.

- Precise and linear slew rate control due to the combination of continous-time analog and adaptive digital closed-loop control. The setpoints of  $dI_C/dt$  and/or  $dV_{CE}/dt$  can be variably adjusted during operation up to more than 2 A/ns and 10 V/ns. They are reached by the adaptive controller in less than 10 switching cycles.

## 1.4 Outline

This section describes the structure of this work in its particular chapters.

Chapter 2 starts with an introduction into the fundamentals. In the beginning, the most important state-ofthe-art power semiconductor devices are introduced and described in their key figures and applications. The switching mode of a gate-controlled device for inductive load switching, also referred to as hard switching, is described. In addition, the essential ideas and operating principles of state-of-the-art gate drive concepts with slope shaping are depicted.

The dual-loop gate driver concept with both closed-loop analog and digital  $dV_{CE}/dt$  and  $dI_C/dt$  control is investigated in Chapter 3. The first part contains an analytical small-signal stability analysis of the analog loop, which allows to derive requirements on the control parameters for stable operation. The small-signal analysis is confirmed and completed by a large-signal analysis in the transient domain. The next section elaborates the optimized sensing concept for  $dV_{CE}/dt$  and  $dI_C/dt$ . Furthermore, the digital loop concept is depicted. Based on the system specifications, requirements for the circuit blocks are derived, with the main focus on motor drive applications.

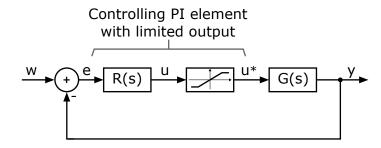

Chapter 4 presents circuit concepts for the analog loop blocks. In the beginning, two concepts for the driver stage, source follower and common-source amplifier, are analyzed. Thereafter, a method for an anti-windup, which controls the slew rate of the driver output voltage  $(dV_{out,drv}/dt)$ , is shown. Furthermore, a  $dI_C/dt$  feedback circuit for the analog closed-loop gate driver is designed.

As part of the following sections, the conceptual circuit blocks are inserted into the analog closed-loop, in order to further investigate and to verify the full functionality of the analog loop design in system simulations, which include a stability analysis and a verification of the performance parameters. In addition, the reference value of the analog control loop is varied in order to shape the switching slopes. By doing so, the minimum and maximum rates of  $dI_C/dt$  and  $dV_{CE}/dt$  are identified. In the end of the chapter, the gate driver is compared to passive gate driver concepts.

Based on the concept analysis of the previous chapters, a hardware evaluation module is built up in Chapter 5, which comprises the full dual-loop slope shaping system. A discrete hardware design for the analog loop blocks is created, adressing the circuit concepts of Chapter 4. Afterwards, hardware for the digital loop is presented and connected to the analog loop. Measurement results prove the performance of the dual-loop gate driver, demonstrate the control of different power switches and compare the dual-loop gate driver with a commercial passive gate driver.

This work concludes with a summary and an outlook.

# 2 Fundamentals

# 2.1 Devices and Circuits in Power Electronics

#### 2.1.1 Modern Generation Power Semiconductor Devices

Each application in power electronics comes along with individual requirements, which are the basis for a selection of a specific power semiconductor device, to achieve a reliable and robust behavior. Four different types of commercially available products, which exhibit an insulated gate electrode and can therefore be controlled by gate drivers, are listed in Table 2.1. The insulated gate bipolar transistor (IGBT) has become the standard switching component for lower or medium switching frequencies at high power densities [26]. IGBTs are able to cope with much higher power up to 6500 V and 3600 A, if they are used in modules. Due to their bipolar nature, they do not exhibit ohmic behavior when turned-on ( $R_{DS,on}$ ), which leads to comparably lower on-state losses.

If the application demands for a higher switching frequency, Superjunction MOSFETs are employed. However, the silicon-based power MOSFETs are limited in power handling capability [27].

|                          | <b>V</b> 1                                   |                                                    | -                                   |                              |

|--------------------------|----------------------------------------------|----------------------------------------------------|-------------------------------------|------------------------------|

|                          | IGBT Discretes                               | IGBT Modules                                       | CoolMOS <sup>TM</sup>               | OPTIMOS <sup>TM</sup>        |

| $V_{max}$ / V            | 600 - 1200                                   | 400 - 6500                                         | 500 - 950                           | 30 - 250                     |

| Inom / A                 | up to 120                                    | up to 3600                                         | up to 100                           | up to 300                    |

| $f_{SW}$ / kHz           | up to 60                                     | up to 20                                           | up to 200                           | >100                         |

| $Q_G$ / nC               | 9 - 772                                      | up to 10000                                        | 20 - 240                            | 5 - 252                      |

| $R_{DS,on}$ / m $\Omega$ |                                              |                                                    | 17 - 6000                           | 0.4 - 400                    |

| Applications             | Motor Drives,<br>Solar Inverters,<br>Welding | Motor Drives,<br>Solar Inverters,<br>Wind Turbines | PFC stages,<br>Computing,<br>Server | Audio Amps,<br>SMPS, Telecom |

|                          |                                              |                                                    |                                     |                              |

Tab. 2.1: Typical key performance parameters of modern commercial power semiconductor devices.

In recent years, the CoolMOS<sup>TM</sup> has become the leading product in the group of Superjunction MOSFETs. These switches withstand high voltages (from 500 to 950 V) when kept at low to medium currents (up to 100

A). At lower voltages, medium-voltage devices can be utilized, for instance the Infineon OPTIMOS<sup>TM</sup>. In recent years, new wide-bandgap (WBG) devices have emerged to attack the market of the classical silicon-based applications. Table 2.2 compares the two most important technologies, silicon carbide (SiC) and gallium nitride (GaN).

|                       | SiC        | GaN       |

|-----------------------|------------|-----------|

| $V_{max}/V$           | 60 - 1700  | 100 - 650 |

| $I_{nom}/A$           | up to 225  | up to 120 |

| <i>f<sub>sw</sub></i> | >100 kHz   | >100 MHz  |

| $Q_G/nC$              | 5.6 - 406  | 1.5 - 18  |

| $R_{DS,on}/m\Omega$   | 3.1 - 1150 | 5 - 150   |

| Power/W               | 35 - 520   | 55 - 125  |

Tab. 2.2: Key performance parameters of WBG power devices.

The SiC technology is able to carry much higher power densities compared to silicon-based MOSFETs and is expected to advance to the IGBT power range. Hence, SiC switches can be utilized in classical IGBT applications to yield much lower switching losses and the lowest  $R_{DS,on}$  in its corresponding voltage class. In contrast, GaN is extending the power density and frequency range of silicon MOSFETs, making them more suitable for use in Superjunction MOSFET applications.

#### 2.1.2 Half-Bridge Circuits in Electrical Converters

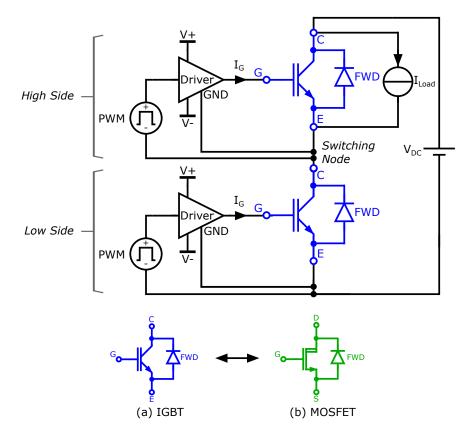

The fundamental block in electrical converters is a half-bridge. It consists of two power devices acting as switches, which are referred to as low side and high side. A half-bridge forms the basic element of any converter stage. Multiple bridges can be combined to achieve different power electronic topologies, such as e.g. H-bridges or three-phase inverters. Figure 2.1 shows a half-bridge consisting of (a) IGBTs or (b) MOSFETs. The high side can establish a low-ohmic connection to the supply voltage  $V_{DC}$ , which is referred to as the DC link voltage, when it is turned on. The low side connects the output switching node to the ground reference.

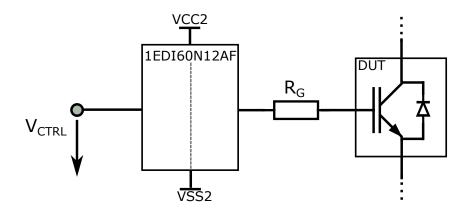

Both high side and low side are turned on and off by gate drivers, that are usually controlled by pulse-width modulation (PWM) signals. The gate driver is responsible to deliver the required gate charge ( $Q_G$ ) of the switch in order to establish the gate-source voltage (gate-emitter voltage for IGBTs) needed to fully turn on the device, and to remove the same amount of charge during the turn-off event. Some drivers also involve a negative supply voltage to enable a faster discharging of the gate during turn-off, which is especially important if the device exhibits a large gate charge  $Q_G$ , as for instance in larger IGBT modules. The use

of a negative gate voltage further prevents an undesired parasitic turn-on when the device is fully turned off [28].

**Fig. 2.1:** Typical half bridge power stage as used in various kinds of electrical converters, realized with (a) IGBTs and (b) MOSFETs.

# 2.2 Switching Behavior of Gate-Controlled Devices

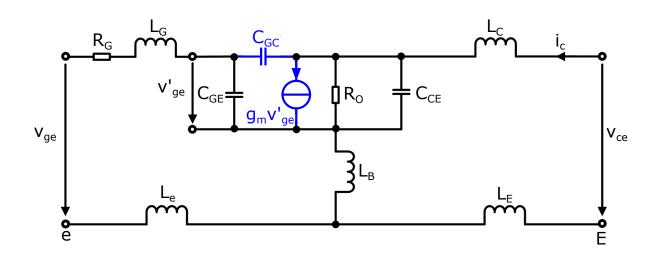

### 2.2.1 Equivalent Circuit for the Switching Dynamics

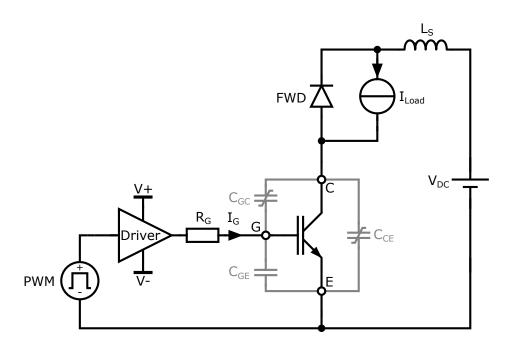

To understand the dynamics in the switching transition of a power transistor, parasitics in the switch and in the half bridge circuit need to be taken into account. Figure 2.2 shows an equivalent circuit for a test setup, used for analysis of the switching behavior. The model, which is based on [29], adds parasitics to the half-bridge schematic from Fig. 2.1 ( $C_{GE}$ ,  $C_{GC}$ ,  $C_{CE}$ , $L_S$ ). Furthermore, the high side stays turned off, such that only the free-wheeling diode (FWD) is apparent, while the low side is turned on and off. This structure serves as a basis for the description of the switching behavior, and also for later investigations on the dualloop control concept. The circuit employs a resistive push-pull gate driver, which provides either a negative or a positive output voltage. The gate current and, consequently, the rates of  $dI_C/dt$  and  $dV_{CE}/dt$  are defined by the size of the gate resistor  $R_G$ . The DC link voltage  $V_{DC}$  and the load current  $I_{Load}$ , which represents

Fig. 2.2: Equivalent circuit for hard switching of the low-side IGBT including parasitics.

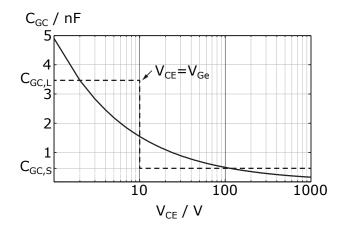

the current impressed by the inductive load, are assumed to be constant within the switching period. The stray inductance  $L_S$  represents the sum of all the parasitic inductances in the commutation loop (e.g. DC link, busbars, device lead inductances) [30] [31]. The parasitic device capacitances  $C_{GE}$ ,  $C_{GC}$  and  $C_{CE}$  are considered as well.  $C_{GC}$  and  $C_{CE}$  are strongly non-linear and depend mainly on  $V_{CE}$ . Figure 2.3 shows the typical voltage dependency of  $C_{GC}$  for a 1.2 kV IGBT. The dashed line indicates the approximation of  $C_{GC,L}$  for small values of  $V_{CE}$  lower than the gate-emitter voltage ( $V_{CE} < V_{Ge}$ ) and  $C_{GC,S}$  for higher values of  $V_{CE}$  ( $> V_{Ge}$ ) [32].

Fig. 2.3: Typical voltage dependency of the Miller capacitance  $C_{GC}$  [32].

The capacitances of a power switch are typically defined in datasheets as follows :

Input capacitance:

$$C_{\rm iss} = C_{\rm GE} + C_{\rm GC}$$

(2.1)

Output capacitance:

$$C_{\rm OSS} = C_{\rm GC} + C_{\rm CE}$$

(2.2)

Reverse transfer capacitance:

$$C_{\rm rss} = C_{\rm GC}$$

(2.3)

Beside the gate resistance, these parasitic capacitances have the main impact on the switching transients. In particular,  $C_{GE}$  influences  $dI_C/dt$  and  $C_{GC}$  influences  $dV_{CE}/dt$ , as will be derived and demonstrated in the following Sect. 2.2.2, cf. Eq. (2.6) and Eq. (2.10). Therefore, these parameters are essential and need to be included into the plant models for an appropriate design of a closed-loop  $dV_{CE}/dt$  and  $dI_C/dt$  control, which will be discussed in more detail in Sect. 3.3.

#### 2.2.2 Turn-on Switching Behavior

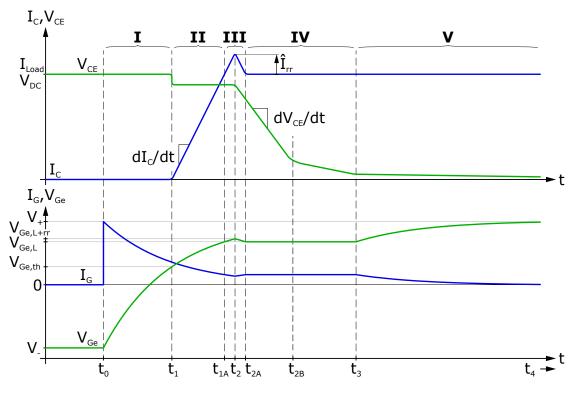

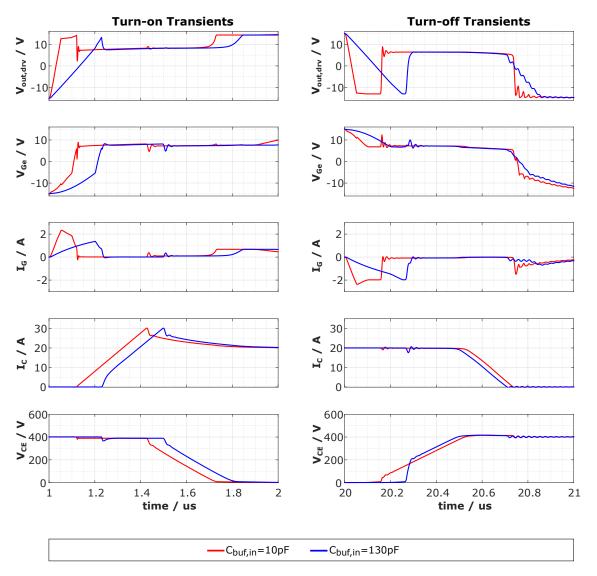

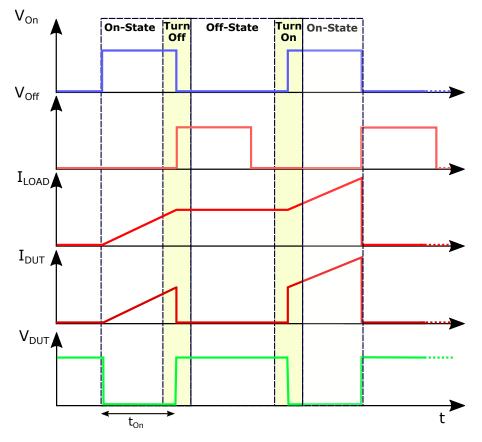

During turn-on, the load current  $I_{\text{Load}}$  commutates from the freewheeling diode to the power switch and the blocking voltages transits from the power switch to the diode [33]. The waveforms of  $V_{\text{CE}}$ ,  $I_{\text{C}}$ ,  $V_{\text{Ge}}$  and  $I_{\text{G}}$  during turn-on are shown in Fig. 2.4. The turn-on is subdivided into the intervals I-V which are described below.

### I: Gate charge delay $(t_0 < t < t_1)$

The turn-on is initiated by the gate driver at  $t = t_0$ , by applying a voltage step from  $V_{out,drv} = V_-$  to  $V_{out,drv} = V_+$ . Accordingly, the input capacitance of the power switch is charged. As a resistive gate driver is used, this process relates to the charging of a *RC*-lowpass, where *R* equals the gate resistor  $R_G$  and *C* is formed by the input capacitance  $C_{iss}$ . The turn-on gate charge delay (time until the threshold voltage  $V_{Ge,th}$  is reached and the collector current starts to rise) for a resistive gate driver can be calculated as

$$t_{\rm d,Gc} = t_1 - t_0 = R_{\rm G} \cdot C_{\rm iss} \cdot \ln\left(\frac{\Delta V_{\rm out,drv}}{V_+ - V_{\rm Ge,th}}\right).$$

(2.4)

## II: Current rise $(t_1 < t < t_{1A})$

At  $t > t_1$ , the gate voltage  $V_{\text{Ge}}$  is above the threshold voltage  $V_{\text{Ge,th}}$ . Therefore, the load current starts to commutate from the freewheeling diode to the power switch. As the power switch is operated in the active

Fig. 2.4: Turn-on transients for inductive load switching.

region, the collector current (drain current in case of a MOSFET) is defined as

$$I_{\rm C}(t) = g_{\rm m} \cdot (V_{\rm Ge}(t) - V_{\rm Ge,th}).$$

(2.5)

From Eq. (2.5), collector current slew rate can be calculated as a function of the gate current,

$$\frac{\mathrm{d}I_{\mathrm{C}}}{\mathrm{d}t} = g_{\mathrm{m}} \cdot \frac{\mathrm{d}V_{\mathrm{Ge}}}{\mathrm{d}t} = g_{\mathrm{m}} \cdot \frac{I_{\mathrm{G}}}{C_{\mathrm{iss}}} \approx g_{\mathrm{m}} \cdot \frac{I_{\mathrm{G}}}{C_{\mathrm{GE}}}.$$

(2.6)

In a typical power switch, the transconductance  $g_m$  strongly depends on the operating point. Hence,  $dI_C/dt$  is not constant during the switching phase in a conventional gate driver. Table 2.3 compares values for  $dI_C/dt$  in different commercial IGBTs, two discretes and two modules, for an injected gate current of  $I_G = 50$  mA during the  $dI_C/dt$  transient. The slew rate depends on the device input capacitance. Therefore,  $dI_C/dt$  decreases for larger devices if the same gate driver strength is used. As the rising collector current flows through the stray inductance  $L_S$ , a voltage is induced over  $L_S$  which reduces the voltage drop over the power switch,

$$V_{\rm CE} = V_{\rm DC} - L_{\rm S} \cdot \frac{\mathrm{d}I_{\rm C}}{\mathrm{d}t}.$$

(2.7)

According to Eq. (2.7), this leads to an overlap of the subsequent current and voltage transition, as there is a voltage drop, and therefore non-zero  $dV_{CE}/dt$ , during the current transition, as indicated in Fig. 2.4.

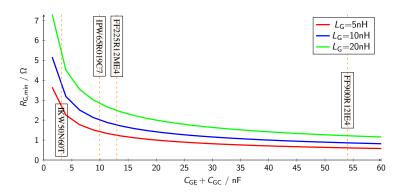

**Tab. 2.3:** Typical values for  $dI_C/dt$  for commercial switches, calculated using Eq. (2.6), assuming  $I_G = 50$  mA during the  $dI_C/dt$  transition. Values are taken out of the corresponding datasheets.

|             |               |               |               |                | _                    | -                        |

|-------------|---------------|---------------|---------------|----------------|----------------------|--------------------------|

| Device      | Туре          | $V_{max}$ / V | $I_{nom}$ / A | $g_{ m m}$ / S | C <sub>GE</sub> / pF | $dI_{\rm C}/dt$ / [A/ns] |

| IKW50N60T   | Discrete IGBT | 600           | 50            | 31             | 3047                 | 0.67                     |

| IKW50N65NH5 | Discrete IGBT | 650           | 50            | 62             | 2989                 | 1.04                     |

| FF225R12ME4 | IGBT Module   | 1200          | 225           | 105            | 13000                | 0.40                     |

| FF900R12IE4 | IGBT Module   | 1200          | 900           | 445            | 54000                | 0.41                     |

|             |               |               |               |                |                      | 1                        |

However, the subsequent occurence is the basis for the small-signal approach in Sect. 3.3. Therefore, the stray inductance must be kept small to enable individual control of  $dI_C/dt$  and  $dV_{CE}/dt$ .

### III: Reverse recovery of the diode $(t_{1A} < t < t_{2A})$

$I_{\rm C}$  reaches the load current level  $I_{\rm Load}$  at  $t = t_{1A}$ . The diode current reverses its polarity and the reverse recovery process starts. This means that the stored charge  $Q_{\rm rr}$  in the diode is actively removed. As a consequence, the collector current exhibits an overshoot with the peak reverse recovery current  $\hat{I}_{\rm rr}$ . Assuming a symmetrical triangular-shaped reverse recovery approximation [34], the peak reverse recovery current can be expressed as

$$\hat{I}_{\rm rr} = \sqrt{\mathcal{Q}_{\rm rr} \cdot \frac{\mathrm{d}I_{\rm C}}{\mathrm{d}t}}.$$

(2.8)

At  $t = t_2$ ,  $I_C$  reaches its maximum and the diode gains voltage blocking capability. Therefore, the collectoremitter voltage of the power switch starts to decay.

### IV: Voltage decay ( $t_{2A} < t < t_3$ )

While the power switch remains in the active region, the collector current continues at  $I_{\text{Load}}$ . According to Eq. (2.5), the gate voltage stays at  $V_{\text{Ge,L}}$ ,

$$V_{\rm Ge}|_{I_{\rm C}=I_{\rm Load}} = V_{\rm Ge,L} = V_{\rm Ge,th} + \frac{I_{\rm Load}}{g_{\rm m}}.$$

(2.9)

This constant level of gate voltage during turn-on, which also occurs during turn-off is referred to as *Miller Plateau*. The gate current is almost constant during this interval, as it only discharges the Miller capacitance

$C_{\text{GC}}$ . Accordingly, the decay of the collector-emitter voltage can be described as

$$\frac{\mathrm{d}V_{\mathrm{CE}}}{\mathrm{d}t} = -\frac{\mathrm{d}V_{\mathrm{GC}}}{\mathrm{d}t} = -\frac{I_{\mathrm{G}}}{C_{\mathrm{GC,S}}}.$$

(2.10)

Table 2.4 compares values for  $dV_{CE}/dt$  in different commercial IGBTs, two discretes and two modules, for an injected gate current of  $I_{G} = 100$  mA during the  $dV_{CE}/dt$  transient. The Miller capacitance  $C_{GC}$  shows

**Tab. 2.4:** Typical values for  $dV_{CE}/dt$  for commercial switches, calculated using Eq. (2.10), assuming  $I_{G} = 100 \text{ mA}$  during the  $dV_{CE}/dt$  transition. Values are taken out of the corresponding datasheets.

| Device      | Туре          | $V_{max}$ / V | Inom / A | <i>C</i> <sub>GC</sub> / pF | $ dV_{\rm CE}/dt $ / [V/ns] |

|-------------|---------------|---------------|----------|-----------------------------|-----------------------------|

| IKW50N60T   | Discrete IGBT | 600           | 50       | 93                          | 1.07                        |

| IKW50N65NH5 | Discrete IGBT | 650           | 50       | 11                          | 9.09                        |

|             |               | 1000          | 225      | <b>7</b> 0 <i>5</i>         |                             |

| FF225R12ME4 | IGBT Module   | 1200          | 225      | 705                         | 0.14                        |

| FF900R12IE4 | IGBT Module   | 1200          | 900      | 3000                        | 0.03                        |

a non-linear dependency on  $V_{CE}$  as shown in Fig. 2.3. At  $t = t_{2B}$ ,  $V_{CE}$  reaches a value close to  $V_{Ge}$ . This leads to a very small  $dV_{CE}/dt$  according to Eq. (2.10), as  $C_{GC}$  increases strongly and the gate current stays constant during this period.

## V: Gate charge $(t_3 < t < t_4)$

Once the power switch transits from the active region into the saturation region, the gate is no longer clamped and the gate driver continues charging of the input capacitance. After this interval, the device is fully turned-on.

#### 2.2.3 Turn-off Switching Behavior

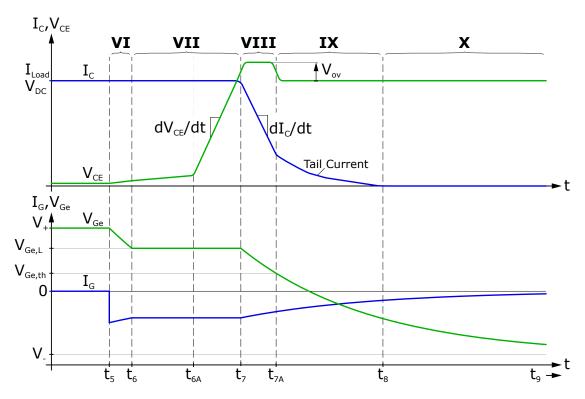

During turn-off, the load current  $I_{\text{Load}}$  commutates from the power switch to the freewheeling diode and the DC link voltage drop transits from the diode to the power switch. The waveforms of  $V_{\text{CE}}$ ,  $I_{\text{C}}$ ,  $V_{\text{Ge}}$  and  $I_{\text{G}}$  during turn-off are shown in Fig. 2.5 in a similar way as for turn-on. In particular, the switching transients are inversed compared to turn-on, except for the reverse recovery behavior. The turn-off is subdivided into the intervals VI-X, which are described below.

Fig. 2.5: Turn-off transients for inductive load switching.

## VI: Gate discharge delay $(t_5 < t < t_6)$

The turn-off is initiated by the gate driver at  $t = t_5$ , by applying a voltage step from  $V_{\text{out,drv}} = V_+$  to  $V_{\text{out,drv}} = V_-$ . The gate voltage at off-state is often negative to prevent a parasitic turn-on for large values of  $dV_{\text{CE}}/dt$ .

According to the voltage step, the input capacitance of the power switch is discharged with an *RC*-behavior. The gate current performs a step to its minimum value and starts to rise. The gate discharge delay until the power switch enters the active region can be calculated as

$$t_{\rm d,Gd} = t_6 - t_5 = R_{\rm G} \cdot C_{\rm iss} \cdot \ln\left(\frac{\Delta V_{\rm out,drv}}{V_{\rm Ge,L} - V_{-}}\right).$$

(2.11)

## VII: Voltage rise ( $t_6 < t < t_7$ )

The power switch enters the active region and  $V_{\text{Ge}}$  reaches the Miller Plateau  $V_{\text{Ge,L}}$  (see Eq. (2.9)). A constant gate current charges the Miller capacitance, which is large due to the low value of  $V_{\text{CE}}$  (see Fig. 2.3). At  $t_{6A}$ , the collector-emitter voltage reaches  $V_{\text{Ge}}$ , which leads to a strong decrease in  $C_{\text{GC}}$ . Therefore,  $V_{\text{CE}}$  starts to rise very fast with  $dV_{\text{CE}}/dt$  according to interval IV at turn-on (see Eq. (2.10)). The additional

delay prior to  $t_{6A}$  caused by the large Miller capacitance can be calculated as

$$t_{\rm d,GC} = t_{6A} - t_6 = (V_{\rm CE,sat} - V_{\rm Ge,L}) \cdot \frac{C_{\rm GC,L}}{I_{\rm G}}.$$

(2.12)

## VIII: Current decay ( $t_7 < t < t_{7A}$ )

Once  $V_{CE}$  reaches the value of the DC link voltage  $V_{DC}$ , the freewheeling diode gets forward biased. Therefore, the load current starts to commutate from the power switch to the diode. The gate voltage is no longer clamped and  $C_{iss}$  is discharged like in interval VI. The amount of  $dI_C/dt$  can be calculated in a similar way as for turn-on in interval II (see Eq. (2.6)). Due to the falling collector current, flowing through the stray inductance  $L_S$ , a negative voltage is induced in  $L_S$  that leads to an overshoot in the collector-emitter voltage,

$$V_{\rm CE} = V_{\rm DC} - L_{\rm S} \cdot \frac{\mathrm{d}I_{\rm C}}{\mathrm{d}t} = V_{\rm DC} + V_{\rm OV}.$$

(2.13)

### IX: Tail current $(t_{7A} < t < t_8)$

If the switching device is an IGBT, the collector current reaches the level of the tail current at  $t = t_{7A}$ . In this period, the gate driver is no longer able to control the device. The characteristic tail is caused by minority carriers that are stored in the IGBT to reduce the voltage drop in on-state.  $V_{Ge}$  is below  $V_{Ge,th}$ , which means that the channel stops conducting. As the channel current stops, the remaining charges in the IGBT can only be removed by recombination. Therefore, the tail current highly depends on the IGBT's technology (in particular the size of the drift zone), the charge carrier lifetime and varies with the junction temperature  $T_i$  [35].

## X: Gate discharge $(t_8 < t < t_9)$

While the current decays, the gate voltage decreases down to  $V_{\text{Ge}} = V_{-}$ . The freewheeling diode is now carrying the whole load current, and the power switch is fully in blocking mode.

#### 2.2.4 Trade-offs Resulting from the Slew Rates of the Switching Transients

Setting the rate of the voltage and current slopes  $(dV_{CE}/dt \text{ and } dI_C/dt)$  in a power semiconductor device enables a trade-off between switching losses, switching delays, SOA operation and electromagnetic interference (EMI). The influence of slow or fast switching transients on these switching behavior parameters is briefly reviewed in the following.

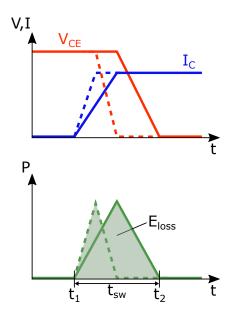

#### **Switching Losses**

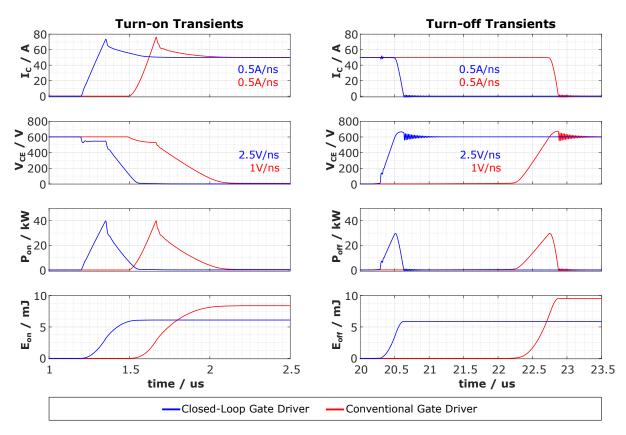

The switching losses during turn-on or turn-off result from the temporary overlap of the collector-emitter voltage  $V_{CE}$  and the collector current  $I_{C}$ . Hence, the energy loss highly depends on the transient switching waveforms. This is illustrated in Fig. 2.6.

Fig. 2.6: Switching loss caused by the current and voltage transients of an IGBT.

The energy loss during the switching time  $t_{sw}$  is given by

$$E_{\rm loss} = \int_{t_1}^{t_2} V_{\rm CE} I_{\rm C} \,\mathrm{d}t, \qquad (2.14)$$

which can be simplified to the approximation

$$E_{\rm loss} \approx 0.5 \cdot V_{\rm CE} \cdot I_{\rm C} \cdot t_{sw}, \tag{2.15}$$

as the multiplication of  $V_{CE}$  and  $I_C$  results in a triangular shaped waveform over time. (2.15) The switching losses depend strongly on the switching time  $t_{sw}$ , which is defined by the amount of  $V_{CE}$  and  $I_C$ . Hence, fast switching transistions are preferred, if high efficiency is the major design goal.

### Switching Delay

The switching delay time indicates the interval from triggering the turn-on or turn-off until the switching transients start to rise. These delays should be kept as small as possible because they act as phase shift

between the actual PWM control signal and the generated output current and voltage waveform. A large delay could lead to a minor bandwidth and a reduced phase margin of the superordinate control of the power electronic system (e.g. field-oriented control of an electric motor). The delay during turn-on is given by the time period for charging the gate to threshold level  $V_{\text{Ge,th}}$  (see Eq. (2.4)). The turn-off switching delay is defined by the discharging of the gate to Miller Plateau level (Eq. (2.11)) and by charging the large Miller capacitance to the gate voltage level (Eq. (2.12)). The turn-on and turn-off delay mainly depend on the size of the gate resistor and the gate current. Hence, fast switching (low gate resistor and high gate current) is preferred for short turn-on and turn-off switching delays.

| Device      | Туре          | $V_{max}$ / V | $I_{nom}$ / A | $t_{\rm d,Gc}$ / ns | $t_{\rm d,Gd}$ / ns |

|-------------|---------------|---------------|---------------|---------------------|---------------------|

| IKW50N60T   | Discrete IGBT | 600           | 50            | 26                  | 299                 |

| IKW50N65NH5 | Discrete IGBT | 650           | 50            | 21                  | 180                 |

|             |               |               |               |                     |                     |

| FF225R12ME4 | IGBT Module   | 1200          | 225           | 160                 | 380                 |

| FF900R12IE4 | IGBT Module   | 1200          | 900           | 200                 | 660                 |

Tab. 2.5: Typical turn-on and turn-off delay values of different IGBTs (datasheets values).

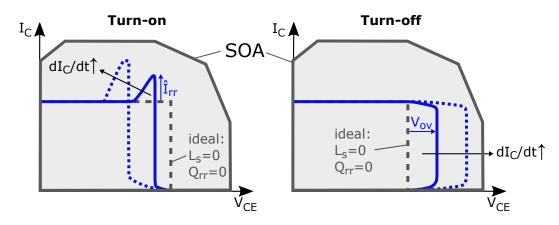

## Safe Operating Area (SOA)

Fast switching is beneficial in terms of low switching losses and small switching delay times. However, a fast collector current transient leads to an increased peak reverse recovery current during turn-on (Eq. (2.8)) and to a higher overvoltage during turn-off (Eq. (2.13)). These individual peaks in power loss need to be maintained within certain limits defined by the safe operating area (SOA). The boundaries, which are determined by properties of the semiconductor material, are shown schematically in Fig. 2.7 together with the switching trajectories of different speeds. These SOA diagrams, which depict the specific limits in  $I_{\rm C}$  and  $V_{\rm CE}$  at a specific gate-emitter voltage  $V_{\rm Ge}$ , are typically shown in the device datasheets.

Hence, the switching speed of the device has to be decreased to such a level, that operation in the SOA is guaranteed for the whole range of operating conditions (load current, DC link voltage and temperature). This results in increased switching losses. Furthermore, it is usually required that the devices need to be designed for a higher voltage rating than the utilized DC link voltage  $V_{DC}$ , which leads to higher parasitics and therefore to associated disadvantages such as higher delay times and losses.

- Fig. 2.7: Switching trajectories of a gate-controlled power switch considering reverse recovery during turn-on and overvoltage during turn-off inside the safe operating area. The dashed line in black represents the trajectory for an ideal commutation loop without stray inductance ( $L_S = 0$ ) and no reverse recovery ( $Q_{rr} = 0$ ).

- **Tab. 2.6:** Typical values for the reverse recovery peak current in different IGBT devices (datasheets values at specific  $dI_C/dt$ ).

| Device      | Туре          | V <sub>max</sub> / V | I <sub>nom</sub> / A | d <i>I</i> <sub>C</sub> /d <i>t</i> /<br>[A/ns] | $\hat{I}_{\rm rr}$ / A |

|-------------|---------------|----------------------|----------------------|-------------------------------------------------|------------------------|

| IKW50N60T   | Discrete IGBT | 600                  | 50                   | 1.28                                            | 27.7                   |

| IKW50N65NH5 | Discrete IGBT | 650                  | 50                   | 1.20                                            | 16.7                   |

|             |               |                      |                      |                                                 |                        |

| FF225R12ME4 | IGBT Module   | 1200                 | 225                  | 5.75                                            | 300                    |

| FF900R12IE4 | IGBT Module   | 1200                 | 900                  | 5.70                                            | 500                    |

#### **Electromagnetic Interference (EMI)**

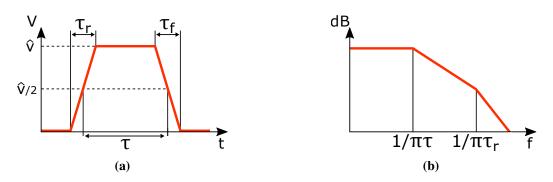

Another design aspect in power electronic systems is the EMI, which is caused by the switching transitions. EMC analysis differentiates between common mode noise and differential mode noise [36]. Thereby, the fast voltage changes ( $dV_{CE}/dt$ ) are causing common mode noise, which couples via parasitic capacitances into the supply lines. Differential noise mainly results from the fast changing load current ( $dI_C/dt$ ) in the commutation loop and from the reverse recovery of the body diode.

The electromagnetic emissions of a PWM controlled driver are typically predicted with the frequency spectrum of a trapezoidal signal [37]. For simplicity, the trapeze exhibits an equal rise time  $\tau_r$  and fall time  $\tau_f$  (see Fig. 2.8a). Employing this assumption, the emission of a trapeze signal in the frequency domain is given by

$$E_{\rm dB} = 20\log\left(2A\frac{\tau}{T}\right) + 20\log\left|\frac{\sin(\pi\tau f)}{\pi\tau f}\right| + 20\log\left|\frac{\sin(\pi\tau f)}{\pi\tau_{\rm r}f}\right|.$$

(2.16)

Fig. 2.8: (a) Trapeze in time domain (b) Trapeze in frequency domain [39].

The resulting frequency spectrum is illustrated in Fig. 2.8b. The first term of Eq. (2.16) represents a constant level of emission and is mainly influenced by the amplitude *A* of the signal and the on-time  $\tau$ . The second term marks the first breakpoint, at which the emissions decrease with 20 dB/decade. The breakpoint depends on the switching frequency *f* and  $\tau$ . As the parameters *A*, *f* and  $\tau$  are given by the application, only the third term remains for reducing the emission by the gate driver. This term represents the second breakpoint, at which the signal emissions fall with 40 dB/decade. Lowering the rise and fall times of the voltage transients shifts the second breakpoint to lower frequencies and hence reduces the emissions in the higher frequency range. The real emission spectrum differs from the illustration in Fig. 2.8b, because the  $dI_C/dt$  causes ringing, which results in additional emissions due to induced voltages in the parasitic inductances. The additional EMI, caused by  $dI_C/dt$ , generally occurs in the higher frequency spectrum. The EMI in the lower frequency spectrum has to be reduced with filters or further sophisticated techniques such as edge shaping [38], as it can usually not be influenced by the slew rates of the switching slopes [39].

#### Requirements on $dV_{CE}/dt$ in Motor Drives

The IEC 60034-17 standard defines the voltage peak limits in relation to the rise time for general purpose 500 VAC motors when fed by motor drives and IEC 60034-25 specifies the limits for motors rated 500 VAC and 690 VAC [40]. Depending on the rise time, the maximum dV/dt can be up to 5 V/ns [41]. However, most manufacturers recommend to reduce the dV/dt at the motor terminals to 1 V/ns in order to reduce the voltage stress on the motor insulation and to increase the motor's lifetime [40] [16].

Considering the reflections at the motor terminal, the achievable rates for  $dI_C/dt$  and  $dV_{CE}/dt$  of the closed-loop gate driver should be in the following ranges:

$$dI_{\rm C}/dt \approx 0.1 \text{ A/ns to } 1.0 \text{ A/ns}$$

(2.17)

$$dV_{\rm CE}/dt \approx 0.5 \, {\rm V/ns}$$

to 2.5 V/ns. (2.18)

#### **Trade-off Definition**

In summary, fast switching transitions are beneficial for low switching losses and small switching delay times. However, operation of the device within the SOA under all conditions and the compliance with EMC standards demand for decreasing the slew rates of the voltage and current slope. Table 2.7 shows an exemplary trade-off matrix for a 50 A, 600 V IGBT in a modern trench-/fieldstop technology, where  $dV_{CE}/dt$  is limited to 1 V/ns due to a given requirement, and  $dI_C/dt$  is used to limit the reverse recovery current peak  $\hat{I}_{rr}$  at turn-on and the voltage overshoot  $V_{OV}$  at turn-off. The values are calculated using the approximations in Eq. (2.8), Eq. (2.13) and Eq. (2.15). In case  $dI_C/dt$  is decreased by factor 10 (from 5 A/ns to 0.5 A/ns),  $\hat{I}_{rr}$  is decreased by 68% (95 A to 30 A) and  $V_{OV}$  by a factor of 10 for the given switch under the mentioned conditions. These exemplary calculations show that a trade-off between SOA and switching losses is possible by  $dI_C/dt$  adjustment. To achieve an appropriate trade-off between these design goals,

| IKW50N60T                                                   | $E_{loss}$ / mJ | $\hat{I}_{ m rr}$ / A | V <sub>OV</sub> / V |

|-------------------------------------------------------------|-----------------|-----------------------|---------------------|

| $\mathrm{d}I_{\mathrm{C}}/\mathrm{d}t = 0.5 \mathrm{A/ns}$  | 5               | 30                    | 50                  |

| $dI_{\rm C}/dt = 1.0  {\rm A/ns}$                           | 4.5             | 42                    | 100                 |

| $\mathrm{d}I_{\mathrm{C}}/\mathrm{d}t = 5.0 \mathrm{~A/ns}$ | 4.1             | 95                    | 500                 |

**Tab. 2.7:** Exemplary trade-off matrix for 50 A, 600 V Discrete IGBT IKW50N60T.  $V_{\text{DC}} = 400 \text{ V}, I_{\text{Load}} = 50 \text{ A}, dV_{\text{CE}}/dt = 1 \text{ V/ns}, L_{\text{S}} = 100 \text{ nH}, Q_{\text{rr}} = 1.8 \text{ }\mu\text{C}$

depending on the requirements of a specific power electronics application, gate drive concepts with slope shaping are employed, that are able to control the voltage and/or current slew rates.

There are different methods to control  $dI_C/dt$  and  $dV_{CE}/dt$  of a power semiconductor device. They are described in the following section, including their advantages and disadvantages.

# 2.3 State-of-the-Art Gate Drive Concepts

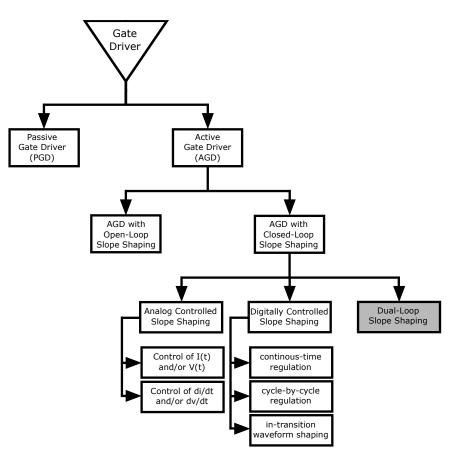

Fig. 2.9: Overview on the state-of-the-art in slope shaping gate drivers.

The gate driver is responsible for the static and dynamic switching performance of the power semiconductor device and is thus also responsible for the associated switching and conduction losses. The switching cycles of the driver are controlled by PWM signals applied by a microcontroller or comparable control units. Thereby, the driver acts as an amplifier, which amplifies the control signal by boosting the voltage and current levels to reach the desired driving capability. The main function of the gate driver is to charge and discharge the input and reverse transfer capacitance of the power switch. The total charge is referred to as gate charge [28] [42]. Figure 2.9 provides an overview of existing gate driving techniques that are able to limit or control the slew rates of current and/or voltage. In general, two basic principles can be distinguished [43]. The first group is formed by *Passive Gate Drivers* (PGDs), the second by *Active Gate Drivers* (AGDs). Active gate drivers consist of two categories, gate drivers with open-loop and gate drivers with closed-loop slope shaping. The different gate drivers are introduced in the following.

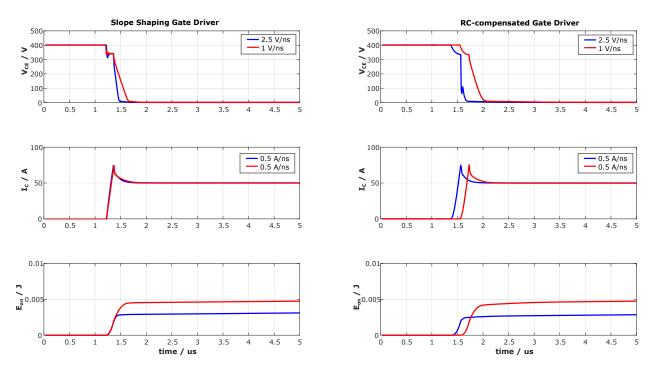

## 2.3.1 Passive Gate Drivers

Gate drivers without any kind of active control on the switching behavior during the transition are referred to as passive gate drivers (PGD). They are frequently used in today's products. In general, passive gate drivers can be subdivided into the following four gate driving schemes:

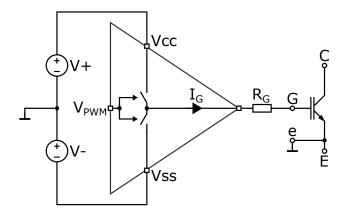

1. Voltage source gate driver with resistive  $dI_C/dt$ ,  $dV_{CE}/dt$  adjustment (hard switching driver)

Fig. 2.10: Voltage source gate driver with resistive  $dI_C/dt$ ,  $dV_{CE}/dt$  adjustment.

The driver acts like a constant voltage source, which is applied to the gate during a switching event, and the whole switching behavior (delay times,  $dI_C/dt$ ,  $dV_{CE}/dt$ ) is predefined by the external gate resistor  $R_G$  mounted to the gate. In general, a larger gate resistor  $R_G$  leads to a lower gate current  $I_G$ and therefore to lower voltage and current slopes. This approach, which is depicted in Fig. 2.10, is the most common implementation and is widely used in commercial products, as for example in the *Infineon EiceDRIVER*<sup>TM</sup> product family [44].

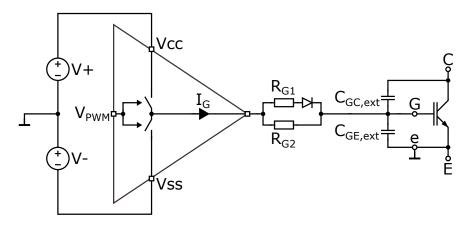

#### 2. Voltage source gate driver with individual $dI_C/dt$ and $dV_{CE}/dt$ adjustment

In contrast to the resistive driver, the mounting of external passive components to the gate is not limited to a gate resistor, but extended by further passive components, such as capacitors  $C_{GC,ext}$  and  $C_{GE,ext}$ . Hence, the switching speed can be set by the corresponding *RC* time constant. Therefore, these gate drivers are also known as RC-compensated gate drivers. Tuning of the external capacitors enables individual adjustment of  $dI_C/dt$  and  $dV_{CE}/dt$ . It is recommended to use a gate resistor in series with  $C_{GE,ext}$  to damp a possible resonant circuit consisting of the gate path inductances and gate path capacitances. However, the major drawback of this method is that the switching delay times and the gate drive losses are increased due to the larger input capacitance.

By adding an external Miller capacitance  $C_{GC,ext}$ ,  $dV_{CE}/dt$  is slowed down (see Eq. (2.10)) with only

minor impact on  $dI_C/dt$ . Using this technique, it has to be considered that the external capacitor  $C_{GC,ext}$  must provide at least the same blocking voltage capability as the device under control [28].

## 3. Voltage source gate driver with separate ON / OFF adjustment

Fig. 2.11: Voltage source gate driver with separate ON/OFF adjustment of the switching transients.

If separate control is required for turn-on and turn-off, two gate resistors can be utilized in combination with diodes according to Fig. 2.11. This allows to individually tune the switching slopes for turnon and turn-off. In the case of Fig. 2.11, the effective gate resistor during turn-on is  $R_{G,on} = R_{G1} ||R_{G2}$ and the effective gate resistor during turn-off is  $R_{G,off} = R_{G2}$ .

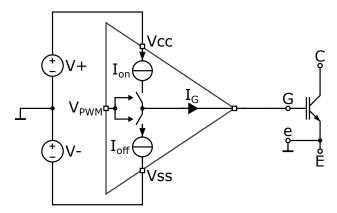

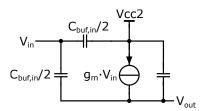

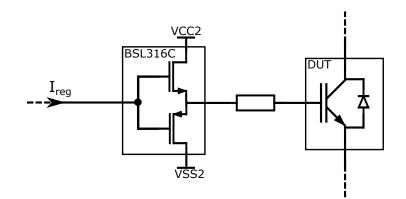

## 4. Predefined current sources

Fig. 2.12: Gate driver with predefined current sources.

The power switch and its switching behavior is directly controlled by a defined current into the gate. The driver consists of one or more current sources for positive and negative current (see Fig. 2.12). The advantage of this method is, that the gate current does not rely on a *RC*-time constant, as it is in case of voltage source drivers. Therefore, the rates of  $dV_{CE}/dt$  and  $dI_C/dt$  can be directly controlled in feed-forward configuration. The disadvantage is mainly that the power losses generated by the driving current are dissipated in the current source within the driver and not in the gate resistor as for voltage source drivers [28].

Although the passive approach includes concepts that allow for individual tuning of the voltage and current transients, and therefore scaling of the switching losses, there are a couple of limitations. Passive gate drive concepts are purely feed-forward, which means that the output of the driver is predefined and not actively changed during the switching operation. The external passive components limit the gate current  $I_G$  during the whole switching event. This typically leads to unwanted higher switching delay. Furthermore, if advanced IGBT devices (e.g. IGBTs in trench-field-stop technology) are used, it can occur that  $dI_C/dt$  during turn-off gets higher although the gate resistor is increased. This effect results from the large amount of stored charge, which is built up in conduction mode, so that  $dI_C/dt$  at turn-off is sensitive to a *desaturation* of the semiconductor (for a specific range of gate resistor values). The stored charge in the IGBT's drift region is partly extracted at turn-off, which results in a faster  $dI_C/dt$  and accordingly a higher voltage overshoot on  $V_{CE}$  [45].

## 2.3.2 Active Gate Drivers with Open-Loop Slope Shaping

Active gate drivers are capable of interventions to the gate at specific points during the switching transition, either based on timing or as a reaction on different type of local feedback. Open-loop gate drivers feature an adjustable output stage, that allows for individual control of the gate current. This behavior can generally be achieved with an adjustable gate voltage [46] or gate current source (see Fig. 2.13). The adjustable gate current can be implemented either as programmable current sources [47] [48] or with switchable gate resistors [49] [50].

The main idea is to divide the switching process into different intervals, for instance, pre-charge delay,  $dI_C/dt$  interval,  $dV_{CE}/dt$  interval and post-charge delay [51–54]. For each interval a specific gate voltage or gate current is provided, in order to achieve the desired behavior and individual open-loop control.

The reference profile can be either fixed [47] or based on feedback of the switching transients [55] [56, 57]. A very fast detection of the different intervals and also a quick switching of the driver output is needed to achieve an accurate control of the power semiconductor switch.

The main limitation of the passive and the open-loop concepts is the dependency on the operating conditions such as varying junction temperature, load current or DC link voltage. Furthermore, the non-linearities of the switch cannot be compensated by this kind of control. Hence, these concepts have to be designed for the worst case, which means that in nominal case the transients are not as fast as possible, resulting in higher losses and non-ideal behavior during nominal conditions.

Fig. 2.13: Open-loop gate drive concept with adjustable output (adjustable gate voltage source or gate current source).

## 2.3.3 Active Gate Drivers with Closed-Loop Slope Shaping

To overcome the aforementioned limitations of passive and open-loop gate drivers, and to achieve a more precise and optimized control of the power switch, closed-loop concepts with negative feedback are employed. These concepts allow for compensation of the non-linearities, as well as for operating point (DC link voltage and load current) and temperature dependencies.

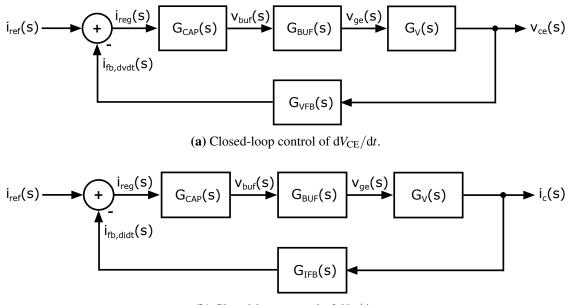

In closed-loop slope shaping, there are two significant trends. On the one hand, there is analog closed-loop control on the switching transients [58–75]. The other method is digital closed-loop slope shaping [24, 76–86]. Both principles are described in the following.

## Analog Closed-Loop Gate Drivers

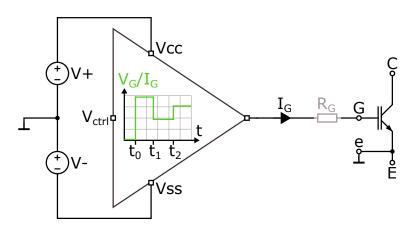

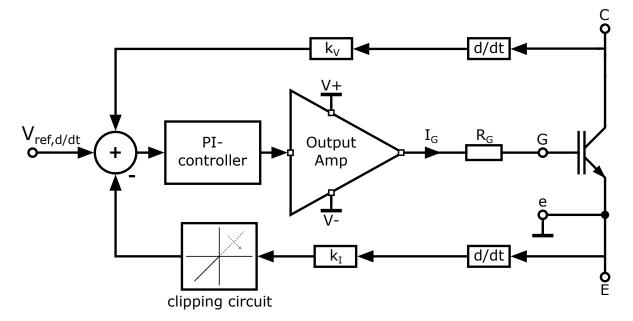

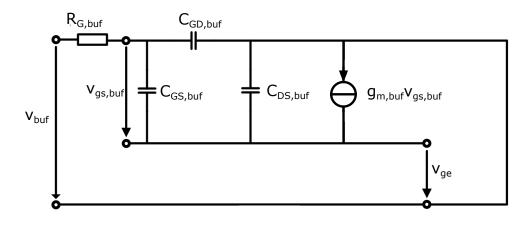

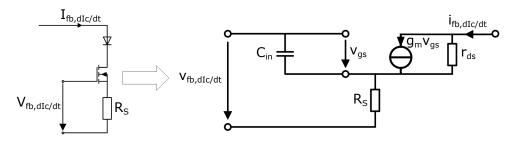

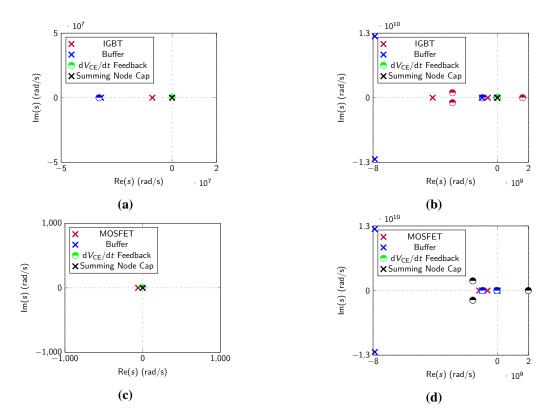

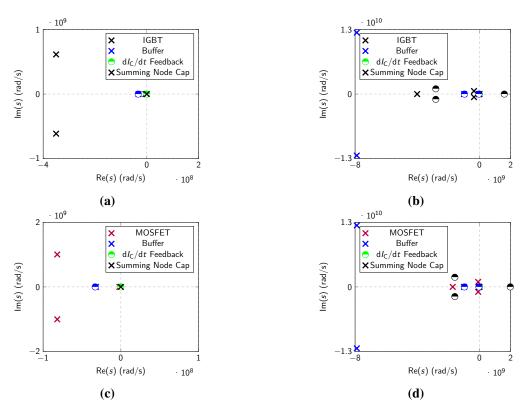

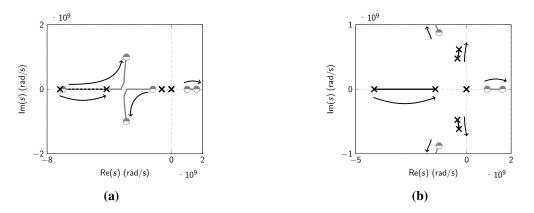

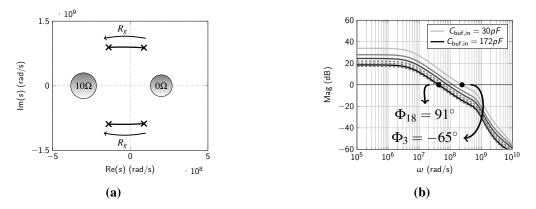

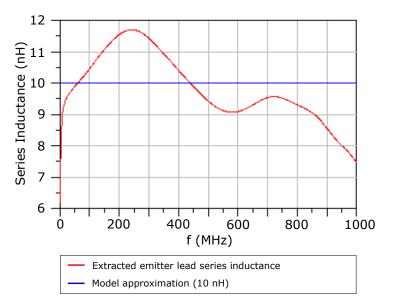

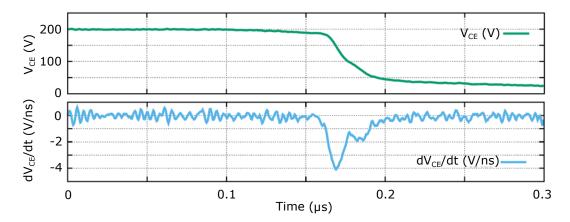

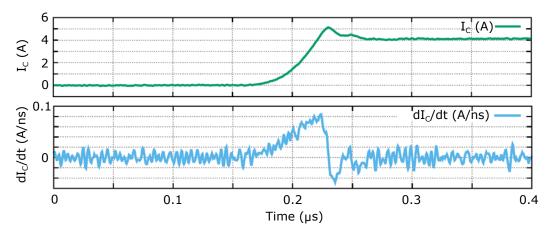

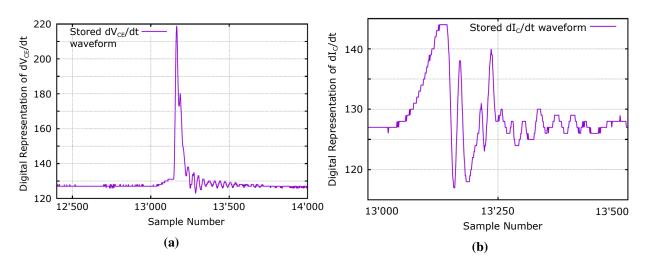

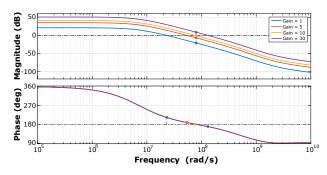

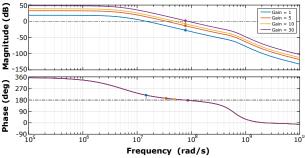

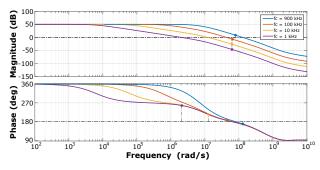

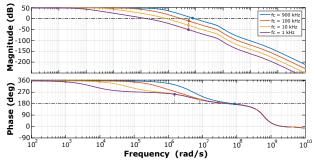

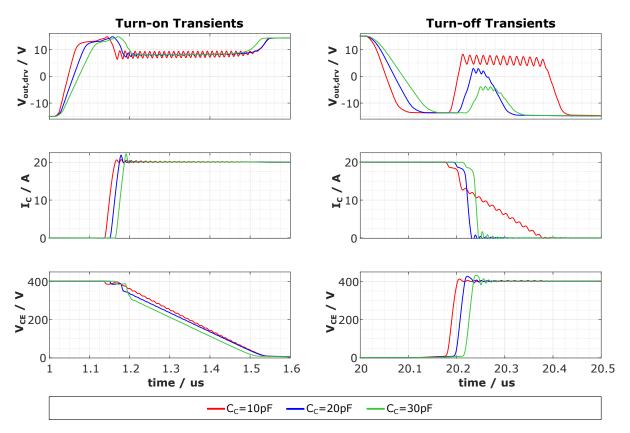

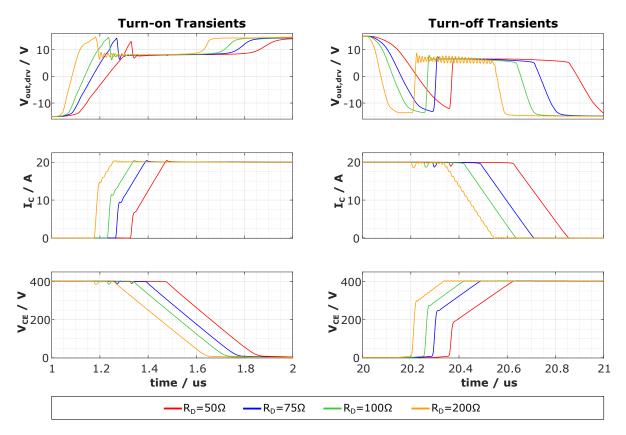

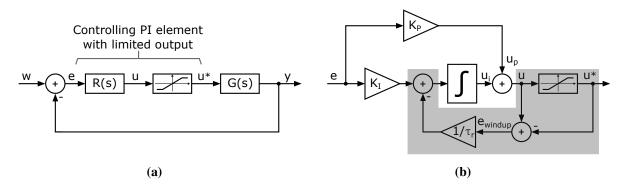

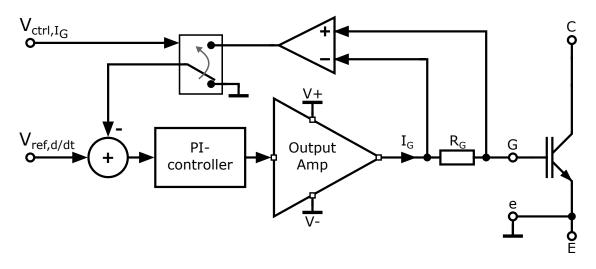

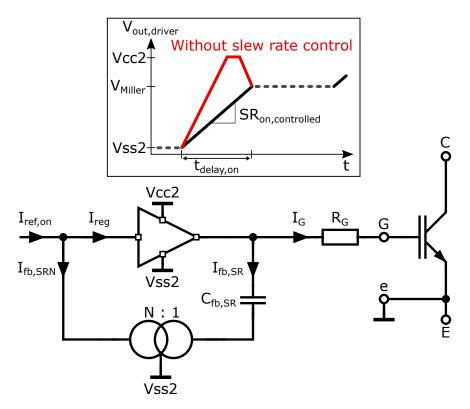

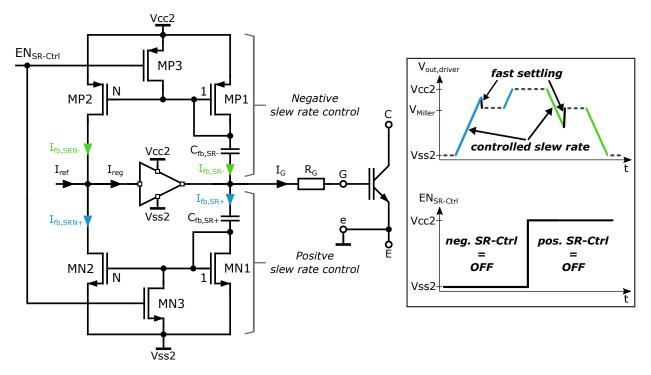

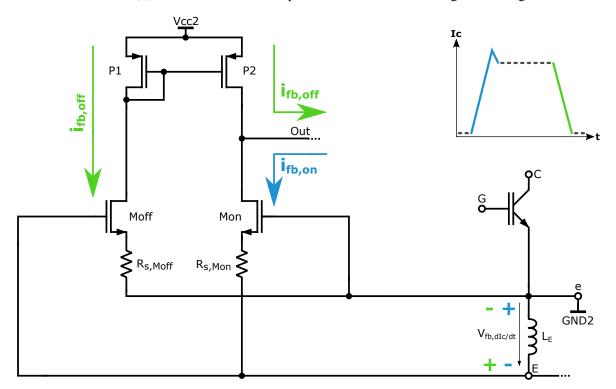

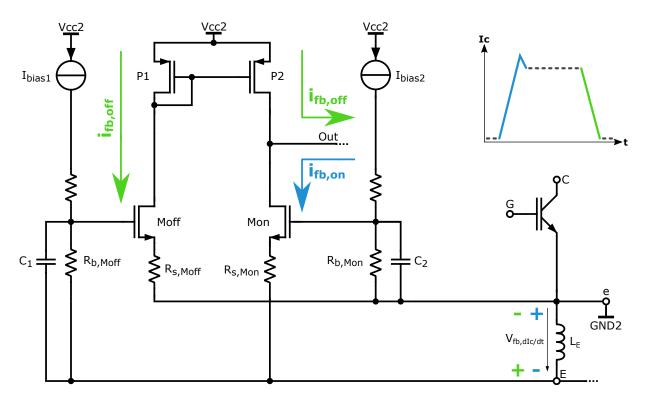

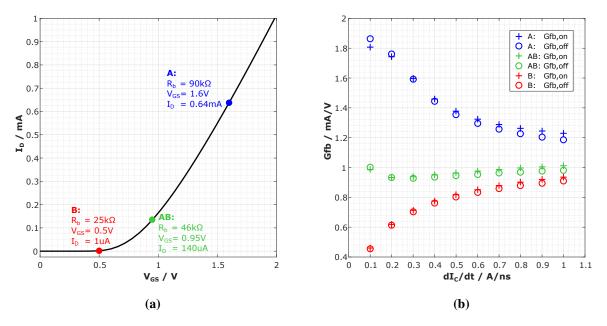

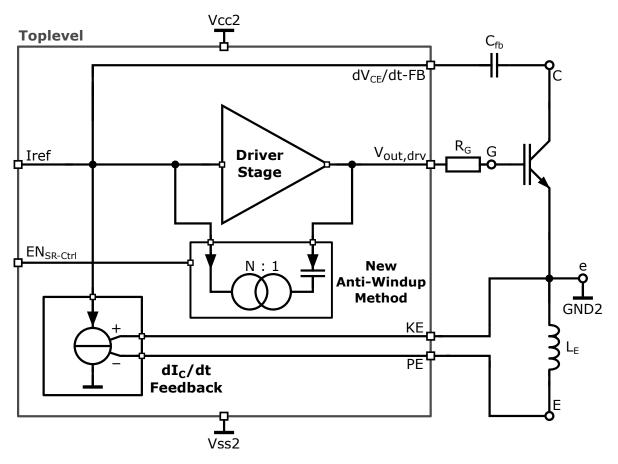

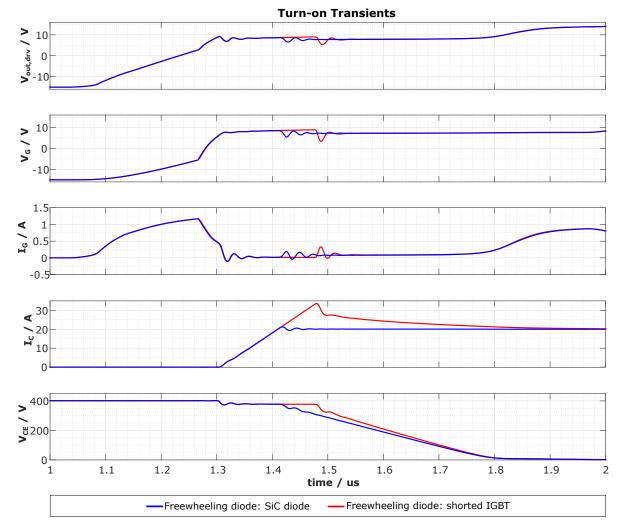

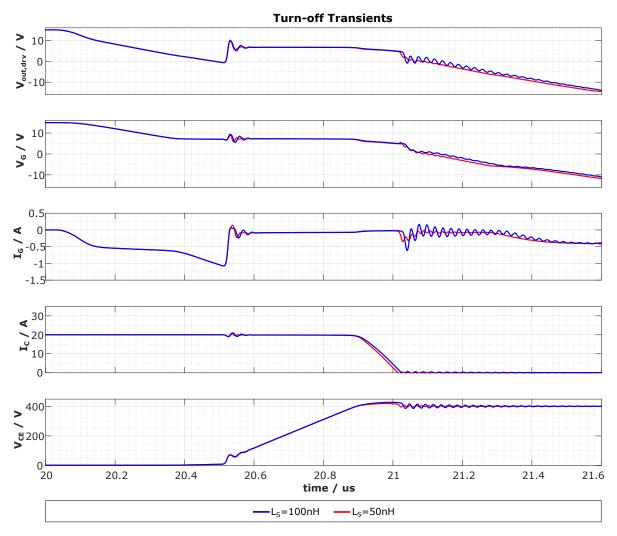

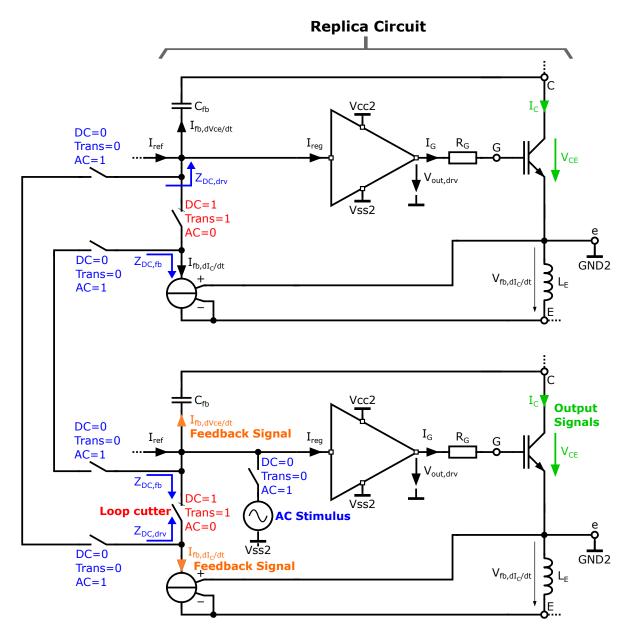

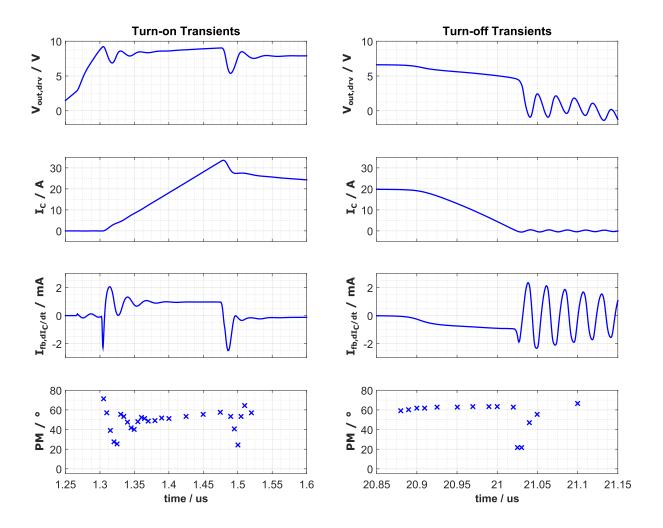

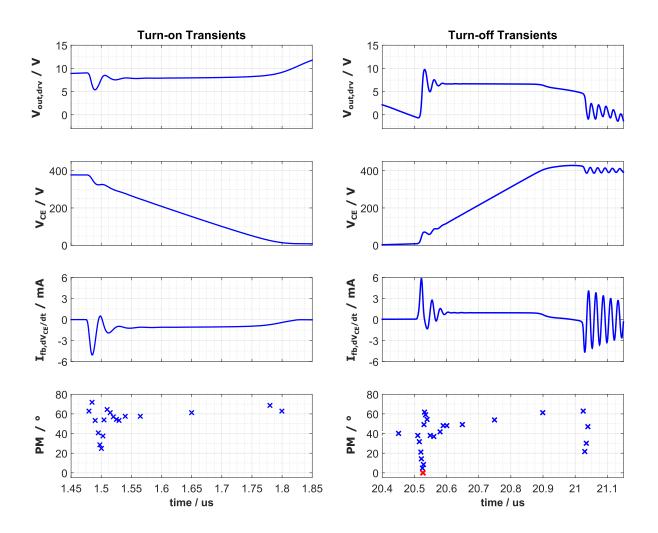

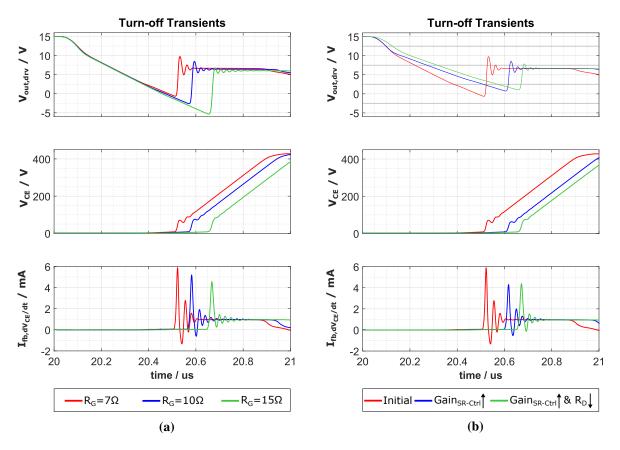

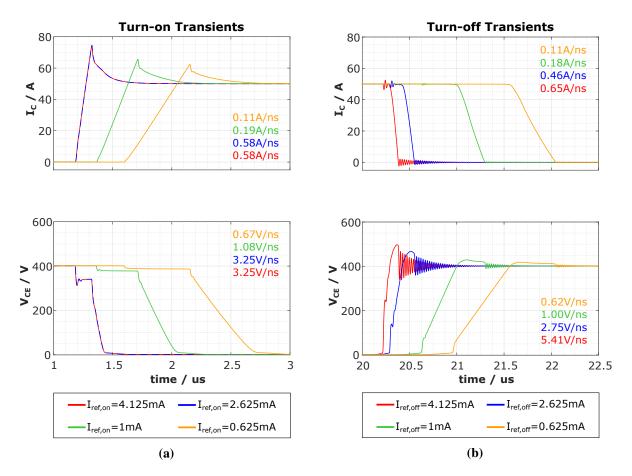

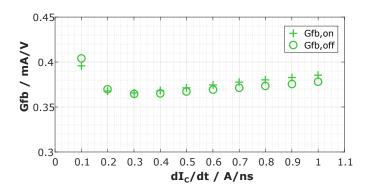

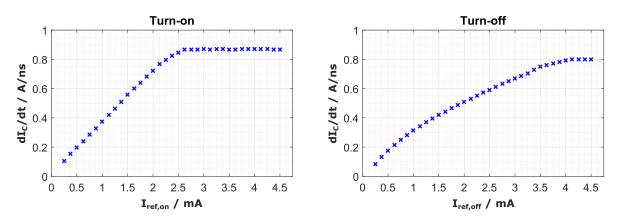

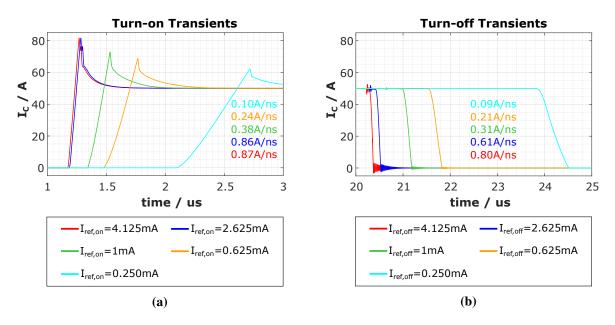

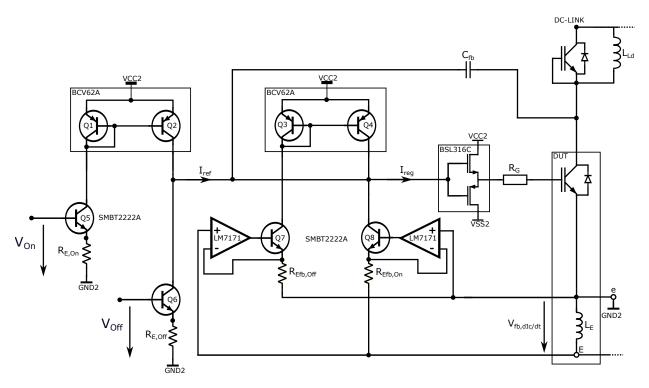

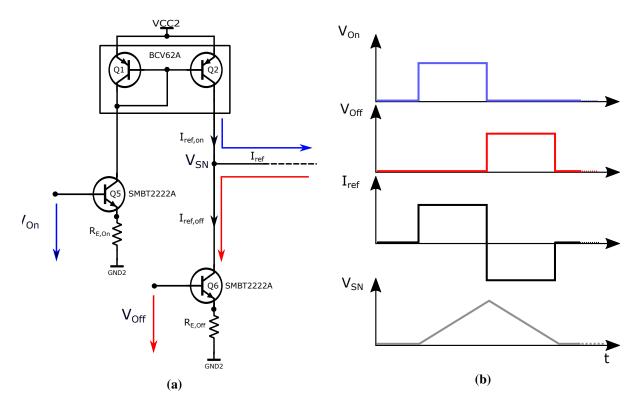

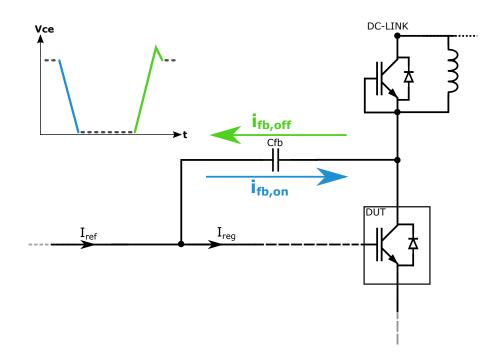

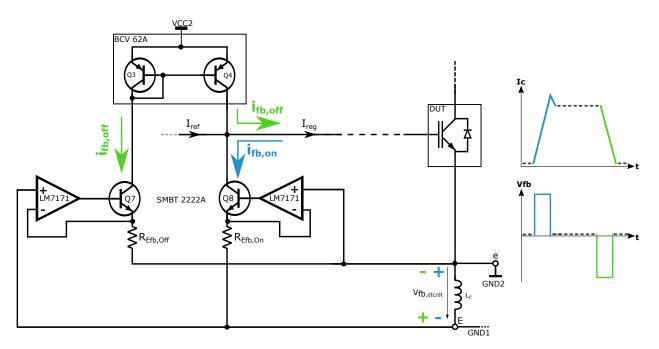

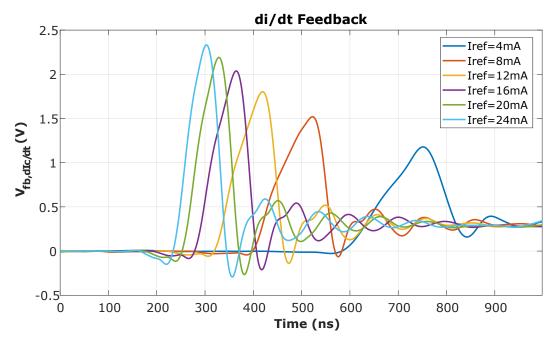

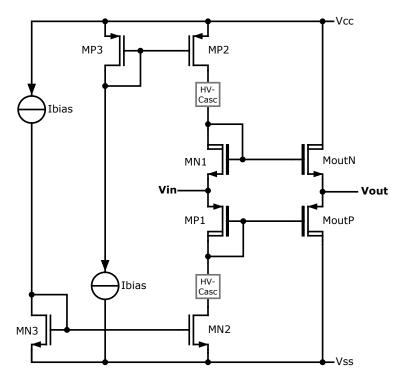

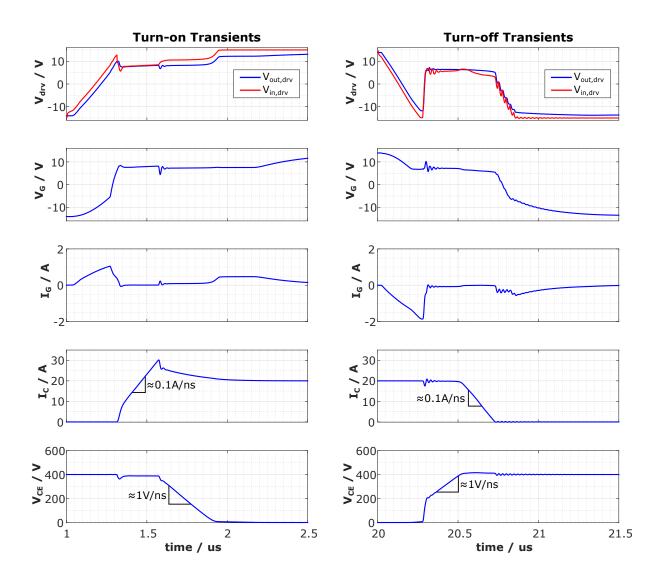

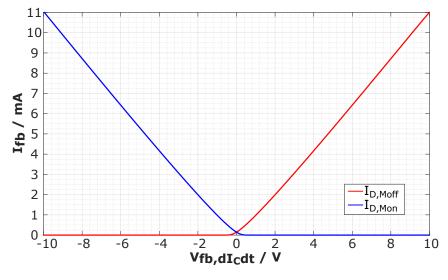

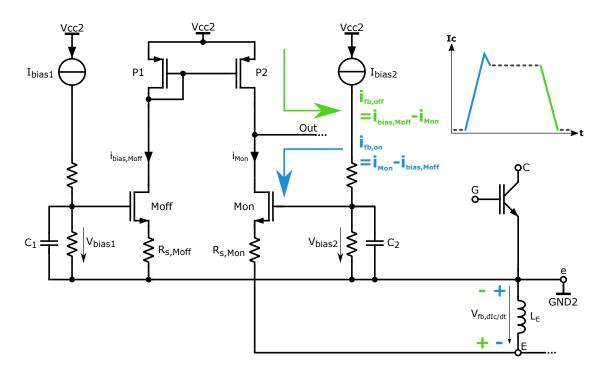

Within analog control, one can differentiate between two concepts: Concepts controlling the absolute values of  $V_{CE}(t)$  and  $I_C(t)$  (voltage/current control) and topologies which directly control  $dI_C/dt$  and  $dV_{CE}/dt$  (slope control).