# Heteroepitaxy of semiconductor—insulator layers and their interface properties

Von der Fakultät für Mathematik und Physik der Gottfried Wilhelm Leibniz Universität Hannover

> zur Erlangung des akademischen Grades Doktor der Naturwissenschaften Dr. rer. nat.

> > genehmigte Dissertation von

M.Sc. Julian Koch

Referent: Prof. Dr. Herbert Pfnür

Gottfried Wilhelm Leibniz Universität Hannover

Koreferent: apl. Prof. Dr. Andreas Fissel

Gottfried Wilhelm Leibniz Universität Hannover

Koreferent: Prof. Dr. Jens Falta

Universität Bremen

Tag der Promotion: 18.03.2021

Keywords: epitaxial interface, barium silicate, crystalline oxides

## **Abstract**

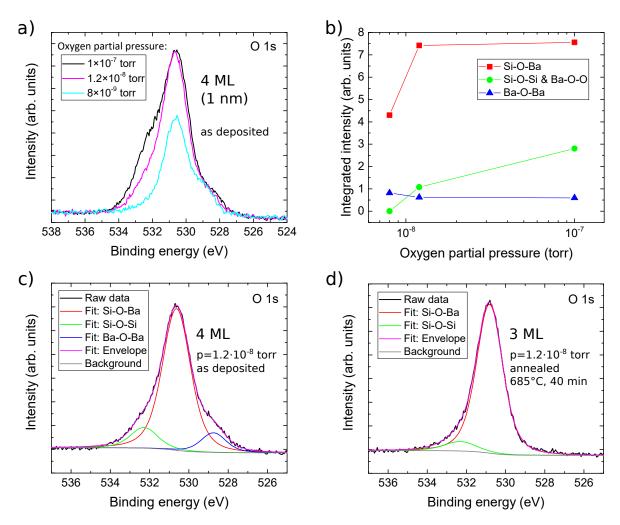

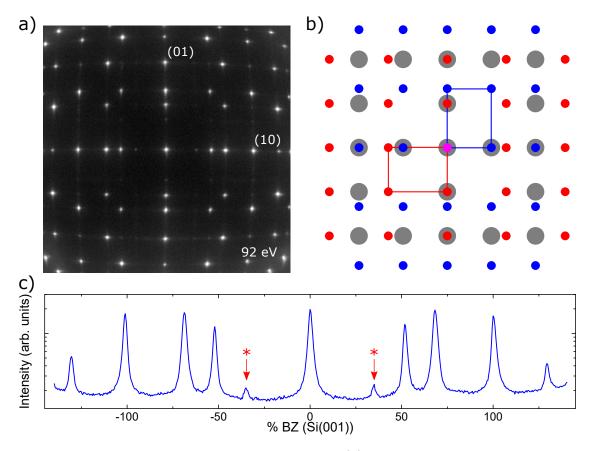

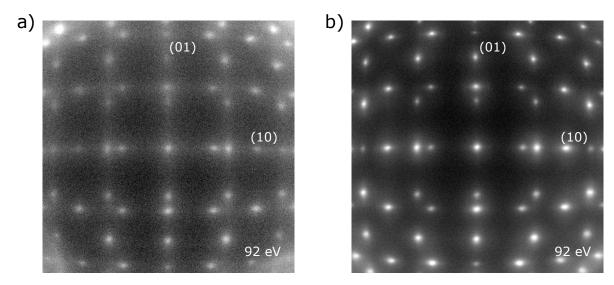

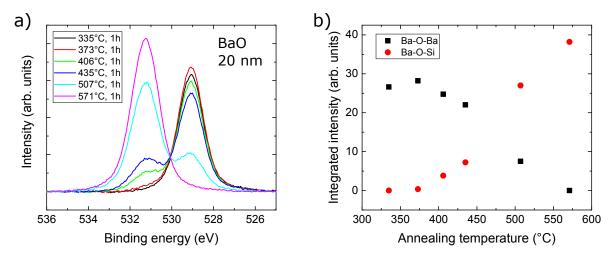

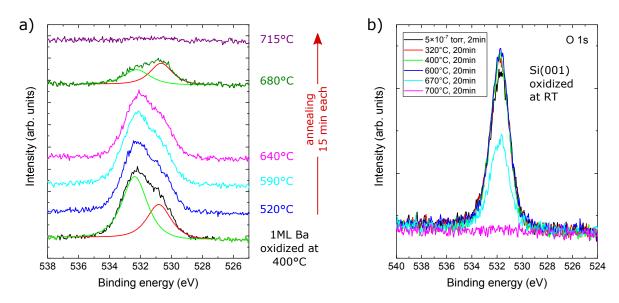

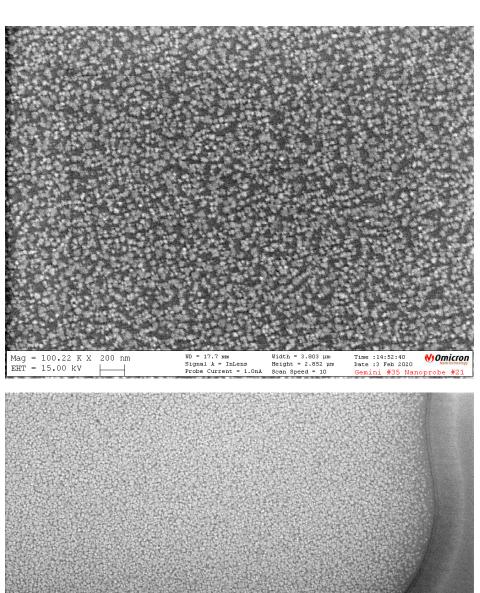

The epitaxial growth of Ba<sub>2</sub>SiO<sub>4</sub> thin films on Si(001) by co-deposition of Ba and Si in an oxygen background pressure is systematically investigated with a focus on the epitaxial interface. A structural investigation is performed by employing x-ray photoelectron spectroscopy (XPS), low energy electron diffraction (LEED) and aberrationcorrected scanning transmission electron microscopy (STEM). The stoichiometry at the interface turns out to be critically dependent on the oxygen background pressure during deposition. The key to the calibration of the oxygen pressure and the determination of the saturation point for a complete oxidation of the film is the line shape of the O1s peak in XPS. Using a two-step approach, in which a crystalline 1 nm thick film is prepared first before the rest of the film is deposited, the successful growth of epitaxial films with a thickness of up to 16 nm is demonstrated. An annealing step at 670 - 690 °C is needed to form the epitaxial interface. Films grown with a minimized oxygen pressure, i.e. an oxygen pressure just above the saturation point for a complete oxidation of the film, still feature 1/4 ML of O atoms in Si-O-Si bonding states. In comparison, the Ba<sub>2</sub>SiO<sub>4</sub> bulk structure has only O atoms in Si-O-Ba bonding states. STEM shows that these films form an atomically sharp interface to Si(001) and that the Ba<sub>2</sub>SiO<sub>4</sub> bulk structure is maintained up to the penultimate layer at the interface. Only one silicate layer is changed to a  $(2 \times 3)$  structure, which is also observed in LEED, to match the  $(2 \times 1.5)$  bulk structure to Si(001), neglecting relaxations. An interface model is proposed for the films grown with a minimized oxygen pressure, which features a pseudo- $(2 \times 1)$  reconstruction of the Si surface and helps to understand the formation process of the epitaxial interface in greater detail.

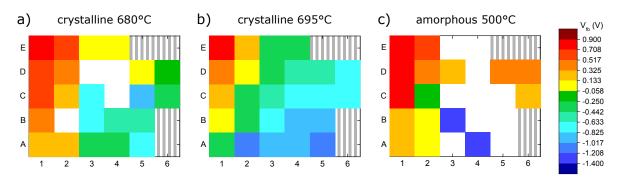

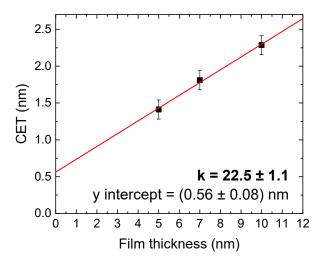

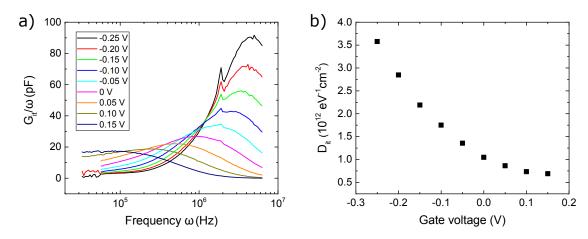

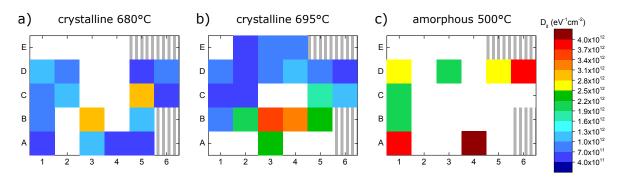

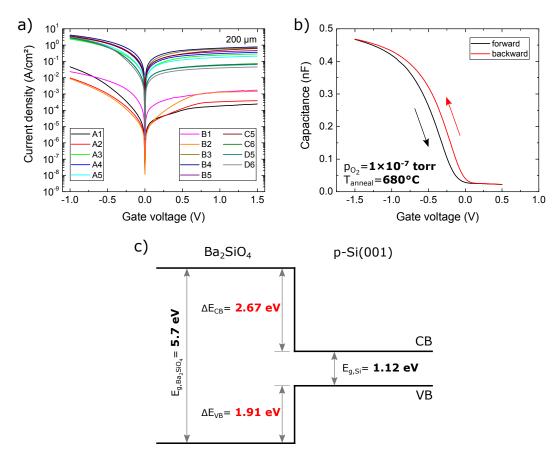

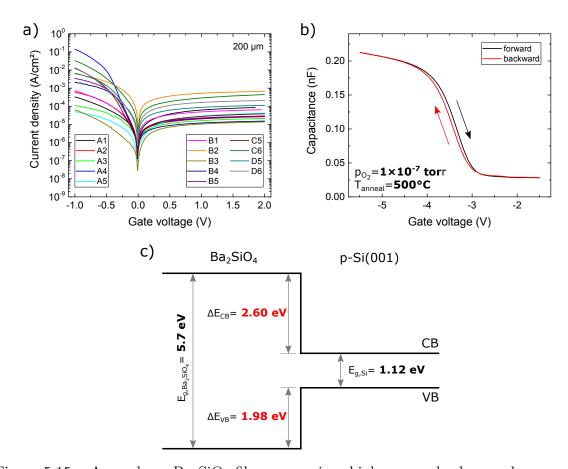

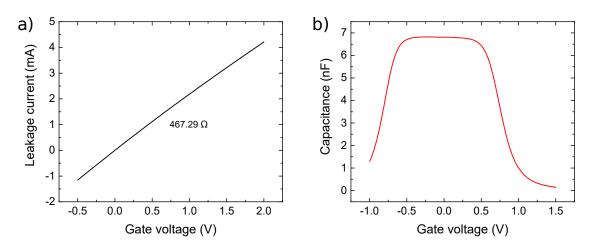

An electrical characterization is done using MOS test capacitors. A dielectric constant of  $k = 22.5 \pm 1.1$  is found for  $Ba_2SiO_4$  in agreement with Ref. [1], as well as band offsets to Si(001) larger than 1.8 eV for crystalline layers. Moreover, leakage current densities as low as  $2 \cdot 10^{-6}$  A/cm<sup>2</sup> at -1 V are measured for a 10 nm thick film. Interface trap densities at midgap of  $(1.14 \pm 0.78) \cdot 10^{12} \text{ eV}^{-1} \text{cm}^{-2}$  are measured for crystalline layers with an abrupt interface. Amorphous films show slightly higher interface trap densities of  $(2.72\pm0.82)\cdot10^{12} \text{ eV}^{-1}\text{cm}^{-2}$  at midgap. A further reduction of the interface trap density is possible by incorporating a Si-rich silicate layer at the interface, thus bringing the conditions at the interface closer to those of the  $SiO_2/Si(001)$  interface. Crystalline films with such an interfacial layer have interface trap densities of  $(3.32 \pm$  $0.45) \cdot 10^{11} \text{ eV}^{-1} \text{cm}^{-2}$  at midgap, which is more than one order of magnitude lower than for films grown by Si diffusion from the substrate [1]. Moreover, the Fermi level of the Ba<sub>2</sub>SiO<sub>4</sub> films appears to be pinned by surface states. However, even though no SiO<sub>2</sub> forms at the interface, the epitaxial interface still seems to contribute an offset of  $(0.56 \pm 0.08)$  nm to the overall CET, which greatly limits the achievable minimum CET of the gate stack.

# **Contents**

| 1. | Mot  | Motivation and introduction                                                          |    |  |  |  |

|----|------|--------------------------------------------------------------------------------------|----|--|--|--|

| 2. | Scie | entific background                                                                   | 11 |  |  |  |

|    | 2.1. | High-k materials                                                                     | 11 |  |  |  |

|    |      | 2.1.1. The MOSFET                                                                    | 11 |  |  |  |

|    |      | 2.1.2. Requirements for high-k materials                                             | 12 |  |  |  |

|    |      | 2.1.3. Overview of the high-k material selection                                     | 14 |  |  |  |

|    | 2.2. | Barium silicates                                                                     | 15 |  |  |  |

|    |      | 2.2.1. Thermodynamic stability                                                       | 15 |  |  |  |

|    |      | 2.2.2. Crystal structure and matching of Ba <sub>2</sub> SiO <sub>4</sub> to Si(001) | 16 |  |  |  |

|    | 2.3. | Low energy electron diffraction                                                      | 17 |  |  |  |

|    |      | 2.3.1. Kinematic approximation and Ewald construction                                | 18 |  |  |  |

|    |      | 2.3.2. The SPA-LEED instrument                                                       | 20 |  |  |  |

|    |      | 2.3.3. Interpretation of LEED patterns                                               | 21 |  |  |  |

|    | 2.4. | X-ray photoelectron spectroscopy                                                     | 22 |  |  |  |

|    |      | 2.4.1. Binding energy of core level peaks                                            | 22 |  |  |  |

|    |      | 2.4.2. Auger peaks                                                                   | 23 |  |  |  |

|    |      | 2.4.3. The XPS spectrum                                                              | 24 |  |  |  |

|    |      | 2.4.4. Core level peak shapes and shifts                                             | 25 |  |  |  |

|    |      | 2.4.5. Intensity of core level peaks                                                 | 27 |  |  |  |

|    |      | 2.4.6. Determination of the layer thickness                                          | 28 |  |  |  |

|    | 2.5. | Underlying theory of the electrical characterization                                 | 29 |  |  |  |

|    |      | 2.5.1. The different regions of a MOS capacitor and the CV-curve                     | 29 |  |  |  |

|    |      | 2.5.2. Three-element model and correction for series resistance                      | 32 |  |  |  |

|    |      | 2.5.3. Determination of the flat band voltage from the CV-curve                      | 34 |  |  |  |

|    |      | 2.5.4. Determination of the interface trap density with the conductance method       | 37 |  |  |  |

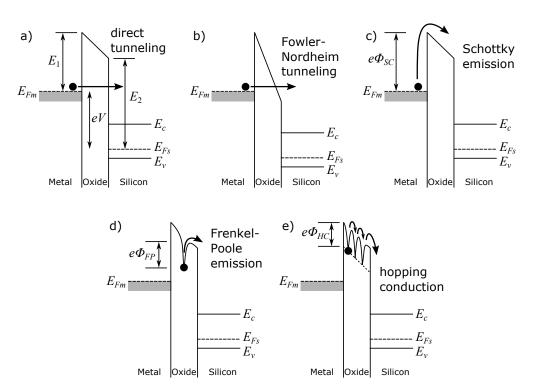

|    |      | 2.5.5. Conduction mechanisms through thin oxide layers                               | 39 |  |  |  |

| 3. | Exp  | erimental                                                                            | 43 |  |  |  |

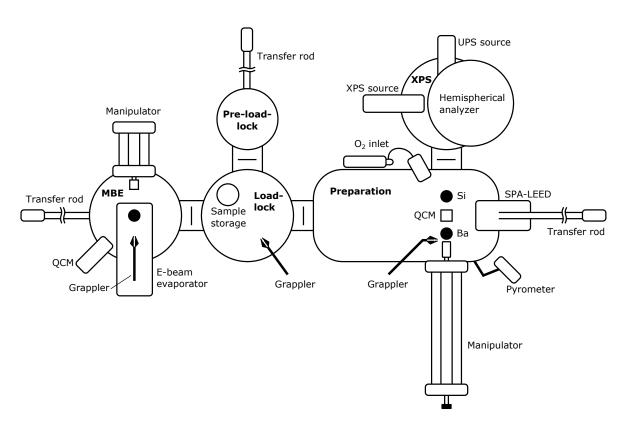

|    | 3.1. | Experimental setup                                                                   | 43 |  |  |  |

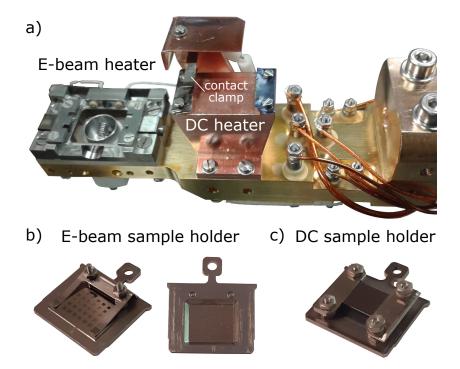

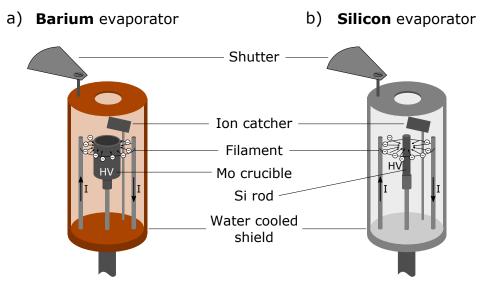

|    |      | 3.1.1. The Ba and Si evaporators                                                     | 45 |  |  |  |

|    | 3.2. | Sample preparation                                                                   | 47 |  |  |  |

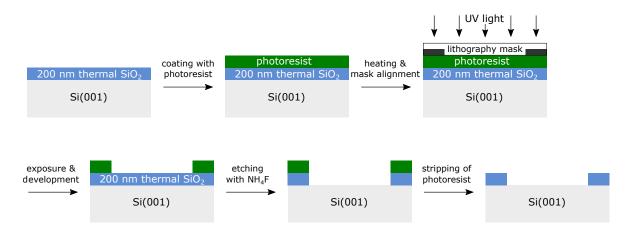

|    |      | 3.2.1. Cleaning of the unstructured substrates                                       | 48 |  |  |  |

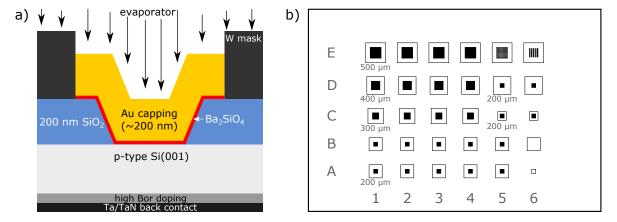

|    |      | 3.2.2. Preparation and cleaning of the structured substrates                         | 49 |  |  |  |

|    |      | 3.2.3. Preparation of the thin films                                                 | 51 |  |  |  |

|    | 3.3. | Experimental details of the measurements                                             | 52 |  |  |  |

|    |      | 3.3.1. X-ray photoelectron spectroscopy                                              | 52 |  |  |  |

|    |      | 3.3.2. Scanning transmission electron microscopy                                     | 53 |  |  |  |

## Contents

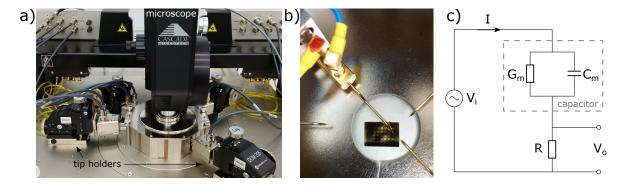

|      |      | 3.3.3. Electrical characterization                                                             | 53  |

|------|------|------------------------------------------------------------------------------------------------|-----|

| 4.   | Stru | ectural properties of $Ba_2SiO_4$ thin films                                                   | 55  |

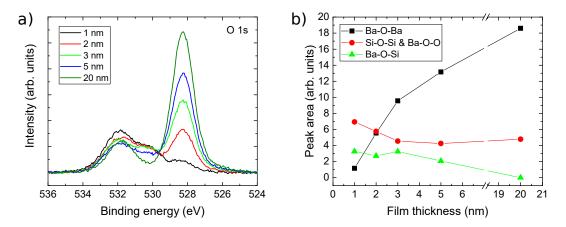

|      | 4.1. | Identification of chemical bond formation from the shift of the O 1s signal                    |     |

|      |      | in XPS                                                                                         | 55  |

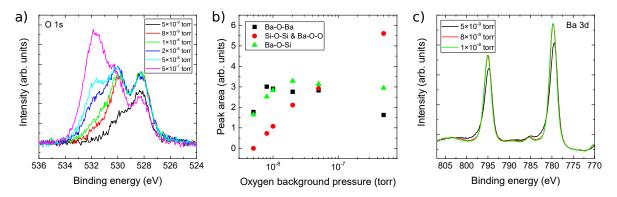

|      | 4.2. | Detection of metallic barium from the line shape of the Ba 3d peak                             | 56  |

|      | 4.3. | Formation of BaO <sub>2</sub> during the film growth                                           | 57  |

|      | 4.4. | Stoichiometry and chemical homogeneity of Ba <sub>2</sub> SiO <sub>4</sub> thin films          | 59  |

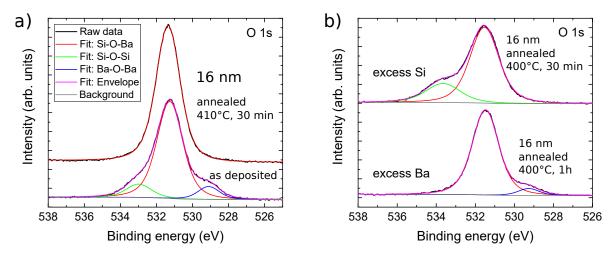

|      | 4.5. | Interface properties and oxygen background pressure                                            | 61  |

|      | 4.6. | Epitaxial growth of $Ba_2SiO_4$ films on $Si(001)$                                             | 63  |

|      | 4.7. |                                                                                                | 70  |

|      | 4.8. | Si 2s and Si 2p and their deconvolution into silicate and substrate con-                       |     |

|      |      | tributions                                                                                     | 72  |

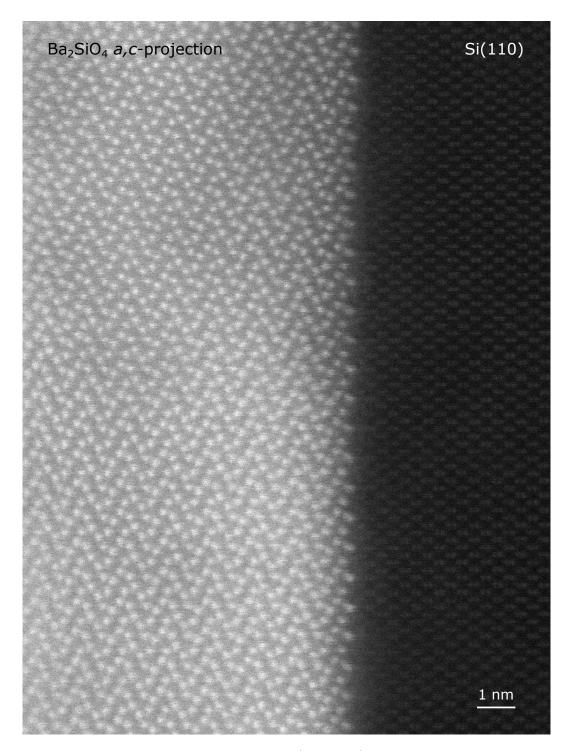

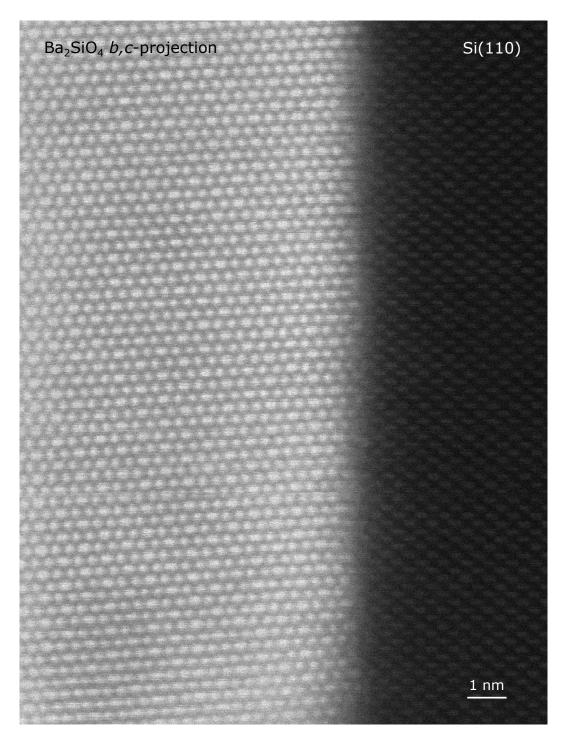

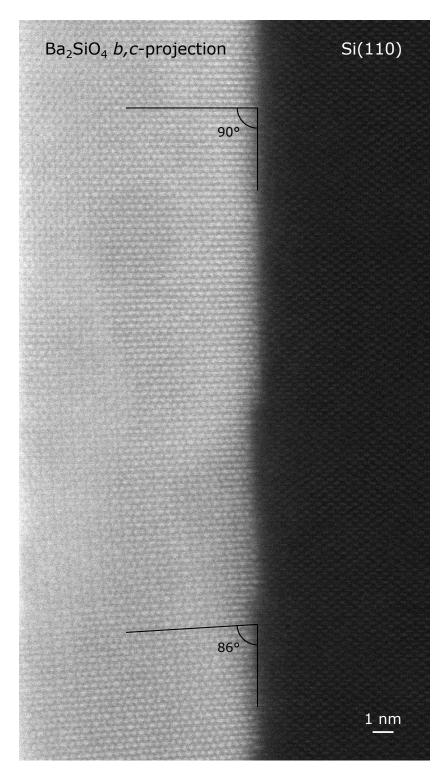

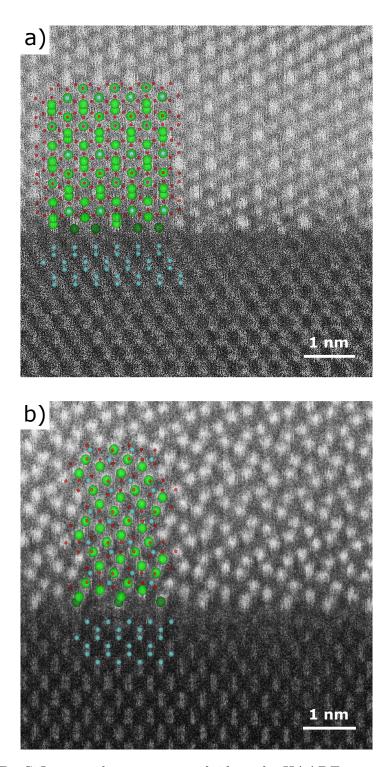

|      |      | Cross-sectional STEM measurements                                                              | 73  |

|      | 4.10 | The epitaxial interface between $Ba_2SiO_4$ and $Si(001)$                                      | 78  |

| 5.   | Elec | trical properties of $Ba_2SiO_4$ thin films on $Si(001)$                                       | 83  |

|      | 5.1. | Band alignment of the $Ba_2SiO_4/Si(001)$ heterostructure                                      | 83  |

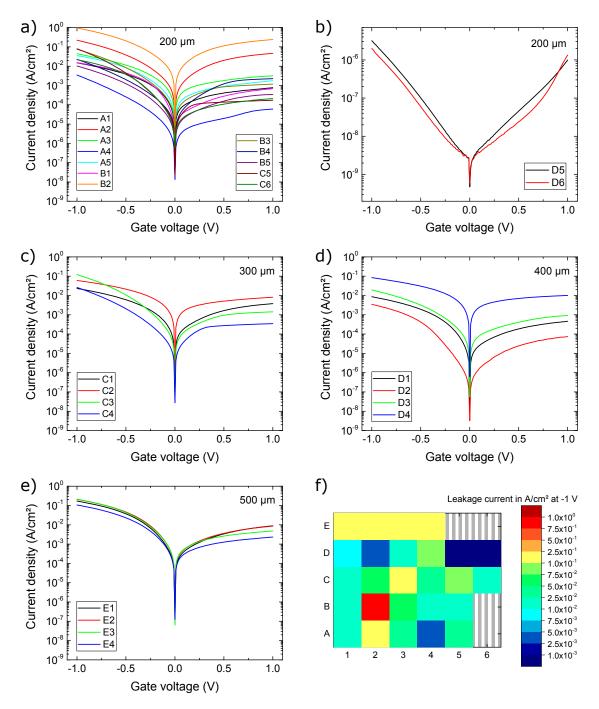

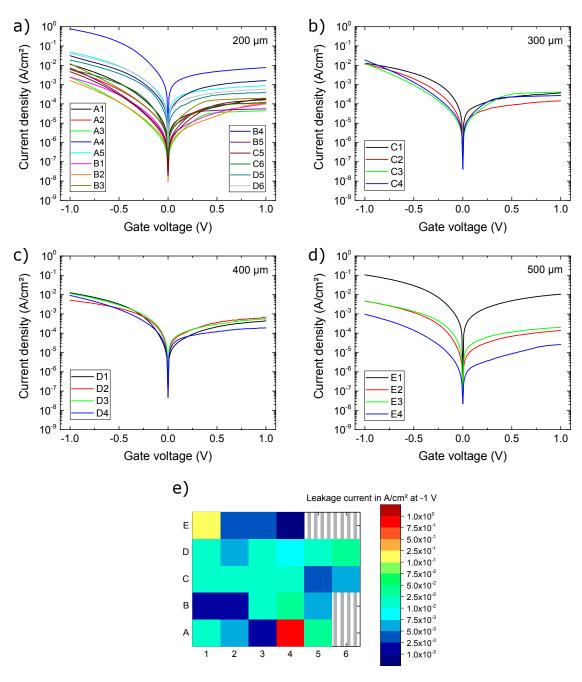

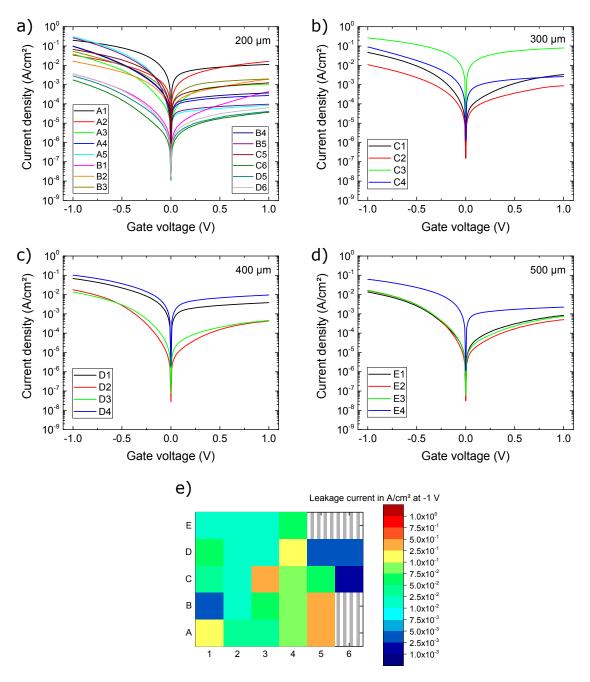

|      | 5.2. | Leakage current through $Ba_2SiO_4$ films                                                      | 87  |

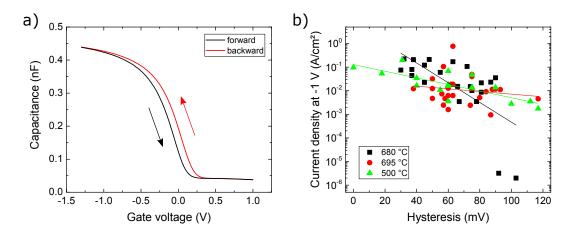

|      | 5.3. | Capacitance voltage measurements: Flat band voltage and hysteresis .                           | 92  |

|      | 5.4. | Dielectric constant of $Ba_2SiO_4$                                                             | 95  |

|      | 5.5. | Interface trap density of the $\mathrm{Ba_2SiO_4/Si}$ system                                   | 96  |

|      |      | Effect of an interfacial Si-rich silicate layer on the electrical properties .                 | 99  |

|      | 5.7. | Assessment of the results and comparison with the literature                                   | 102 |

| 6.   | Sum  | imary and conclusion                                                                           | 10! |

| Δ    | Ann  | endix                                                                                          | 109 |

| - •• |      | Short-circuit due to carbon residues                                                           | 109 |

|      |      | Re-examination of the previous work                                                            | 112 |

|      |      | Comparison of the crystal structures of Ba <sub>2</sub> SiO <sub>4</sub> and BaSi <sub>2</sub> | 116 |

## List of abbreviations

CB Conduction band

CEM Channel electron multiplier

CET Capacitance-equivalent thickness

CL Core level

CMOS Complementary metal-oxide-semiconductor

DFT Density-functional theory

EOT Equivalent oxide thickness

fb Flat band

FIB Focused ion beam

FinFET Fin field-effect transistor

HAADF High-angle annular dark-field

HMDS Hexamethyldisilazane

LEED Low-energy electron diffraction

ML Monolayer

MOS Metal oxide semiconductor

MOSFET Metal oxide semiconductor field-effect transistor NIST National Institute of Standards and Technology

QCM Quartz crystal microbalance rpm Revolutions per minute (unit) RSF Relative sensitivity factor

RT Room temperature

SEM Scanning electron microscopy/microscope

SPA-LEED Spot profile analysis low energy electron diffraction STEM Scanning transmission electron microscopy/microscope

TEM Transmission electron microscopy/microscope

UHV Ultra-high vacuum

VB Valence band

VLSI Very large-scale integration

XPS X-ray photoelectron spectroscopy/spectroscope

## 1. Motivation and introduction

The complementary metal-oxide-semiconductor (CMOS) transistor is the fundamental switching device in micro- and nanoelectronic circuits. Over the years its dimensions have been continuously reduced in order to keep increasing the performance of the integrated circuits by increasing the number of active components per area and lowering the switching times of the transistors. However, there is a physical limit to this process due to the tunneling leakage currents that occur at low thicknesses of the gate dielectric. When the  $SiO_2$  layer, which was originally used as the gate dielectric, became only about 1 nm thick, an unacceptably high density of power dissipation due to tunneling leakage currents occurred [2, 3], which lead to the search for an alternative material with a higher dielectric constant k [4, 5]. These so-called high-k materials offer the same capacitance at a higher physical layer thickness, thus greatly reducing the tunneling leakage currents, which are exponentially dependent on the layer thickness.

The high-k research was focused mainly on amorphous oxides, out of which HfO<sub>2</sub> has emerged as the best suited material for practical applications [4, 6, 7, 8, 9]. However, even the scaling with these high-k materials in planar transistor structures has reached a limit and in order to keep increasing the density of active components, three dimensional transistor structures, in particular the FinFET design [10], that focus on reducing the active area of the transistors by changing the fundamental structure of the transistor instead of simply reducing the thickness of the gate dielectric, have been developed. The main obstacle to a further reduction of the physical layer thickness of the gate dielectric is the formation of a well-defined, abrupt interface between the high-k material and silicon. The interface between the amorphous high-k oxides and silicon are typically rather defectious. In the case of HfO<sub>2</sub>, low interface trap densities are achieved due to an interfacial SiO<sub>2</sub> layer, which arises naturally during the device processing [11]. However, such an intermediate layer reduces the total capacitance, since the capacitances of the HfO<sub>2</sub> and SiO<sub>2</sub> layers add up reciprocally, thus severely limiting the scaling at very low thicknesses. The initial thickness of this SiO<sub>2</sub> layer is also rather difficult to control, which is why scavenging techniques have been developed in order to reduce its thickness retroactively [12].

A continuation of the scaling to the lowest possible layer thickness of the gate dielectric requires the formation of an atomically sharp interface with an extremely low defect density surpassing even the  $\mathrm{SiO}_2/\mathrm{Si}$  interface. This can be achieved by implementing crystalline gate oxides [6, 13, 14]. McKee et al. have already shown that epitaxial  $\mathrm{BaTiO}_3$  can be grown on  $\mathrm{Ge}(001)$  with an interface trap density  $D_{it} < 10^{10} \,\mathrm{eV}^{-1}\mathrm{cm}^{-2}$  by using a layer sequencing technique to manipulate the interface [15]. Nevertheless, a system with a crystalline oxide that fulfills this requirement while also meeting all other requirements for high-k gate dielectrics [4] has not been found. The band gap of  $\mathrm{BaTiO}_3$  is too small for practical application. Epitaxial  $\mathrm{Ba}_{0.7}\mathrm{Sr}_{0.3}\mathrm{O}$  lattice matched

#### 1. Motivation and introduction

to Si(001) is thermodynamically unstable in contact with silicon and reacts with the substrate to form silicate at temperatures above 400 °C [16].

Crystalline Ba<sub>2</sub>SiO<sub>4</sub> is a candidate that could potentially fulfill all requirements for a crystalline gate oxide. Even tough Ba<sub>2</sub>SiO<sub>4</sub> has a tetragonal crystal symmetry, it grows epitaxially on Si(001), whereby its longest crystal axis grows perpendicular to the Si(001) surface, while the lattice constants in the other two crystal directions are approximately equivalent to 2 and 1.5 times the Si lattice constant in [110] direction, respectively [17, 1]. Ba silicates are thermodynamically stable, i.e. the reaction of the oxides SiO<sub>2</sub> and BaO to silicate is exothermic [18]. Moreover, silicates are in general also kinetically stable up to their desorption temperature above 750 °C [17, 19, 20, 21], making their thermal stability comparable to that of SiO<sub>2</sub>. In addition, Ba<sub>2</sub>SiO<sub>4</sub> also fulfills other important requirements placed upon high-k materials. Epitaxial films have shown a dielectric constant of  $22.8 \pm 0.2$ , band offsets to p-Si(001) of over 2 eV and an acceptable leakage current of 3 mA/cm<sup>2</sup> at -1 V [1]. The main problem that remains is that these films featured a high density of interface traps of  $D_{it} = (1 \pm$  $(0,5) \times 10^{13} \,\mathrm{eV^{-1} cm^{-2}}$  [1]. One of the primary factors contributing to this is most likely the growth process, which relied upon the diffusion of Si from the substrate into a deposited BaO layer in order to form the silicate layers. The diffusion leads to an atomically rough interface and since it requires concentration gradients, it may introduce local disorder and variations of the chemical composition.

In order to avoid the diffusion problem, a co-deposition growth method, in which Ba and Si are evaporated simultaneously in an oxygen atmosphere, is implemented in this thesis. The expectation is that this will reduce the interface trap density. Also, this will hopefully allow for a reduction of the annealing temperature required to grow epitaxial films, since the diffusion of Si from the substrate is not required anymore. The films grown by Si diffusion from the substrate required a rather high annealing temperature of around 670 °C [1]. The main goal of this thesis is to gain an understanding of the intricacies of the epitaxial growth process of Ba<sub>2</sub>SiO<sub>4</sub> on Si(001), in particular with respect to the formation of the epitaxial interface, in order to enable the purposeful manipulation of the interface. Therefore, the scope of this thesis is not limited to the search for alternative gate dielectrics, but also encompasses a contribution to the physical understanding of the formation of epitaxial semiconductor-insulator interfaces, which are of scientific and technological interest for various reasons beyond the use as a gate dielectric, e.g. as wave guides [22], barriers for tunnel junctions and spin filters [23].

A structural investigation of the Ba<sub>2</sub>SiO<sub>4</sub> films and their epitaxial interface to Si(001) is performed by employing x-ray photoelectron spectroscopy (XPS), low energy electron diffraction (LEED) and aberration-corrected scanning transmission electron microscopy (STEM). MOS test capacitors are prepared in order to perform an electrical characterization. Parts of this thesis were already published in [24].

## 2.1. High-k materials

#### 2.1.1. The MOSFET

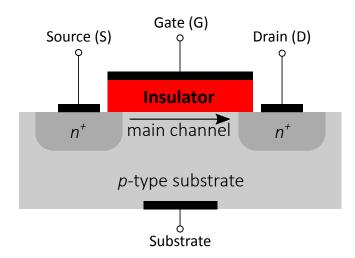

Figure 2.1.: Illustration of an n-channel metal-oxide-semiconductor field-effect transistor (MOSFET). Based on Ref. [25].

The metal-oxide-semiconductor field-effect transistor (MOSFET) is a voltage-controlled resistor. As illustrated in Fig. 2.1, it consists of a low doped semiconductor substrate, typically silicon, a source and a drain contact for the main current, a gate contact that is insulated from the source-drain-channel by a thin oxide layer and, optionally, a substrate contact at the back [25, 26]. In the case of a p-type substrate, as shown in the figure, the source and drain contacts are highly doped n-type regions. This creates an npn structure, so that the current flow from source to drain is inhibited due to the formation of depletion zones at the transitions of the doping regions. By applying a voltage to the gate contact so that the band edges of the silicon substrate bend down at the interface to the insulator until the Fermi level is close to the conduction band edge, thus populating the region close to the insulator with electrons, an inversion layer or n-channel is created between the source and drain contacts enabling a current flow [25] (see also section 2.5.1). The electron density in the inversion layer and thus the source-drain-current can be controlled with the gate voltage.

If an n-type substrate is used, the source and drain contacts are highly doped p-type regions and a p-channel is created between them by bending the band edges of the

silicon up at the interface until the Fermi level is close to the valence band edge. Moreover, by doping the region of the substrate close to the insulator opposite to the rest of the substrate, a transistor is created that allows current flow between source and drain if no gate voltage is applied and can be switched off by applying a gate voltage.

In this work, only the middle part of the MOSFET without the source and drain contacts, i.e. MOS-capacitors, will be manufactured in order to characterize the  $\mathrm{Ba_2SiO_4}$  thin films.

#### 2.1.2. Requirements for high-k materials

The gate stack works like a parallel-plate capacitor with the insulator as the dielectric. Its capacitance can be described by [4]:

$$C = \varepsilon_0 k \frac{A}{d},\tag{2.1}$$

with  $\varepsilon_0$  being the vacuum permittivity, k being the dielectric constant of the insulating layer, d being its thickness and A being its area. For a long time SiO<sub>2</sub> was used as the gate dielectric. In order to increase the density of the active elements as well as the switching speeds, the dimensions of the transistors have been continuously reduced. During this process, the thickness of the dielectric has to be reduced by the same factor as the area, i.e. the *square* of the gate length, to keep the same capacitance (see equation 2.1). Eventually, when the SiO<sub>2</sub> layer was only a few nanometers thick, the tunneling leakage currents became so large that they resulted in an unacceptably high density of power dissipation [2, 3]. It follows from equation 2.1 that the only way to increase the thickness of the dielectric and thereby reducing the tunneling currents, while keeping the active area and the capacitance of the gate stack unchanged, is to increase the dielectric constant of the gate insulator. Therefore, the search for suitable alternative gate insulators with a higher dielectric constant than SiO<sub>2</sub> (k = 3.9), so-called high-k materials, began [4, 5].

To characterize the high-k materials, the equivalent oxide thickness (EOT), which is the thickness that an  $SiO_2$  layer with the same capacitance per area would have, is defined [4]:

$$EOT = \frac{3.9}{k} \cdot d,\tag{2.2}$$

where 3.9 is the dielectric constant of  $SiO_2$ , k is the dielectric constant of the high-k material and d is its thickness.

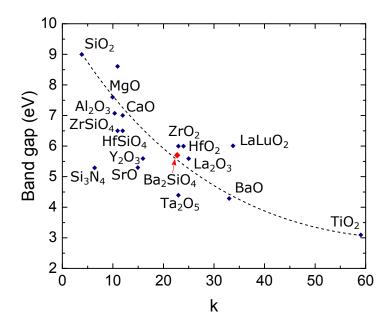

While a high dielectric constant is needed to reduce the tunneling leakage currents, there is a limit to the possible increase due to the inverse relationship between k and the band gap of the insulator (see Fig. 2.2). A large band gap is the prerequisite for large band offsets to silicon, which are required to inhibit carrier injection from the silicon into the insulator, since this would lead to leakage currents through the insulator. Moreover, there are several requirements for alternative gate dielectrics with regard to

Figure 2.2.: Band gap vs. dielectric constant k for candidate gate insulators [4, 27]. Ba<sub>2</sub>SiO<sub>4</sub> data taken from [1].

its interface to silicon, since this is where the main source-drain current flows, and its thermodynamic and kinetic stability. The requirements for practical application can be summed up as follows [4]:

- 1. The dielectric constant k must be high enough so that the material can be used for multiple scaling cycles. It should be at least greater than 12 and preferably greater than 25.

- 2. The material must function as an insulator. In particular, this means that the conduction and valence band offsets between the gate dielectric and silicon must be at least greater than 1 eV in order to minimize charge carrier injection into the gate dielectric [28]. Since the band offsets are usually not symmetrical, the material should ideally have a band gap greater than 5 eV, which limits the the maximum dielectric constant to about 30 due to the correlation shown in Fig. 2.2 [4, 28]. Furthermore, no other parasitic conduction mechanisms should occur.

- 3. It must form a high quality electrical interface with silicon, i.e. low interface roughness, no interface states or defect states in the Si band gap [29] and high charge carrier mobility.

- 4. Low density of electrically active defects, i.e. interface traps, fixed charges and bulk traps.

- 5. Thermodynamic stability in contact with Si: The material must not react with the silicon substrate, since this would result in the formation of a different chemical compound at the interface, which can affect the properties of the gate stack, in particular the effective k-value, negatively.

6. Kinetic stability: It has to be possible to process the material at 1000 °C for 5 s, so that it is compatible with the standard CMOS processing. This requirement can be circumvented by using a gate last process [30, 31].

The dielectric constant is the sum of an electronic and a lattice contribution. The electronic contribution  $k_e$  is the same as the optical dielectric constant and therefore the refractive index squared, which is typically 4-5 and at a maximum 8 [32]. Hence, the majority of the dielectric constant has to come from the lattice contribution  $k_l$ , which is given by [33, 32]

$$k_l = \frac{Ne^2 Z_T^{*2}}{m\omega_{TO}^2},$$

(2.3)

where N is the number of ions per unit volume, e is the elementary charge,  $Z_T^*$  is the transverse dynamic effective charge, m is the reduced ion mass and  $\omega_{TO}$  is the frequency of the transverse optical phonon. In order to obtain large values of  $k_l$ ,  $Z_T^*$  has to be large and/or  $\omega_{TO}$  has to be small. The variation of these two parameters with the band gap also explains the variation of the dielectric constant seen in Fig. 2.2 [32]. On the one hand,  $Z_T^*$  is due to the rearrangement of the electronic charge as a consequence of ion movement. Since this rearrangement requires the electrons to be mobile and the minimum energy that the electrons in the valence band have to overcome in order to become mobile is the band gap,  $Z_T^*$  increases with decreasing band gap. On the other hand, the transverse optical phonon frequency  $\omega_{TO}$  is directly related to the energy of the transverse optical phonon by  $E_{TO} = \hbar \omega_{TO}$ . If this energy is larger than the band gap, the phonon can be absorbed by the solid. Consequently, the maximum  $\omega_{TO}$  decreases with decreasing band gap.

## 2.1.3. Overview of the high-k material selection

Of the extensively studied candidates for an alternative gate oxide,  $HfO_2$  (k=25) has emerged as the best suited for practical applications. Compared to  $HfO_2$ ,  $ZrO_2$ , while having the same k-value, is more reactive in contact with Si and can easily form a silicide [34]. Some of the oxides of the lanthanides have a higher dielectric constant and lower leakage currents than  $HfO_2$ , but they are hygroscopic [35, 36, 37].  $Y_2O_3$  is also a possible candidate, but is has a lower k-value, namely k=15 [4], than  $HfO_2$ .

The silicates of the aforementioned oxides were also investigated, since they have higher crystallization temperatures [38, 39, 40]. However, their k-value is significantly reduced as compared to the respective high-k oxide (e.g.  $HfSiO_4$ : k=11 vs.  $HfO_2$ : k=25). Furthermore, in contrast to  $Ba_2SiO_4$ , which for thermodynamic reasons guarantees the absence of  $SiO_2$  at the interface to Si (see section 2.2.1), the silicates of Y [41, 42], Hf, III, IIII, III

$\mathrm{HfO_2}$  has, however, also several drawbacks as a high-k gate oxide. Firstly, O vacancies lead to trap states close to the silicon conduction band [4]. Moreover, a  $\mathrm{SiO_2}$  layer forms at the interface to silicon due to the diffusion of O-atoms through the  $\mathrm{HfO_2}$  layer [11]. Although the  $\mathrm{SiO_2}$  layer has the upside of forming a well-defined interface to silicon

with a low defect concentration and can therefore be desirable in low thicknesses, it ultimately represents a serious limitation for the scaling to EOTs below 1 nm due to the associated decrease of the effective dielectric constant.

The search for alternative gate dielectrics is mainly focused on amorphous materials. The argument against polycrystalline layers is that the grain boundaries might lead to higher leakage currents and that they can furthermore serve as diffusion paths for dopants from the silicon making it easier for an electrical breakdown to occur [4]. However, most of the oxides that are considered as alternative gate dielectrics have crystallization temperatures well below 1000 °C, so that nanocrystalline layers can easily form during the device processing [4, 46]. In particular, HfO<sub>2</sub> crystallizes at 400 °C [4]. In order to increase the crystallization temperatures nitrogen is built into the oxides, which also lowers the diffusion rates of atoms inside the layers [47]. Nevertheless, no difference in the leakage currents of amorphous and nanocrystalline HfO<sub>2</sub> layers was found experimentally [48, 49].

### 2.2. Barium silicates

Barium silicates are ionic compounds with Ba-ions as cations and anions consisting of SiO<sub>4</sub>-tetrahedra. The various compounds are a mixture of BaO and SiO<sub>2</sub> in different ratios. Out of all the barium silicates, Ba<sub>2</sub>SiO<sub>4</sub>, which is the focus of this work, is the one with the highest Ba concentration. Its anions are single SiO<sub>4</sub>-tetrahedra, while the anions of the compounds with higher Si concentrations all consist of multiple SiO<sub>4</sub>-tetrahedra that are connected by an O-bridge, i.e. two tetrahedra share one O atom.

## 2.2.1. Thermodynamic stability

$Ba_2SiO_4$  is thermodynamically very stable. In particular, the reaction of the oxides  $SiO_2$  and BaO to silicate is exothermic, i.e. the heat of formation  $\Delta H$  from the oxides at room temperature (RT) is negative [18]:

$$2 \text{ BaO} + \text{SiO}_2 \rightarrow \text{Ba}_2 \text{SiO}_4, \quad \Delta H_{298 K} = -64.48 \text{ kcal/mol}$$

Moreover, it is generally thermodynamically more favorable to form a silicate than to keep  $SiO_2$  in the system:

$$\begin{array}{lll} 2 \; {\rm BaO} + 4 \; {\rm SiO_2} \; & \to \; {\rm Ba_2SiO_4} + 3 \; {\rm SiO_2}, & \Delta H_{298 \; K} = -64.48 \; {\rm kcal/mol} \\ & \to \; 2 \; {\rm BaSiO_3} + 2 \; {\rm SiO_2}, & \Delta H_{298 \; K} = -76.06 \; {\rm kcal/mol} \\ & \to \; {\rm Ba_2Si_3O_8} + {\rm SiO_2}, & \Delta H_{298 \; K} = -82.42 \; {\rm kcal/mol} \\ & \to \; 2 \; {\rm BaSi_2O_5}, & \Delta H_{298 \; K} = -82.56 \; {\rm kcal/mol} \end{array}$$

With respect to the growth of  $Ba_2SiO_4$  thin films on Si(001) this guarantees the absence of  $SiO_2$  at the interface. However, excess  $SiO_2$  does of course result in the formation of

a silicate with a higher Si concentration than Ba<sub>2</sub>SiO<sub>4</sub>, which can impede the epitaxial growth and could impact the performance of the thin films negatively. Therefore, the oxidation of the Si substrate cannot be disregarded. From the above data, the energy gain from the incorporation of SiO<sub>2</sub> into the silicate seems to saturate at Ba<sub>2</sub>Si<sub>3</sub>O<sub>8</sub>, at least at room temperature. However, for the growth of Ba<sub>2</sub>SiO<sub>4</sub> this would already represent an extreme SiO<sub>2</sub> surplus of more than three times the necessary amount, so that is unlikely to have an effect in this case.

The incorporation of BaO into the silicate is also generally thermodynamically favorable:

Since Ba<sub>2</sub>SiO<sub>4</sub> is, however, the barium silicate with the highest Ba concentration, excess BaO during the growth of Ba<sub>2</sub>SiO<sub>4</sub> would remain as BaO.

The heats of formation for the various silicate formations above were determined using the data from Barany *et al.* [18]. These considerations also demonstrate that for the growth of Ba<sub>2</sub>SiO<sub>4</sub> it is important to adjust the ratio of at least two of the three elements to avoid the formation of a different type of silicate.

## 2.2.2. Crystal structure and matching of $Ba_2SiO_4$ to Si(001)

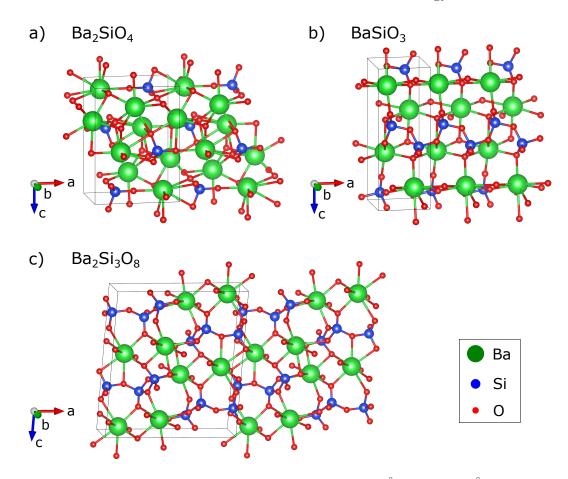

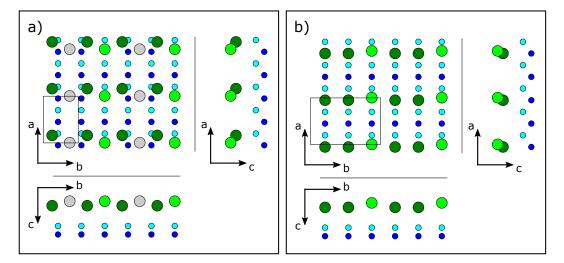

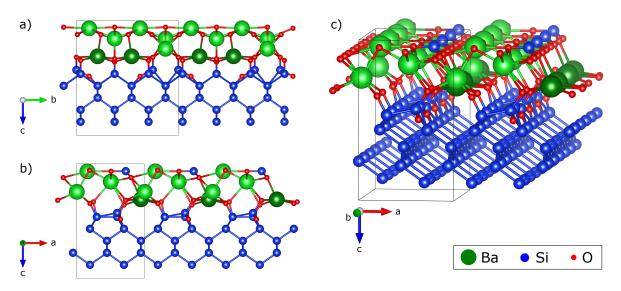

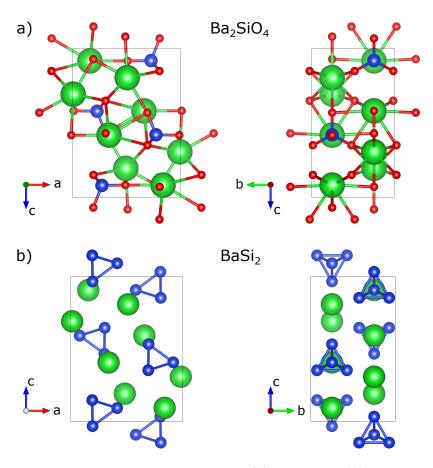

The crystal structure of Ba<sub>2</sub>SiO<sub>4</sub> is shown in Fig. 2.3a). As stated above, this is the only barium silicate crystal structure that has exclusively single SiO<sub>4</sub>-tetrahedra as anions. As an example the crystal structures of BaSiO<sub>3</sub>, which has infinite SiO<sub>4</sub>-tetrahedra chains, and Ba<sub>2</sub>Si<sub>3</sub>O<sub>8</sub>, which has chains of six SiO<sub>4</sub>-tetrahedra, are shown in Figs. 2.3b) and c), respectively, for comparison. This means that all O atoms in Ba<sub>2</sub>SiO<sub>4</sub> form exactly one bond to Si and one bond to Ba, while the other barium silicates all have a proportion of O atoms that form two bonds to Si. This fact can be used to calibrate the system by XPS (see sections 4.1 and 4.4).

$Ba_2SiO_4$  grows epitaxially on Si(001) with its c-axis normal to the surface [17, 1]. Disregarding the  $(2 \times 1)$  reconstruction, the Si(001) surface has a square symmetry with a lattice constant of  $a_{Si(001)} = 3.84$  Å in [110] direction. The lattice constants of  $Ba_2SiO_4$  along the a and b-axes are approximately equivalent to 2 and 1.5 times the Si(001) lattice constant, respectively. This means that, in principle, the  $Ba_2SiO_4$  lattice constant in a-direction fits approximately 1:1 with the  $(2 \times 1)$  reconstruction of the Si(001) surface, although it is not clear whether this reconstruction is maintained at the interface between an epitaxial  $Ba_2SiO_4$  film and Si(001). The exact lattice mismatch between  $Ba_2SiO_4$  and Si(001) depends on the source of the  $Ba_2SiO_4$  lattice constants. A comparison of different sources is done in table 2.1.

Figure 2.3.: Crystal structures of (a)  $\text{Ba}_2\text{SiO}_4$  (a=7.602 Å, b=5.884 Å, c=10.413 Å,  $\alpha=\beta=\gamma=90^\circ$ ), (b)  $\text{BaSiO}_3$  (a=4.638 Å, b=5.692 Å, c=12.708 Å,  $\alpha=\beta=\gamma=90^\circ$ ), (c)  $\text{Ba}_2\text{Si}_3\text{O}_8$  (a=12.665 Å, b=4.756 Å, c=14.149 Å,  $\alpha=\gamma=90^\circ$ ,  $\beta=93.472^\circ$ ). The wire boxes mark the unit cells. Drawn with VESTA [50] with data from [51, 52, 53].

| a / Å | $\mathrm{a/a_{Si(001)}}$ | b / Å | $\mathrm{b/a_{Si(001)}}$ | Source                  |

|-------|--------------------------|-------|--------------------------|-------------------------|

| 7.602 | 1.9797                   | 5.884 | 1.5323                   | Materials Project [51]  |

| 7.69  | 2.0026                   | 5.86  | 1.5260                   | Springer Materials [54] |

| 7.51  | 1.9557                   | 5.81  | 1.5130                   | Norton et al. [17]      |

| 7.498 | 1.9526                   | 5.805 | 1.5117                   | Pieper et al. [55]      |

Table 2.1.: Lattice constants a and b of  $\mathrm{Ba_2SiO_4}$  in Å and in multiples of the  $\mathrm{Si}(001)$  lattice constant  $\mathrm{a_{Si}}(001) = 3.84$  Å from different sources

## 2.3. Low energy electron diffraction

Low energy electron diffraction (LEED) is a method for studying the structure and morphology of surfaces. It was discovered by Davisson and Germer in 1927 [56] and has since become one of the most important surface science techniques. The technique

is based on the analysis of the interference pattern created by the elastic scattering of electrons on a crystal lattice. Monochromatic electrons are accelerated onto the sample and the resulting diffraction pattern is either made visible with a fluorescent screen or recorded with a channel electron multiplier (CEM). A retarding grid ensures that only elastically scattered electrons reach the screen or the CEM.

Low energy electrons with energies between 50-200 eV are used for two reasons: First, their de Broglie wavelength [57]

$$\lambda(\text{Å}) = \sqrt{\frac{150.4}{E(\text{eV})}} \tag{2.4}$$

is between  $0.9 \text{ Å}\ (200 \text{ eV})$  and  $1.7 \text{ Å}\ (50 \text{ eV})$ , and therefore in the dimensions of the typical lattice constants in crystals, making it possible for diffraction phenomena to occur. Second, due to the short mean free path between approximately 0.4 and 0.9 nm, which corresponds to about two to four monolayers, of the electrons in this energy range they are highly surface sensitive [58].

### 2.3.1. Kinematic approximation and Ewald construction

The kinematic approximation is a simple method to describe the diffraction on a crystal, that only considers single scattering. The diffraction from the atoms at the positions  $\vec{r}(n)$  can be described as a sum of electron wave functions with the incident wave vector  $\vec{k}_i$  and the scattering vector  $\vec{K}$ , which is defined as the difference of the incident wave vector and the final wave vector  $\vec{k}_f$ , as follows [57]

$$\Psi(\vec{K}, \vec{k}_i) = \sum_{n} f(n, \vec{K}, \vec{k}_i) \exp\left(i\vec{K} \cdot \vec{r}(n)\right), \qquad (2.5)$$

where  $f(n, \vec{K}, \vec{k_i})$  is the structure factor at the positions  $\vec{r}(n)$ . The absolute square of this wave function gives the intensity of the diffraction spots [57]

$$I(\vec{K}, \vec{k}_i) = |\Psi(\vec{K}, \vec{k}_i)|^2 = \sum_{n,m} f(n, \vec{K}, \vec{k}_i) f^*(m, \vec{K}, \vec{k}_i) \exp\left(i\vec{K} \cdot (\vec{r}(n) - \vec{r}(m))\right)$$

(2.6)

This also means that the phase information is unfortunately lost in the diffraction experiment, so that an unambiguous reconstruction of the real space structure is not possible.

The diffraction spot intensity assumes a local maximum, i.e. diffraction spots are observed, when the Laue condition

$$\vec{K} = \vec{k}_i - \vec{k}_f = \vec{G} \tag{2.7}$$

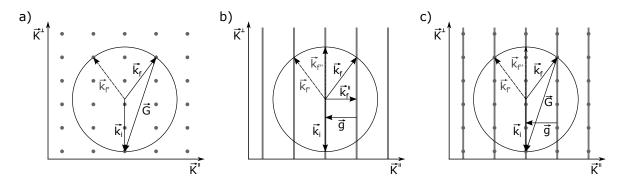

Figure 2.4.: Ewald construction for the scattering on a 3D crystal (a), a 2D crystal (b) and the scattering of low energy electrons on a real surface (c). There are multiple final wave vectors  $\vec{k}_f$  for a given incident wave vector  $\vec{k}_i$ . The reciprocal lattice vector is only drawn for one final wave vector.

is fulfilled, where  $\vec{G}$  is a reciprocal lattice vector, for which  $\vec{G}_a \cdot \vec{R}_b = 2\pi \delta_{a,b} N$ , a,b=1,2,3 holds, with  $\vec{R}$  being a real space lattice vector,  $\delta_{a,b}$  being the Kronecker delta and N being an integer. A graphic determination of all occurring  $\vec{k}_f$  for a given  $\vec{k}_i$  is possible with the Ewald construction (see Fig. 2.4a)), which is obtained as follows: The vector  $\vec{k}_i$  is drawn into the reciprocal lattice in such a way that its end point coincides with a reciprocal lattice point. Then a sphere with the radius  $|\vec{k}_i|$ , which represents the conservation of energy during the elastic scattering process, is drawn around the starting point of the vector. Every reciprocal lattice point intersected by this sphere becomes the end point of a final wave vector  $\vec{k}_f$ , whose common starting point is the same as that of the incident wave vector.

In the case of the scattering on a two-dimensional lattice, the Laue condition only applies to the components of the wave vectors parallel to the surface

$$\vec{K}^{\parallel} = \vec{k}_i^{\parallel} - \vec{k}_f^{\parallel} = \vec{g},$$

(2.8)

where  $\vec{g}$  is the reciprocal lattice vector of the two-dimensional crystal. Since the periodicity perpendicular to the surface is infinite, the distance between the reciprocal lattice points becomes infinitely small, resulting in Ewald rods and a modified Ewald construction as shown in Fig. 2.4b). As a consequence, the diffraction on a two-dimensional lattice leads to generally more diffraction spots than the diffraction on a three-dimensional lattice.

The diffraction of low energy electrons on a real surface, while dominated by the surface, is still affected by the first few atomic layers below the surface due to the small penetration depth. This leads to an intensity modulation of the Ewald rods as indicated in Fig. 2.4c). A diffraction spot is observed when the Laue condition is fulfilled for the components of the wave vectors parallel to the surface. If it is also fulfilled for the vertical component, the intensity of the diffraction spot assumes a maximum.

The kinematic approximation is sufficient to describe the positions of the diffraction spots. However, the strong interaction of the electrons with the solid necessary for the

high surface sensitivity also results in strong multi scattering effects, which are not considered in the kinematic approximation [59]. Therefore, a detailed description of the spot intensity, which in needed in particular for the determination of the positions of the atoms in the unit cell, requires the more sophisticated dynamic LEED theory, which takes multi scattering into account (see e.g. [60, 61]).

#### 2.3.2. The SPA-LEED instrument

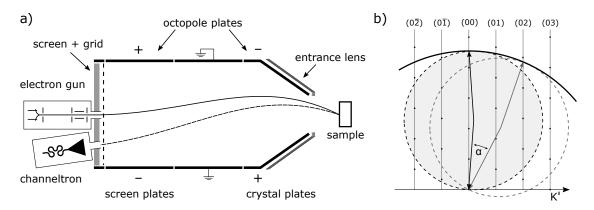

Figure 2.5.: The Spot Profile Analyzing LEED: (a) Illustration of a SPA-LEED instrument with an octupole deflection unit. (b) Modified Ewald construction in the case of the SPA-LEED in reciprocal space. As the deflection voltage is changed, the incident and final wave vectors move together drawing a circle (thick black line) around the starting point of the incident wave vector. The dashed lines mark the size of the regular Ewald sphere (see Fig. 2.4). [62, 63, 57]

In this work a Spot Profile Analyzing LEED (SPA-LEED), which is illustrated in Fig. 2.5a), is used to record LEED patterns. Electrons with energies between 10 and 500 eV are accelerated onto the sample surface by an electron gun. The scattered electrons are detected with a channel electron multiplier, also referred to as a channel tron, which is mounted at an angle of 4° to the electron gun. A grid in front of the detector ensures that only elastically scattered electrons are detected.

Between the electron gun and the sample sits the octupole deflection unit, which consists of three octupoles in series. Each octupole in turn consists of four plate capacitors arranged in angles of  $45^{\circ}$  to each other around the electron path. All plates of the middle octupole are grounded. The outer octupoles are polarized opposite to each other, thereby forcing the electrons on a parabolic path if a deflection voltage is applied. By varying the deflection voltages, the angle in which the electrons hit the surface, and thus the component of the respective wave vector parallel to the surface, can be changed, both in x and in y direction, making it possible to scan the reciprocal space [62, 63].

As the deflection voltage is changed, both the incidence and the reflection angle are varied by the same amount. As a result, in reciprocal space the incident wave vector and the final wave vector are turned together, with the angle between them remaining

constant, which creates a modified Ewald construction with twice the radius of the regular Ewald sphere [57] as illustrated in Fig. 2.5b). Consequently, at the same energy the SPA-LEED measures a larger area of the reciprocal space than the conventional LEED. Moreover, the (00)-spot is recorded by the SPA-LEED, which is covered by the shadow of the electron gun in a conventional LEED.

If the deflection unit is switched off, the SPA-LEED can be used like a regular LEED by using the built-in screen instead of the channeltron to detect the electrons. This mode is mainly meant for maintenance. Moreover, there is an entrance lens that can be used to focus the electron beam on the sample, in order to correct for an inaccurate sample position.

### 2.3.3. Interpretation of LEED patterns

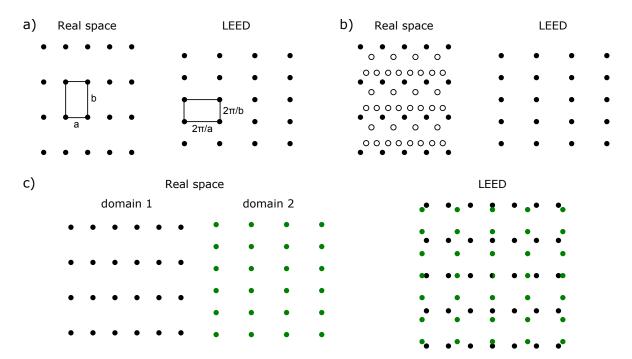

Figure 2.6.: Interpretation of LEED patterns: (a) A rectangular lattice in real and in reciprocal space. (b) The content of the unit cell, indicated with unfilled circles, does not affect the positions of the diffraction spots, only the intensities. (c) Two domains with rectangular lattices, turned by 90° to each other. The LEED image is a superposition of the corresponding reciprocal lattices.

The LEED pattern represents the reciprocal lattice of the investigated surface. With a regular LEED this is achieved by choosing an angle of incidence of  $0^{\circ}$  to the surface normal, so that  $|\vec{k}_i^{\parallel}| = 0$ . From equation 2.8 it then follows that the final wave vectors  $\vec{k}_f^{\parallel}$  that lead to diffraction spots are equal to reciprocal lattice vectors. Hence, the LEED pattern becomes a representation of the reciprocal lattice. With a SPA-LEED this is achieved with the octupole deflection system. The joint rotation of the incident

and final wave vectors in reciprocal space shown in Fig. 2.5b) can also be viewed as the rotation of the scattering vector  $\vec{K}$ , i.e. varying the deflection voltage of the octupole plates changes  $\vec{K}^{\parallel}$ . Thus, according to equation 2.8 the diffraction spots sit at the endpoints of reciprocal lattice vectors that start at the origin.

In the LEED pattern, a real space length a is represented by the reciprocal length  $2\pi/a$ . As illustrated in Fig 2.6a), this means that, while a rectangular real space lattice remains rectangular in the LEED pattern, the shorter side becomes the longer side and vice versa. Moreover, the arrangement of the LEED spots only represents the lattice of the investigated crystal. The contents of the unit cell, which are indicated in Fig 2.6b) with unfilled circles, do not affect the spot positions, but only their intensities. Lastly, real surfaces often feature more than one crystal domain, e.g. two rectangular lattices with the same lattice constants but at an angle of  $90^{\circ}$  to each other as illustrated in Fig 2.6c). In that case, the LEED pattern is a superposition of the reciprocal lattices.

## 2.4. X-ray photoelectron spectroscopy

X-ray photoelectron spectroscopy (XPS) is a type of photoelectron spectroscopy that uses photons with energies in the 1–2 keV range, which is high enough to release electrons from the atomic core levels. For this reason, the energies of the ejected electrons are characteristic of the chemical element they originate from, which enables a determination of the chemical composition of a sample by comparing the energies of the elastic peaks in the XPS spectrum with literature (for example Refs. [64, 65]). Moreover, small shifts of the elastic peaks depending on the chemical environment allow for a determination of the chemical bonding state of the respective atoms.

XPS is a surface sensitive technique, which is a result of the mean free path of the ejected photoelectrons. However, it is not quite as surface sensitive as SPA-LEED, due to the generally higher kinetic energy of the electrons. The contribution of each layer below the surface to the overall signal decreases exponentially with the combined thickness of the overlying layers, with the first approximately 6 nm contributing 95% of the signal [66]. This can also be used to estimate the thickness of thin films by measuring the intensity of a substrate peak.

## 2.4.1. Binding energy of core level peaks

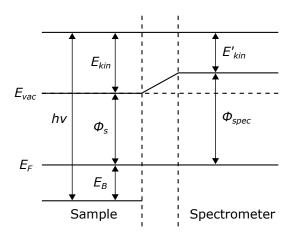

XPS is based on the photoelectric effect. In the simplest description, a photon with the energy  $h\nu$  hits a surface and is absorbed by an electron with the binding energy  $E_B$ . If the photon energy is larger than the sum of the binding energy of the electron and the work function  $\Phi_s$  of the sample, the electron is released from the solid. It follows from the conservation of energy that

$$h\nu = E_B + E_{kin} + \Phi_s, \tag{2.9}$$

where  $E_{kin}$  is the kinetic energy of the photoelectron after it is released from the solid

Figure 2.7.: Energy level diagram for the emission of a photoelectron and its detection by a spectrometer

and  $E_B$  and  $E_{kin}$  are given with respect to the Fermi level. The kinetic energy is then measured in a spectrometer that is in electrical contact with the sample, i.e. their fermi levels are aligned. Since the work functions of the sample  $\Phi_s$  and the spectrometer  $\Phi_{spec}$  are generally not identical, a contact potential is formed between the sample and the spectrometer (see Fig. 2.7), which leads to the kinetic energy  $E'_{kin}$  measured by the spectrometer being different from  $E_{kin}$  as defined above. The kinetic energies are related by  $E'_{kin} + \Phi_{spec} = E_{kin} + \Phi_s$ , so that

$$h\nu = E_B + E'_{kin} + \Phi_{spec}. \tag{2.10}$$

The kinetic energy scale of the spectrometer is then usually shifted either in the software or directly in the electronics so that the work function of the spectrometer  $\Phi_{spec}$  is eliminated, thus simplifying the determination of the binding energy:

$$E_B = h\nu - E'_{kin}. (2.11)$$

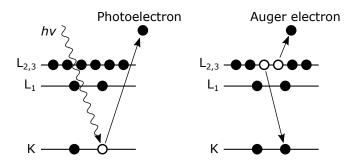

## 2.4.2. Auger peaks

Auger peaks are a second type of peak that appear in an XPS spectrum in addition to the core level peaks as a result of the atoms being in an excited state after a core electron has been ejected. In the Auger process an excited state of an atom decays radiation-free with the emission of a second electron. An example is illustrated in Fig. 2.8. After a core level electron has been ejected by means of the photoelectric effect, the resulting vacancy in the inner shell is filled by an electron from a shell with a higher energy. The energy that is released is transferred to another electron, which is thereby emitted from the atom. The corresponding Auger peaks are labeled with the shells involved. For the process in the example this would be  $KL_{2,3}L_{2,3}$ , with the first letter indicating the shell with the initial vacancy, the second letter indicating the shell from which the first electron decays and the third letter indicating the shell from

Figure 2.8.: Auger process: After an electron is released by photoemission (left), the vacancy is filled by an electron from a higher energy level, which releases enough energy for a second electron, the Auger electron, to be ejected from the atom (right).

which the second electron, i.e. the Auger electron, is ejected. A V is used for electrons in the valence band.

The kinetic energy of the Auger electron is independent of the energy  $h\nu$  of the incident photon, since the photon is not directly involved in the Auger process. Let A, B and C be the energy levels involved (in the example in Fig. 2.8 A, B, C = K,  $L_{2,3}$ ,  $L_{2,3}$ ) and  $E_A$ ,  $E_B$  and  $E_C$  be the corresponding binding energies. Then  $E_A - E_B$  is the energy released through the decay, which is transferred to the Auger electron. In the simplest description, the kinetic energy of the Auger electron can thus be approximated as

$$E_{ABC} \approx E_A - E_B - E_C. \tag{2.12}$$

In a more complete picture, which takes into account the interaction of holes in the final state and screening effects, the kinetic energy of the Auger electron is given by [67]

$$E_{ABC} = E_A - E_B - E_C - E_{BC,x} + R_{x,in} + R_{x,ex}, (2.13)$$

where  $E_{BC,x}$  is the energy of the interaction of the holes in B and C in the final state x and  $R_{x,in}$  and  $R_{x,ex}$  are the intra- and extra-atomic relaxation energies.

## 2.4.3. The XPS spectrum

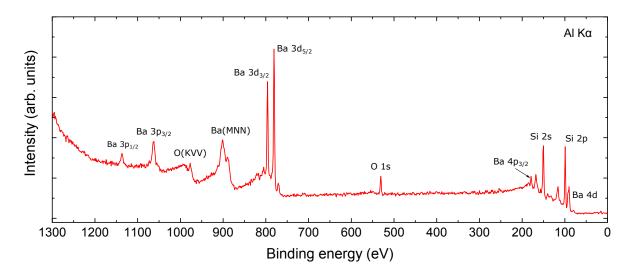

An XPS overview spectrum of a  $Ba_2SiO_4$  thin film with a thickness of 1 nm on Si(001) is shown in Fig. 2.9 as an example. It was recorded with an Al K $\alpha$  source. The sharp peaks are due to elastically scattered photoelectrons and can be assigned to a core level of one of the three elements. Silicon has two core level peaks, Si 2s and Si 2p, in the given energy range (They actually originate from the substrate. The intensities of the thin film Si contributions are too low for them to be visible in the plot. See also section 4.8). Furthermore, there is one oxygen peak, the O 1s peak, and several barium peaks. Most of the barium peaks are split into doublet peaks due to the spin—orbit interaction. For example, the Ba 3d peak is split into a Ba  $3d_{3/2}$  and a Ba  $3d_{5/2}$  peak. In

Figure 2.9.: XPS spectrum of a 1 nm thick Ba<sub>2</sub>SiO<sub>4</sub> thin film on Si(001)

addition, there are two Auger peaks in the spectrum, the O(KVV) and the Ba(MNN) peaks.

An x-ray source is typically equipped with an Al/Mg dual anode. Their main emission lines are at 1486.6 eV for Al and 1253.6 eV for Mg. The dual anode makes it possible to differentiate between core level peaks and Auger peaks by changing the excitation energy. Since the energy of the Auger electrons is independent of the photon energy, the core level peaks and the Auger peaks shift relative to each other when the excitation energy is changed. In the binding energy scale the core level peaks remain at the same energy, while the Auger peaks are shifted by 233 eV, i.e. the difference between the excitation energies. This seems counterintuitive at first. However, one has to keep in mind that the binding energy is only defined for the core level peaks, and has no meaning with respect to the Auger peaks.

The background of the spectrum is due to inelastically scattered electrons. It increases towards low kinetic energies, i.e. high binding energies. The reason for the large background is that, while the elastic peaks are almost exclusively due to electrons originating from the first few nanometers of the sample because of their short mean free path, the incident x-rays actually have a much higher penetration depth. This leads to a large contribution of inelastically scattered electrons from the lower layers.

## 2.4.4. Core level peak shapes and shifts

#### Relaxation shifts

The kinetic energy of the emitted photoelectron according to the equations 2.9 and 2.10 is only correct if Koopman's theorem is fulfilled, which assumes that after the ionization of the atom all other electrons remain in the same state as before the ionization. In reality this is, however, not the case. The main reason for this is the so-called relaxation shift. First, the core hole created by photoemission is screened by core electrons in

other states relaxing in energy to lower states, which makes more energy available to the emitted photoelectron. This intra-atomic relaxation shift is represented by an energy  $E_a$  [68]

$$E'_{kin} = h\nu - E_B - \Phi_{spec} + E_a. \tag{2.14}$$

Furthermore, the weaker bound valence electrons, which in the case of an atom in a solid are involved in the bond formation with other atoms, will also screen the core hole. This leads to an additional inter-atomic relaxation shift represented by the energy  $E_r$  [68]

$$E'_{kin} = h\nu - E_B - \Phi_{spec} + E_a + E_r. \tag{2.15}$$

The relaxation shifts are much smaller than the binding energy. Typically,  $E_B$  is several hundred eV while  $E_a$  and  $E_r$  are only a few eV.

#### The chemical shift

The chemical shift is an experimentally very important shift of the core level peaks depending on the local chemical and electronic environment of the associated atoms, which allows for a determination of their chemical bonding state. There are two contributions to the chemical shift. First, there is the inter-atomic relaxation shift discussed above, which depends on the neighboring atoms. Second, there is the 'true chemical shift', which is a shift of the original binding energy due to the bonds formed to other atoms [68]. The bond formation leads to the electron density in the outer shells either increasing or decreasing. If it decreases, the associated reduction of the effective negative charge around the nucleus results in the core level electrons being bound more tightly, i.e. their binding energy increases, and vice versa. Both contributions are significant for the overall shift and the inter-atomic relaxation shift can even surpass the 'true chemical shift' [69]. The 'true chemical shift' between the bonding states i and j of an atom is the difference of the respective binding energies [68]

$$\Delta E_B = E_{B,i} - E_{B,j} = E'_{kin,j} - E'_{kin,i}. \tag{2.16}$$

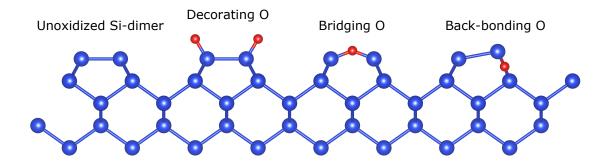

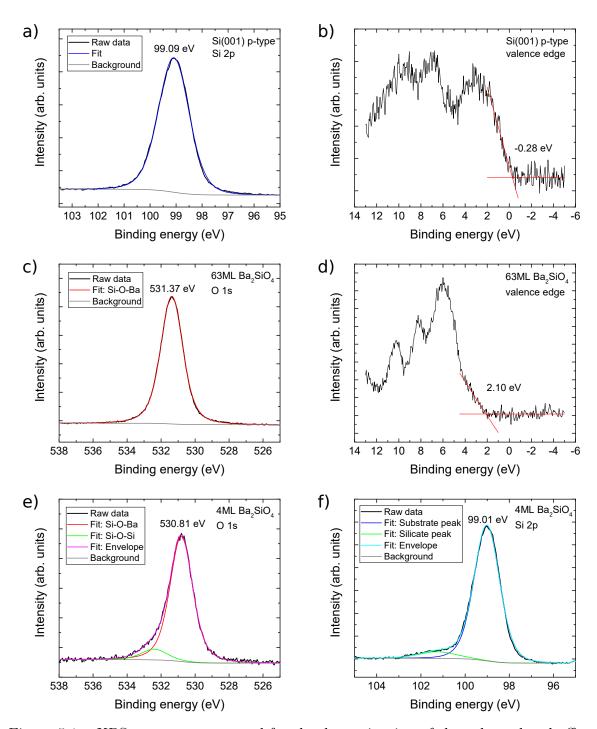

Since XPS measures core level electrons, only the combined effect of all bonds of the atom is measured, i.e. bonds are not measured directly. For example, there is no unique O 1s peak associated with Si-O bonds. Since O-atoms form two bonds, there are different peaks for e.g. Si-O-Si and Si-O-Ba bonding states (see also section 4.1).

#### Satellite features of core level peaks

There are several satellite features that can accompany a core level peak. Since the emission of a photoelectron is a rapid process, the system does not necessarily reach a stable equilibrium at the point the photoelectron is emitted. One such excited state is the creation of electron-hole pairs around the Fermi level, which reduces the energy of the emitted photoelectron. This leads to satellite peaks, so-called shake-up features,

close to the main core level peak at lower kinetic energies, creating an asymmetric peak shape [68]. Another possible excited state is the creation of bulk or surface plasmons, which gives rises to plasmon loss features at lower kinetic energies than the main peak [68]. The plasmon loss satellites have an even lower kinetic energy than the shake-up features, so that they can usually be visually distinguished from the main peak.

Furthermore, there are satellites at higher kinetic energies, due to the source not being completely monochromatic. In addition to the main  $K\alpha_{1,2}$  line, the Al and Mg targets also produce several weaker lines resulting from less likely transitions. The positions and intensities relative to the main  $K\alpha_{1,2}$  line are listed in table 2.2. The most important ones are in both cases the  $K\alpha_3$  and  $K\alpha_4$  lines, which produce the most intense satellite peaks.

|                           |                         | Al               | $\overline{\mathrm{Mg}}$ |               |  |

|---------------------------|-------------------------|------------------|--------------------------|---------------|--|

| Line                      | $\Delta E \text{ (eV)}$ | Intensity $(\%)$ | $\Delta E \text{ (eV)}$  | Intensity (%) |  |

| $\overline{\alpha_{1,2}}$ | 0                       | 100              | 0                        | 100           |  |

| $\alpha_{1,2}$ $\alpha'$  | 5.8                     | 0.7              | 4.6                      | 1.0           |  |

| $\alpha_3$                | 9.7                     | 7.3              | 8.5                      | 9.1           |  |

| $\alpha_4$                | 11.7                    | 3.1              | 10.1                     | 5.1           |  |

| $\alpha_5$                | 20.0                    | 0.41             | 17.4                     | 0.76          |  |

| $\alpha_6$                | 23.6                    | 0.28             | 20.6                     | 0.48          |  |

| $\beta$                   | 70.6                    | 0.76             | 48.6                     | 0.55          |  |

Table 2.2.: Relative energies and intensities of the  $K\alpha$  satellites and  $K\beta$  bands for Al and Mg [70]

## 2.4.5. Intensity of core level peaks

The intensity of the core level peak for the state A in the case a laterally homogeneous sample is given by [71]

$$I_A = \kappa \cdot T(E_A) \cdot \sigma_A \int_{z=0}^{\infty} c_A(z) \cdot \exp\left(-\int_{z'=0}^{z} \frac{1}{\lambda(E_A, z')\cos(\vartheta)} dz'\right) dz, \qquad (2.17)$$

where  $c_A$  is the concentration of the Element A,  $\sigma_A$  is the photoionization cross section of the state A,  $\lambda(E_A)$  is the mean free path of electrons with the kinetic Energy  $E_A$ of the core level peak A in the material the electrons pass through,  $T(E_A)$  is the transmission function of the analyzer for electrons with the kinetic energy  $E_A$ ,  $\vartheta$  is the angle between the normal of the sample surface and the analyzer, and  $\kappa$  is a devicespecific constant.

For single phase samples  $c_A$  and  $\lambda(E_A)$  can be assumed to be isotropic, so that the equation can be simplified [66]:

$$I_{A} = \kappa \cdot T(E_{A}) \cdot \sigma_{A} \cdot c_{A} \int_{z=0}^{\infty} \exp\left(-\frac{1}{\lambda(E_{A})\cos(\vartheta)} \cdot \int_{z'=0}^{z} 1 \, dz'\right) \, dz$$

$$= \kappa \cdot T(E_{A}) \cdot \sigma_{A} \cdot c_{A} \int_{z=0}^{\infty} \exp\left(-\frac{z}{\lambda(E_{A})\cos(\vartheta)}\right) \, dz$$

$$= \kappa \cdot T(E_{A}) \cdot \sigma_{A} \cdot c_{A} \cdot \left[-\lambda(E_{A})\cos(\vartheta) \cdot \exp\left(-\frac{z}{\lambda(E_{A})\cos(\vartheta)}\right)\right]_{z=0}^{\infty}$$

$$= \kappa \cdot T(E_{A}) \cdot \sigma_{A} \cdot c_{A} \cdot \lambda(E_{A}) \cdot \cos(\vartheta)$$

$$(2.18)$$

This means that the sensitivity of the instrument is determined by three factors: The photoionization cross section  $\sigma_A$ , the mean free path  $\lambda(E_A)$  and the transmission function  $T(E_A)$  of the spectrometer. In order to compare the intensities of different core level peaks, relative sensitivity factors  $RSF(A) \propto \sigma_A \lambda(E_A) T(E_A)$  are defined so that

$$c_A \propto \frac{I_A}{\sigma_A \cdot \lambda(E_A) \cdot T(E_A)} \propto \frac{I_A}{RSF(A)}$$

(2.19)

Usually the relative sensitivity factors are defined so that either RSF(F1s) = 1 or RSF(C1s) = 1. The RSFs can be used to determine relative intensities of the elements in the sample. The accuracy of this method greatly depends on the accuracy with which  $\lambda(E_A)$  is known. The mean free path  $\lambda(E_A)$  is usually assumed to be a universal function [58]. However, there can be rather large deviations from the universal function, especially for complex oxides like  $Ba_2SiO_4$ .

## 2.4.6. Determination of the layer thickness

The thickness of a thin film can be determined with XPS by measuring the damping of a substrate peak. For a homogeneous layer with thickness d this damping of the substrate peak intensity is given by [67]

$$I_{sub}(d) = I_{sub}(0) \cdot \exp\left(-\frac{d}{\lambda(E) \cdot \cos(\vartheta)}\right),$$

(2.20)

where  $I_{sub}(d)$  is the intensity of the substrate peak with the thin film and  $I_{sub}(0)$  is the intensity of the same substrate peak but without the thin film both measured under identical conditions,  $\lambda(E)$  is the mean free path of electrons in the thin film at the kinetic energy of the substrate peak and  $\vartheta$  is the angle between the sample surface normal and the analyzer. Thus, by measuring  $I_{sub}(d)$  and  $I_{sub}(0)$  the film thickness can be determined via

$$d = \lambda(E) \cdot \cos(\vartheta) \cdot \ln\left(\frac{I_{sub}(0)}{I_{sub}(d)}\right). \tag{2.21}$$

Since this method requires the substrate to be visible in XPS, it only works for film thicknesses of up to approximately 10 nm. Ideally,  $I_{sub}(d)$  should be determined for several thicknesses with known ratios in order to increase the accuracy of the method.

The mean free path can be looked up in the NIST Electron Inelastic-Mean-Free-Path Database [72].

## 2.5. Underlying theory of the electrical characterization

### 2.5.1. The different regions of a MOS capacitor and the CV-curve

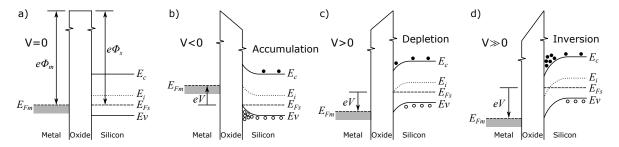

Figure 2.10.: Band diagrams of a metal oxide semiconductor (MOS) capacitor with a p-type semiconductor: (a) Equilibrium state for the case that the work functions of the metal and the semiconductor are identical. If a voltage is applied, three regions can be distinguished: (b) accumulation, (c) depletion and (d) inversion. Based on [73, 26].

The band diagram of a MOS capacitor for the example of p-type silicon is shown in Fig. 2.10a). In the context of a MOS capacitor it is convenient to define modified work functions  $\Phi_m$  and  $\Phi_s$ , whose energies are measured from the Fermi level to the conduction band of the oxide as shown in the figure [73]. In this idealized example the work functions of the metal and the semiconductor are the same, so that there is no band bending of the semiconductor bands in the equilibrium state.

The MOS structure works essentially like plate capacitor, where one plate is replaced by a semiconductor. By applying a voltage to the metal, charge is deposited on the metal, which induces an equal charge of opposite sign in the semiconductor. Three main regions can be distinguished, which are discussed in the following for the example of a p-type semiconductor. If the voltage applied to the metal is negative, the band edges of the semiconductor bend upwards at the interface to the oxide, which leads to a hole accumulation near the interface (Fig. 2.10b)) [73]. This voltage region, where the density of the majority carriers is increased near the interface, is called accumulation. Since (in the ideal case) no current flows through the oxide, the Fermi level of the semiconductor remains straight. If a small positive voltage is applied, the bands of the semiconductor bend downward, leading to a depletion of the majority carriers (Fig. 2.10c)) [73]. Hence, this region is called depletion. When the positive voltage is increased further, the intrinsic level  $E_i$  eventually crossed the Fermi level of the semiconductor  $E_{Fs}$  (Fig. 2.10d)). At this point the minority carrier density (electrons) at the interface is larger than the majority carrier density (holes), i.e. the interface is inverted [73]. This region is called *inversion*.

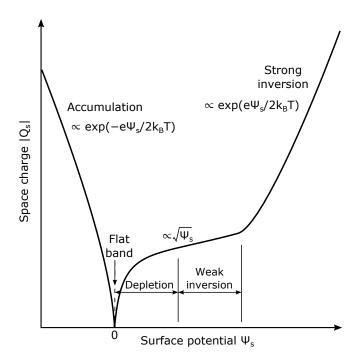

Figure 2.11.: Space charge at the semiconductor-oxide interface in a MOS capacitor versus the surface potential for p-type silicon. [26, 74]

For an n-type semiconductor the bands bend in same direction. However, since the majority carriers are electrons instead of holes, accumulation occurs at positive voltages, while depletion and inversion occur at negative voltages. Moreover, if the work functions of the metal and the semiconductor are not the same, the voltage at which the semiconductor bands are not bend, and thus the voltage at which the transition between accumulation and depletion happens, is different from zero. This voltage is called the flat band voltage  $V_{fb}$ . In the idealized case that there is no additional charge in the oxide or at the oxide-semiconductor interface, it is equal to the difference in the work functions [73]

$$V_{fb} = \Phi_m - \Phi_s. \tag{2.22}$$

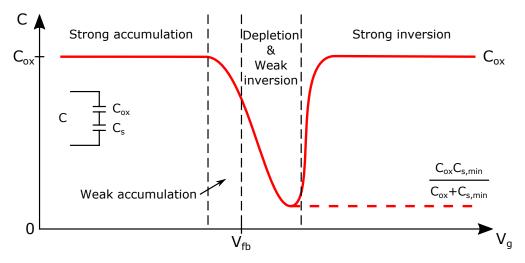

The capacitance of a MOS structure is the series connection of a voltage-independent conductance due to the oxide  $C_{ox}$  and a voltage-dependent conductance due to the space charge at the semiconductor surface  $C_s$ , which is given by the change of the space charge  $Q_s$  with the surface potential  $\Psi_s$  [73]

$$C_s = \frac{dQ_s}{d\Psi_s}. (2.23)$$

Fig. 2.11 shows the dependence of the space charge for a p-type substrate on the surface potential, which is related to the voltage  $V_g$  applied to the metal gate by  $\Psi_s = V_g - V_{fb}$ . The space charge is zero at the flat band condition. In the accumulation region it depends exponentially on the surface potential. In depletion and weak inversion, the

Figure 2.12.: Capacitance-gate voltage curve for a MOS capacitor with a p-type semiconductor substrate. The dashed red line is observed at high measurement frequencies. Based on [73].

surface charge is dominated by ionized dopants, so that it changes with the square root of the surface potential. Finally, in the strong inversion region it becomes exponentially dependent on the surface potential again. In the regions where the space charge depends exponentially on the surface potential the semiconductor capacitance  $C_s$  becomes very large, so that the overall capacitance of the MOS structure becomes basically equal to the oxide capacitance  $C_{ox}$  in strong accumulation and strong inversion [73] as seen in Fig. 2.12. However, if the measurement frequency is so high that the generation and recombination of the minority carriers in the inversion layer cannot follow the voltage changes, the measured conductance in the strong inversion region remains dominated by the contribution of ionized dopants (dashed red line in Fig. 2.12). In-between these two extremes the capacitance of the MOS structure changes as shown in the figure due to the variation of the semiconductor capacitance with the gate voltage. For n-type substrates the CV-curve is mirrored at the  $V_g = V_{fb}$  line.

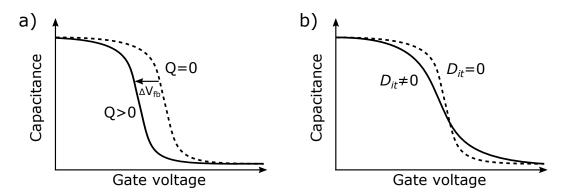

Furthermore, the CV-curve is influenced by charges in the oxide. Charge either in the oxide bulk or at the interface to the semiconductor induces a charge of opposite sign in the semiconductor, which leads to a shift in the flat band voltage and thereby in the CV-curve. Positive charge in the oxide shifts the flat band voltage towards negative voltages, while negative charge in the oxide shifts it towards positive voltages (see Fig. 2.13a)). For a charge  $Q_i$  at the interface to the semiconductor and a charge density  $\rho_{ox}$  distributed in the oxide, equation 2.22 changes to [25]

$$V_{fb} = \Phi_m - \Phi_s - \frac{Q_i}{C_{ox}} - \frac{1}{C_{ox}d} \int_0^d x \rho_{ox}(x) dx, \qquad (2.24)$$

where  $C_{ox}$  is the oxide capacitance and d is the thickness of the oxide. Moreover, if interface trap states are present, they have to be charged in addition to the space charge layer, which leads to a stretch-out of the CV-curve as shown in Fig. 2.13b).

Figure 2.13.: Effect of oxide charges on the CV-curve: (a) Charge in the oxide or at the interface to the semiconductor shifts the CV-curve. Positive oxide charge shifts it towards negative gate voltages and vice versa. (b) Interface trap states lead to a stretch-out of the CV-curve. Based on [75].

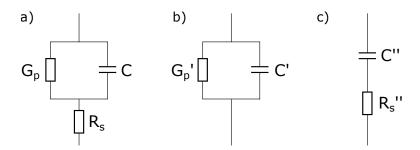

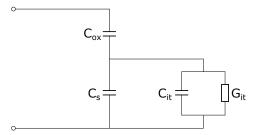

#### 2.5.2. Three-element model and correction for series resistance

Figure 2.14.: Equivalent circuit diagrams for (a) the three-element model, (b) a two-element model with a conductance and a capacitance connected in parallel and (c) a two-element model with a conductance and a resistance connected in series.

The three-element model, whose equivalent circuit diagram is shown in Fig. 2.14a), is a model for the measurement of the capacitance of an insulator thin film, that takes the simultaneous presence of the conductance through the oxide due to leakage  $G_p$  and a series resistance  $R_s$ , which represents the resistance due to the spreading resistance in the silicon wafer [76] and the contact resistances, to which the resistance between the wafer backside and the chuck makes generally the greatest contribution, into account. Its use becomes necessary for the capacitance measurement of a thin oxide layer with high leakage currents, since the high frequency of the alternating voltage used to minimize the influence of the leakage current results in an increased contribution of the series resistance due to the low impedance of the capacitor. Disregarding the series resistance unjustifiably would lead to a dependency of the accumulation capacitance of the CV-curve on the measurement frequency, making an accurate determination of the accumulation capacitance impossible [77].

The measurement at a single frequency, however, only gives an unambiguous result for

a two-element model, i.e. a model with a capacitance and a conductance connected in parallel (see Fig. 2.14b)) or one with a capacitance and a resistance in series (see Fig. 2.14c)) [77]. Therefore, the CV-curves are initially measured assuming only a two-element model with a parallel conductance as shown in Fig. 2.14b) (see section 3.3.3) and then corrected for the series resistance afterwards. For this correction, a frequency dependent  $(10^2-10^6~{\rm Hz})$  measurement of the absolute value |Z| and the phase  $\phi$  of the impedance is done at a fixed voltage in strong accumulation, since in this regime the contribution of substrate and interface traps can be ignored and the series resistance has the largest effect.

**Determination of the series resistance:** The impedance Z of the three element model is given by the parallel connection of the impedances of the conductance  $Z_1 = G_p^{-1}$  and the capacitance  $Z_2 = (i\omega C)^{-1}$ , which is connected in series with  $Z_3 = R_s$ :

$$Z = (Z_1^{-1} + Z_2^{-1})^{-1} + Z_3$$

$$= (G_p + i\omega C)^{-1} + R_s$$

$$= \frac{G_p - i\omega C}{G_p^2 + \omega^2 C^2} + R_s$$

$$= R_s + \frac{G_p}{G_p^2 + \omega^2 C^2} + i\frac{-\omega C}{G_p^2 + \omega^2 C^2},$$

(2.25)

where  $\omega = 2\pi f$  is the corresponding angular frequency of the measurement frequency f. Equation 2.26 can then be used to determine expressions for the absolute value |Z| and the phase  $\phi$  of the impedance:

$$|Z| = \left[ \left( R_s + \frac{G_p}{G_p^2 + \omega^2 C^2} \right)^2 + \left( \frac{-\omega C}{G_p^2 + \omega^2 C^2} \right)^2 \right]^{1/2} = \left[ R_s^2 + \frac{2R_s G_p + 1}{G_p^2 + \omega^2 C^2} \right]^{1/2} \quad (2.27)$$

$$\phi = \arctan\left(\frac{\frac{-\omega C}{G_p^2 + \omega^2 C^2}}{R_s + \frac{G_p}{G_p^2 + \omega^2 C^2}}\right) = -\arctan\left(\frac{\omega C}{R_s(G_p^2 + \omega^2 C^2) + G_p}\right)$$

(2.28)

In order to determine the series resistance  $R_s$ , the equations 2.27 and 2.28 are then used to simultaneously fit the frequency dependent measurements of |Z| and  $\phi$  performed in strong accumulation with one parameter set, where  $G_p$ , C and  $R_s$  are fitting parameters. This fitting process and the subsequent correction of the C(V) and  $G_p(V)$  measurements was done using a Maple software developed at the Institut für Materialien und Bauelemente der Elektronik of the Leibniz Universität Hannover [78]. Starting values for the fit are extracted from the measurement of C(V) and  $G_p(V)$  based on the two-element parallel model. In particular, a starting value for the series resistance is determined from

$$R_s = \frac{G_{m,acc}}{G_{m,acc}^2 + \omega^2 C_{m,acc}^2},$$

(2.29)

where  $C_{m,acc}$  and  $G_{m,acc}$  are the measured values of C and G in accumulation based on the two-element parallel model. This expression is determined by comparing the impedance of the two-element series model (Fig. 2.14c)) with the impedance of the two-element parallel model (Fig. 2.14b)) under the assumption that the capacitances in both models are identical [79]. Therefore, it is not very accurate and may have to be adjusted if the fit does not converge.

Correction for series resistance: Analogous to the determination of equation 2.25, the impedance of the two-element model with a conductance and a capacitance connected in parallel as shown in Fig. 2.14b) is given by

$$Z' = \frac{G_m - i\omega C_m}{G_m^2 + \omega^2 C_m^2},\tag{2.30}$$

with  $C_m = C'$  and  $G_m = G'_p$ . The m emphasizes that these are the measured values of the capacitance and the conductance (see also section 3.3.3). Equating the real parts as well as the imaginary parts of the equations 2.25 and 2.30 and solving the resulting system of linear equations, gives the following expressions for the capacitance  $C_{corr} = C$  and the conductance  $G_{p,corr} = G_p$  in the three-element model [79]

$$C_{corr} = \frac{(G_m^2 + \omega^2 C_m^2) C_m}{a^2 + \omega^2 C_m^2}$$

(2.31)

$$G_{p,corr} = \frac{(G_m^2 + \omega^2 C_m^2)a}{a^2 + \omega^2 C_m^2}$$

(2.32)

with

$$a = G_m - (G_m^2 + \omega^2 C_m^2) R_s. (2.33)$$

These equations are then used to correct the measured values  $C_m$  and  $G_m$  for the series resistance.

## 2.5.3. Determination of the flat band voltage from the CV-curve

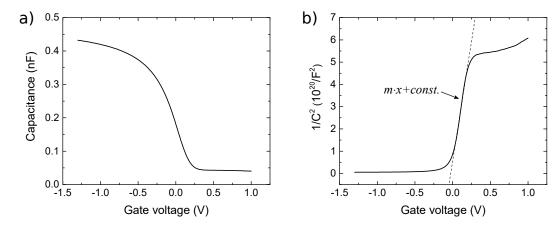

There are many methods to determine the flat band voltage from a measured CV-curve [80, 81, 82, 83]. In this work two methods are used, the flat band capacitance method and the inflection point method.

Flat band capacitance method: In this method the flat band capacitance is first determined and with it the flat band voltage is read from the CV-curve (after correction for series resistance). The flat band capacitance  $C_{fb}$  is given by the series connection of the oxide capacitance  $C_{ox}$  and the semiconductor capacitance at the flat band voltage

Figure 2.15.: Determination of the semiconductor capacitance at the flat band condition: (a) CV-curve after correction for series resistance and (b) the corresponding  $1/C^2$ -characteristic. The semiconductor capacitance at the flat band condition can be determined from the slope m of the linear part of the  $1/C^2$ -curve (dashed line).

$C_{s,fb}$  (see also section 2.5.1):

$$C_{fb} = \frac{C_{ox}C_{s,fb}}{C_{ox} + C_{s,fb}}. (2.34)$$

The oxide capacitance  $C_{ox}$  is determined from the CV-curve in strong accumulation. The semiconductor capacitance at the flat band voltage  $C_{s,fb}$  is given by [81]

$$C_{s,fb} = \varepsilon_0 \varepsilon_s \frac{A}{L_D},\tag{2.35}$$

where  $\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_s$  is the dielectric constant of the semiconductor, A is the active area of the capacitor and  $L_D$  is the Debey length, which is given by [81]

$$L_D = \sqrt{\frac{k_B T \varepsilon_0 \varepsilon_s}{e^2 N_D}},\tag{2.36}$$

where  $k_B$  is the Boltzmann constant, T is the temperature, e is the elementary charge and  $N_D$  is the doping concentration, which can be calculated via [81]

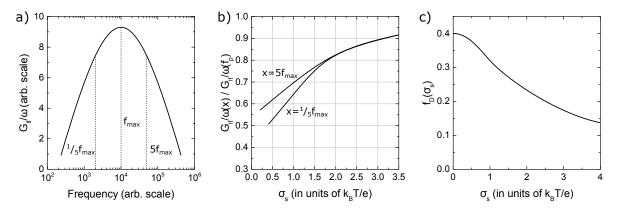

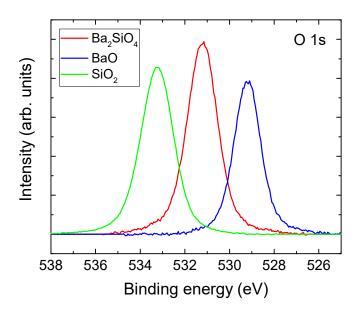

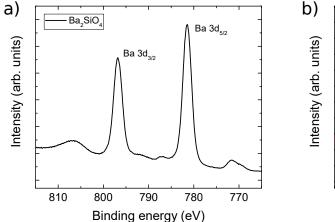

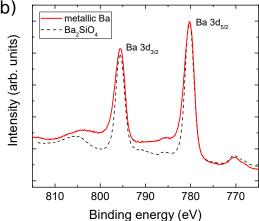

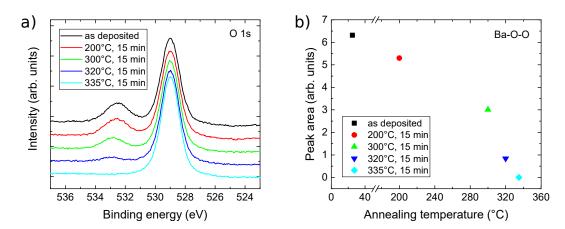

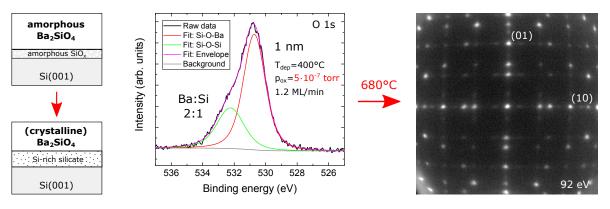

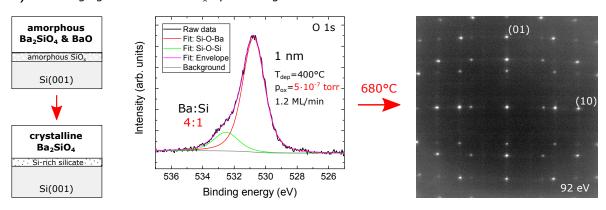

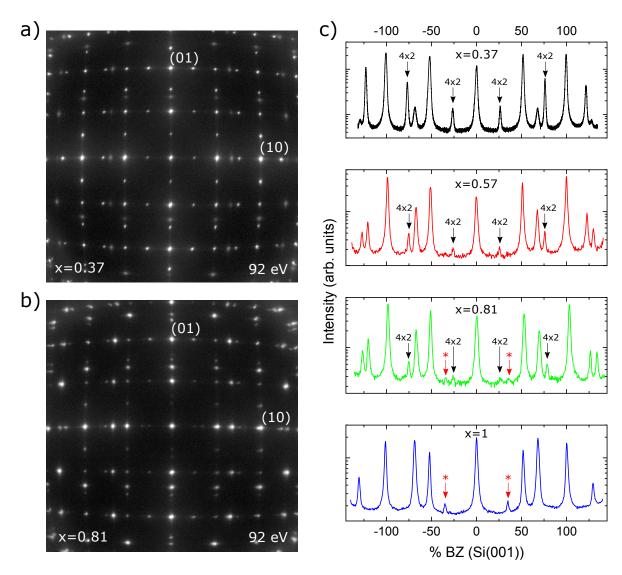

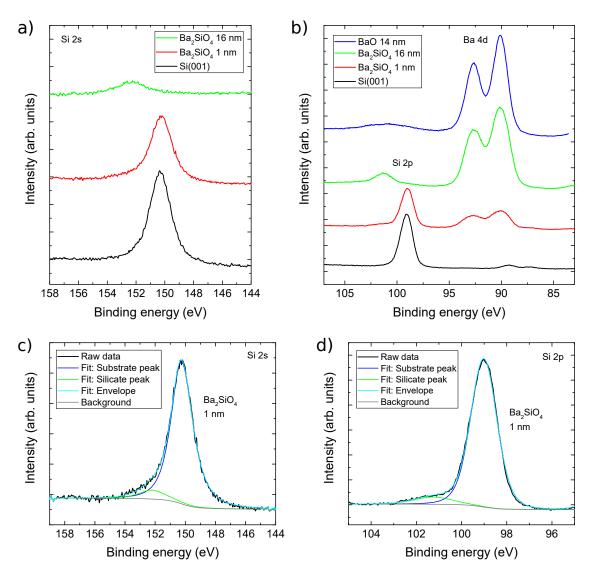

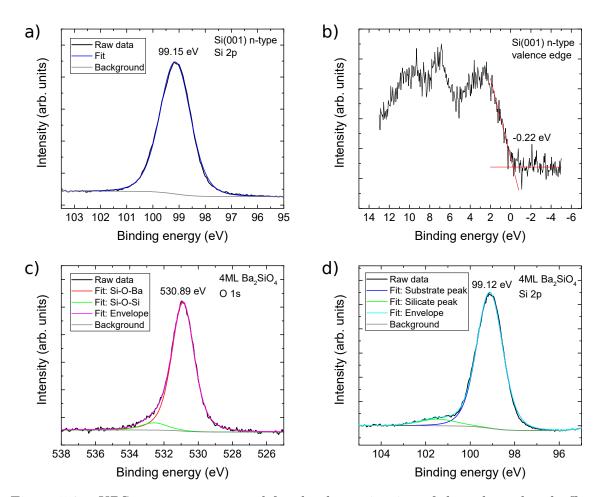

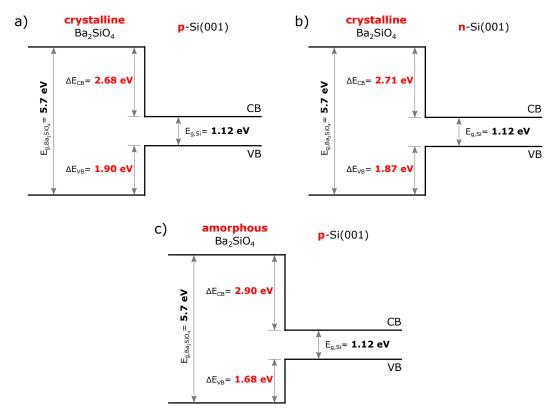

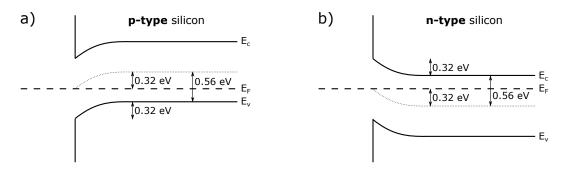

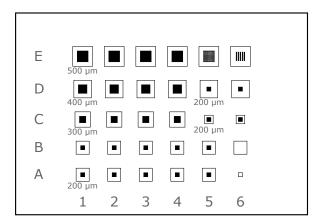

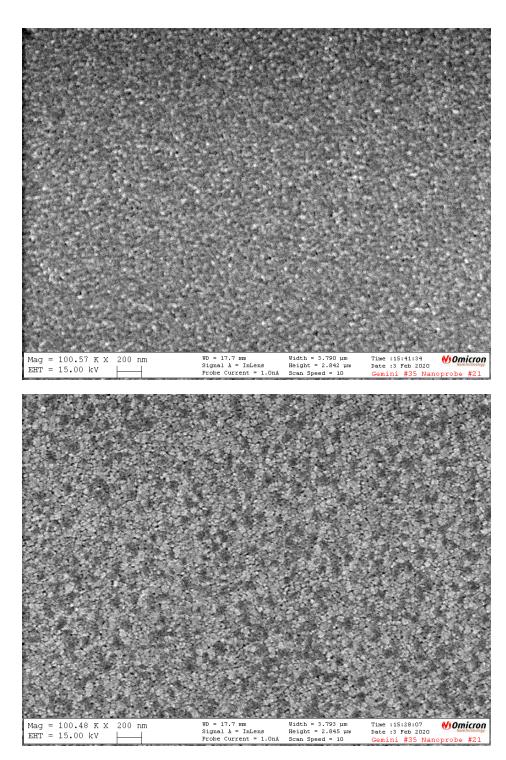

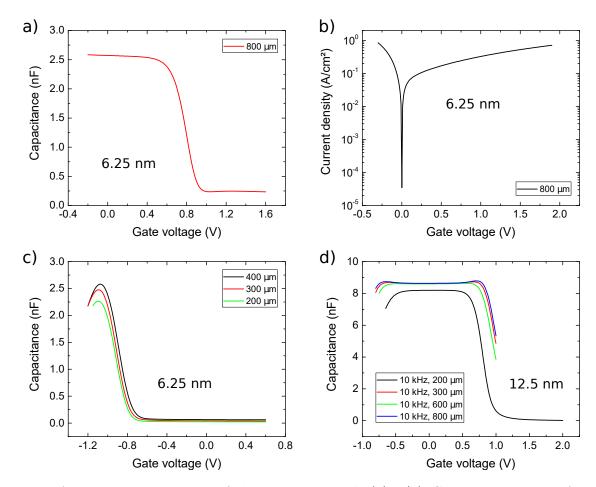

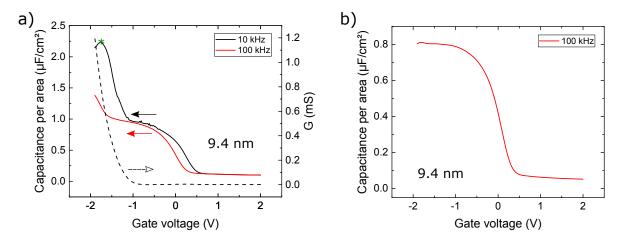

$$N_D = \frac{2}{e \,\varepsilon_0 \varepsilon_s} \cdot (|m| \cdot A^2)^{-1}, \tag{2.37}$$