## **KAVUAKA**

## Chip Design für digitale Hörhilfen

Am Institut für Mikroelektronische Systeme (IMS)

wird im Rahmen des Exzellenzclusters Hearing4all erforscht,

wie Signalverarbeitung-Chips

für digitale Hörgerätesystemen

anhand von komplexen Hörgerätealgorithmen konzipiert

und optimiert werden können.

Ziel der Forschung ist es, neuartige Prozessorarchitekturen zu entwickeln, die die geforderte hohe Rechenleistung bereitstellen, gleichzeitig einen sehr geringen Stromverbrauch aufweisen und in kleine Hörgerätegehäuse integriert werden können.

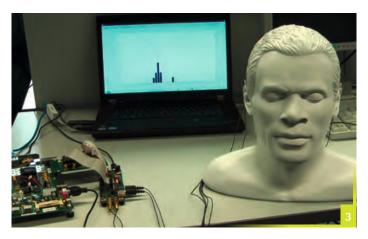

Abbildung 1

Darstellung der verschiedenen

Phasen der Chipentwicklung:

Platzierung (1) aller Komponenten, Verdrahtung (2) und Simulation des Spannungsabfalls (3)

über dem Chip.

1

Bereits ein teilweiser Hörver-Sprachverständlichkeit insbelust führt zu einer deutlichen sondere in komplexen akusti-Einschränkung der Lebensschen Szenarien, wie zum Beiqualität in vielen alltäglichen spiel auf einer Party, verbes-Situationen. Ein solcher Hörsern. So sollen zukünftige verlust betrifft rund 17 Pro-Hörgeräte beispielweise sprechende Personen in der Umgezent der Weltbevölkerung. Die Auswirkungen und Folgen bung erkennen und die reledieses Hörverlustes können vanten Sprecher aus den Störgeräuschen herausfiltern (vgl. durch moderne Hörhilfen vermindert werden, indem die Artikel Sprecherlokalisation in Sprachverständlichkeit durch Hörgeräten). digitale Signalverarbeitung verbessert wird. Jedoch ist

eine aufwändige digitale Sig-

der geringen Größe von Hör-

nalverarbeitung auf Grund

hilfen und auf Grund des

Batteriebetriebs nur eingeschränkt möglich. Durch neue

Erkenntnisse aus der For-

schung und kontinuierliche

technologische Entwicklun-

gen werden die Signalprozes-

soren digitaler Hörgerätesys-

teme immer leistungsfähiger,

kleiner und energieeffizienter.

Dadurch wird der Einsatz

neuartiger und recheninten-

gorithmen möglich, die die

siver Signalverarbeitungs-Al-

Der am Institut für Mikroelektronische Systeme (IMS) entwickelte Hörgeräte-Prozessor mit dem Namen KAVUAKA ist für diese Art von rechenintensiver Signalverarbeitungs-Algorithmen ausgelegt. KAVUAKA ist ein sogenannter applikationsspezifischer Instruktionssatz-Prozessor (ASIP). Die generische Basisprozessorarchitektur wurde anhand der im Exzellenzcluster *Hearing4All* entwickelten Hörgerätealgorithmen angepasst und optimiert. Die Anpassung erfolgte durch das Einfügen komplexer ange-

passter Instruktionen in den Basisinstruktionssatz. Nennenswerte Erweiterungen sind eine Multiplikations-Additions-Einheit, die sowohl mit reellen als auch mit komplexen Zahlen rechnen kann, Architekturen für Verlustleistungsoptimierungen bei Speicherzugriffen und ein Audio-Interface für eine geringe Audio-Latenz. Während der Entwicklungsphase von KAVUAKA sind viele Entwurfsraumuntersuchungen mit Hilfe von Simulationen durchgeführt worden, um anhand der verschiedenen Algorithmen die Rechenleistung und die Verlustleistungsaufnahme des Prozessors zu optimieren [1]. Es konnte für diese verschiedene Hörgerätealgorithmen gezeigt werden, dass KAVUAKA mit den optimierten Erweiterungen schneller und effizienter als vergleichbare und aktuelle Hörgeräte-Prozessoren rechnen kann. In der letzten Phase des Exzellenzclusters wurde der

*KAVUAKA* Prozessor als Chip gefertigt [2].

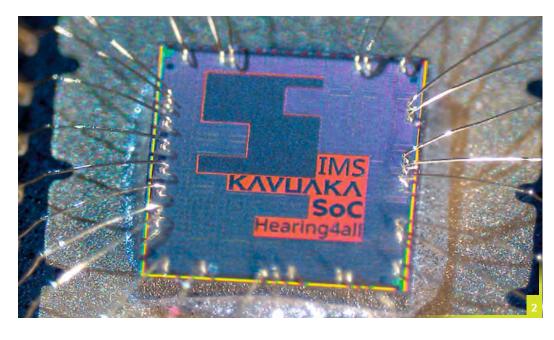

Die Phasen der Chipentwicklung sind in Abbildung 1 dargestellt. Eine Mikroskop-Aufnahme des hergestellten Chips ist in Abbildung 2 gezeigt. Die verwendete Chip-Technologie ist für eine extrem niedrige Verlustleistung ausgelegt und hat eine Strukturgröße von 40 nm. Der Chiphat eine Fläche von ungefähr

nen, die sich in ihrer Rechenleistung und Verlustleistung unterscheiden.

Um Fehler im Chip-Design während der Entwicklung zu vermeiden, wird der Hörgeräteprozessor unter realen Bedingungen mit Algorithmen, die im Exzellenzcluster *Hearing4all* entwickelt werden, getestet. Dazu wird der Prozessor mit Dummy-Hörgeräten verbunden und es werden

wickelten Hörgeräte-Entwicklungsplattform gekoppelt, um sämtliche Funktionalität testen zu können. Die Entwicklungsplattform bietet eine Bluetooth-Schnittstelle zur drahtlosen Kommunikation zwischen dem Hörgerät und einem Smartphone oder Tablet. Auf diese Weise können die Hörgerätealgorithmen gesteuert werden. Um den aktuellen Stromverbrauch des Prozessors im laufenden Be-

Abbildung 2

Der KAVUAKA Chip für digitale Hörgeräte. Der Chip hat eine Kantenlänge von 1,9 mm und ist über die Bond-Drähte mit anderen Hörgerätekomponenten verbunden.

3.6 mm<sup>2</sup> bei einer Kantenlänge von 1.9 mm. Die Leistungsaufnahme beträgt wenige tausendstel Watt.

Da ein Hörgeräteprozessor durch eine unterschiedliche Priorisierung der Optimierungsziele in Form von Rechenleistung, Verlustleistung und Chipfläche unterschiedlich optimiert werden kann, ist KAVUAKA als ein sogenanntes System-on-Chip (SoC) entworfen worden. Dieses System enthält vier Hörgeräteprozessoren und zehn Co-Prozessoren, die einzeln oder gleichzeitig aktiviert, deaktiviert und unterschiedlich miteinander gekoppelt werden können. Dies ermöglicht die Erforschung von verschiedenen Hörgerätekonfiguratio-

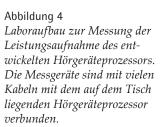

typische Hörsituationen nachgestellt. Dies ist in *Abbildung 3* gezeigt. Der gesamte Prozessor wird in diesem Fall mit Hilfe eines Rapid Prototyping Systems emuliert und mit einer eigenständig dafür ent-

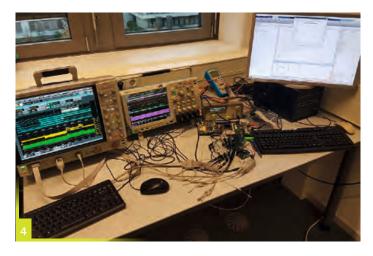

trieb zu ermitteln, wird der Prozessor im Labor mit sehr genauen Strom- und Spannungsmessgeräten und Oszilloskopen verbunden. *Abbildung 4* zeigt den Messaufbaus unter Laborbedingungen.

Abbildung 3

Rapid Prototyping Test System

für den KAVUAKA Prozessor.

Der im Exzellenzcluster Hearing4all entwickelte Lokalisierungsalgorithmus wird unter realen

Bedingungen getestet. Der Monitor zeigt die Richtung der einfallenden Schallquellen an.

Fotos: Institut für Mikroelektronische Systeme (IMS)

Mit diesem Aufbau werden die verschiedenen Hörgerätekonfigurationen hinsichtlich des Stromverbrauchs unter verschiedenen Bedingungen untersucht. In der Fortsetzung des Exzellenzclusters *Hearing4all 2.0* werden auf Basis der Erkenntnisse und der Ergebnisse neue Architekturen für zukünftige Hörgeräte entwickelt. Ein Ziel ist die Erweiterung des

KAVUAKA Prozessors um einen Hardwarebeschleuniger. Dieser soll die Berechnung von aktuellen Algorithmen des maschinellen Lernens, insbesondere tiefe neuronale Netze (DNNs), beschleunigen.

## Literatur

- [1] Gerlach, L.; Marquardt, D.; Payá Vayá, G.; Liu, S.; Weißbrich, M.; Doclo, S.; Blume, H. (2017): Analyzing the Trade-Off between Power Consumption and Beamforming Algorithm Performance using a Hearing Aid ASIP, Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS)

- [2] Gerlach, L.; Payá-Vayá, G.; Blume, H. (2019): KAVUAKA: A Low Power Application Specific Hearing Aid Processor, 27th IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC 2019)

**Prof. Dr.-Ing. Holger Blume**Jahrgang 1967, ist seit 2008

Professor für "Architekturen und Systeme" und als geschäftsführender Leiter des Instituts für Mikroelektronische Systeme (IMS) tätig. Seine wesentlichen Forschungsinteressen liegen auf dem Gebiet der Algorithmen und heterogenen Architekturen zur digitalen Signalverarbeitung, der Entwurfsraum-Exploration für diese Architekturen sowie den dazu erforderlichen Modellierungstechniken. Kontakt: blume@ims.uni-hannover.de

apl. Prof. Dr.-Ing. Guillermo Payá Vayá

Jahrgang 1978, ist derzeit au-Berplanmäßiger Professor am Institut für Mikroelektronische Systeme (IMS). Seine Forschungsinteressen umfassen eingebettete Computer und das Architekturdesign von Signalund Bildverarbeitungssystemen. Kontakt: guipava@ims.uni-hannover.de

Dipl.-Ing. Lukas Gerlach

Jahrgang 1988, ist derzeit wissenschaftlicher Mitarbeiter am Institut für Mikroelektronische Systeme (IMS). Seine Forschungsschwerpunkte liegen im Bereich der Entwicklung von verlustleistungsarmen und applikationsspezifischen Architekturen für digitale Hörgeräte. Kontakt: gerlach@ims.uni-hannover.de