# Time Domain Based Image Generation for Synthetic Aperture Radar on Field Programmable Gate Arrays

Von der Fakultät für Elektrotechnik und Informatik der Gottfried Wilhelm Leibniz Universität Hannover zur Erlangung des akademischen Grades

Doktor-Ingenieur

(abgekürzt: Dr.-Ing.)

genehmigte Dissertation

von Herrn Fabian Cholewa M.Sc.

geboren am 25. Februar 1981 in Winsen an der Luhe / Deutschland

Referent: Univ.-Prof. Dr.-Ing. Holger Blume

Referent: Univ.-Prof. Dr.-Ing. Jörn Ostermann

Tag der Promotion: 20.06.2018

#### **Danksagung**

Die vorliegende Dissertation ist im Rahmen meiner Tätigkeit als wissenschaftlicher Mitarbeiter am Institut für Mikroelektronische Systeme (IMS) der Gottfried Wilhelm Leibniz Universität entstanden.

An erster Stelle möchte ich mich bei Herrn Prof. Dr.-Ing Holger Blume für die langjähre fachliche Unterstützung und die Übernahme des 1. Referats bedanken. Herr Blume hat in seiner Funktion als Leiter des Instituts außerdem einen wesentlichen Einfluss auf die positiven Ergebnisse dieser Arbeit. Des Weiteren möchte ich mich bei Herrn Prof. Dr.-Ing Jörn Ostermann für die Übernahme des Koreferats und die freundliche Zusammenarbeit im Bereich SAR bedanken. Mein weiterer Dank richtet sich an Herrn Prof. Dr.-Ing Peter Pirsch, für die jahrelange fachliche Unterstützung im Bereich SAR, sowie für die Übernahme des Prüfungsvorsitzes.

Ich möchte mich außerdem bei meinen Kollegen für die gute Atmosphäre am Institut, sowie für die diversen fachlich hilfreichen Diskussionen bedanken. Für die erfolgreiche Zusammenarbeit im Projekt, die Unterstützung und den Teamgeist möchte ich mich besonders bei Matthis Wielage, Christian Fahnemann und Martin Pfitzner bedanken.

Meinen Freunden danke ich für die Motivation und das Gefühl mit den täglichen Sorgen nicht alleine zu sein. Der größte Dank gilt meiner Familie, die mir immer das Gefühl der vollen Unterstützung geben und sich immer für mich eingesetzt haben. Ohne diese Unterstützung während meiner Laufbahn, wäre ich niemals bis zu diesem Punkt gekommen. Dafür möchte ich meiner Mutter Bärbel Stürzbecher, meinem Vater Erik Cholewa, meinem Stiefvater Emil Stürzbecher, meiner Schwester Melanja Tucker, sowie meinen Großeltern Christine und Rolf Meyer danken.

Ich widme diese Arbeit meinem Vater Erik Cholewa, der diesen Tag leider nicht mehr erleben durfte.

#### **Abstract**

Aerial images are important in different scenarios including surface cartography, surveillance, disaster control, height map generation, etc. Synthetic Aperture Radar (SAR) is one way to generate these images even through clouds and in the absence of daylight. For a wide and easy usage of this technology, SAR systems should be small, mounted to Unmanned Aerial Vehicles (UAVs) and process images in real-time. Since UAVs are small and lightweight, more robust (but also more complex) time-domain algorithms are required for good image quality in case of heavy turbulence. Typically the SAR data set size does not allow for ground transmission and processing, while the UAV size does not allow for huge systems and high power consumption to process the data. A small and energy-efficient signal processing system is therefore required.

To fill the gap between existing systems that are capable of either high-speed processing or low power consumption, the focus of this thesis is the analysis, design, and implementation of such a system. A survey shows that most architectures either have to high power budgets or too few processing capabilities to match real-time requirements for time-domain-based processing. Therefore, a Field Programmable Gate Array (FPGA) based system is designed, as it allows for high performance and low-power consumption. The Global Backprojection (GBP) is implemented, as it is the standard time-domain-based algorithm which allows for highest image quality at arbitrary trajectories at the complexity of  $\mathcal{O}(N^3)$ . To satisfy real-time requirements under all circumstances, the accelerated Fast Factorized Backprojection (FFBP) algorithm with a complexity of  $\mathcal{O}(N^2 log N)$  is implemented as well, to allow for a trade-off between image quality and processing time. Additionally, algorithm and design are enhanced to correct the failing assumptions for Frequency Modulated Continuous Wave (FMCW) Radio Detection And Ranging (Radar) data at high velocities. Such sensors offer high-resolution data at considerably low transmit power which is especially interesting for UAVs.

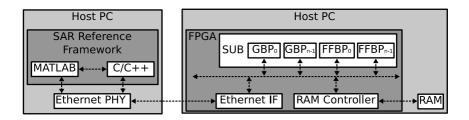

A full analysis of all algorithms is carried out, to design a highly utilized architecture for maximum throughput. The process covers the analysis of mathematical steps and approximations for hardware speedup, the analysis of code dependencies for instruction parallelism and the analysis of streaming capabilities, including memory access and caching strategies, as well as parallelization considerations and pipeline analysis. Each architecture is described in all details with its surrounding control structure. As proof of concepts, the architectures are mapped on a Virtex 6 FPGA and results on resource utilization, runtime and image quality are presented and discussed. A special framework allows to scale and port the design to other FPGAs easily and to enable for maximum resource utilization and speedup.

The result is streaming architectures that are capable of massive parallelization with a minimum in system stalls. It is shown that real-time processing on FPGAs with strict power budgets in time-domain is possible with the GBP (mid-sized images) and the FFBP (any image size with a trade-off in quality), allowing for a UAV scenario.

Keywords: Synthetic Aperture Radar, SAR, Time-domain, Backprojection, FPGA

## Kurzfassung

Luftbilder sind ein wichtiger Bestandteil in der Kartographierung, der Überwachung, des Katastrophenmanagements, der Generierung von Höhenmodellen usw. Die Technologie des Radars mit synthetischer Apertur, oder Synthetic Aperture Radar (SAR), eröffnet die Möglichkeit diese Bilder auch durch Wolken und in Dunkelheit zu erzeugen. Um diese Technologie in der Breite verfügbar zu machen, ist es nötig SAR Systeme zu entwickeln, die in Drohnen (Unmanned Aerial Vehicles (UAVs)) eingesetzt werden können und in der Lage sind Bilder schritthaltend zu generieren, jedoch machen die geringe Größe und das damit einhergehende geringe Gewicht von Drohnen, diese anfälliger für atmosphärische Einflüsse. Deshalb werden bei schwereren Turbulenzen robustere (aber auch komplexere) zeitbereichsbasierte Verfahren eingesetzt, um eine ausreichende Bildqualität gewährleisten zu können. SAR Systeme liefern in der Regel hohe Datenraten die, aufgrund der geringen Geschwindigkeiten der Funkverbindung, nicht schritthaltend zu einer Bodenstation übertragen werden können, um die Daten dort schritthaltend zu verarbeiten. Aufgrund der rauschartigen Charakteristik können die Daten auch nicht komprimiert werden. Da Drohnen üblicherweise nur über ein beschränktes Platz- und Energiebudget verfügen, müssen die eingesetzten SAR Systeme innerhalb dieser Spezifikationen liegen und dennoch in der Lage sein die Daten schritthaltend zu verarbeiten.

Um die Lücke zwischen bestehenden System zu schließen, die entweder nicht zu einer schritthaltenden Verarbeitung hochratiger Sensordaten in der Lage sind oder energieeffizienten arbeiten, liegt der Fokus dieser Arbeit auf der Analyse, dem Entwurf und der Implementierung eines Systems, das beide Eigenschaften vereint. Eine Voruntersuchung ergibt, dass die meisten nicht dedizierten Architekturen diese beiden Anforderungen nicht gleichzeitig erfüllen können. Deshalb wird eine dedizierte Field Programmable Gate Array (FPGA) Architektur entwickelt, die Energieeffizienz mit hoher Rechenleistung kombiniert. Das Standardverfahren im Zeitbereich ist die globale Rückprojektion (Global Backprojection (GBP)) mit einer Komplexität von  $\mathcal{O}(N^3)$ . Dieses wird implementiert, da es beliebige Trajektorien bei maximaler Bildqualität ermöglicht. Um die schritthaltende Verarbeitung bei größeren Datensätzen zu ermöglichen, wird außerdem das beschleunigte Rückprojektionsverfahren (Fast Factorized Backprojection (FFBP)) implementiert, das bei einer Komplexität von  $\mathcal{O}(N^2 log N)$  einen Abtausch zwischen Bildqualität und Berechnungszeit ermöglicht. Außerdem wird die Architektur erweitert, um grundlegende Annahmen zu korrigieren die versagen, wenn Frequency Modulated Continuous Wave (FMCW) Radardaten verarbeitet werden, die bei hohen Geschwindigkeiten aufgenommen wurden. FMCW Sensoren sind speziell für UAVs interessant, da sie hohe Auflösungen bei vergleichsweise geringer Sendeleistung ermöglichen.

Für einen effizienten Entwurf, der vorhandene Hardware Ressourcen maximal nutzt, werden die Verfahren einer vollständigen Analyse unterzogen. Dies beinhaltet die Analyse des mathematischen Modells, sowie die Analyse möglicher Approximationsverfahren zur beschleunigten Ausführung auf dedizierten Architekturen.

Außerdem die Analyse von Instruktionsabhängigkeiten zur Maximierung der Parallelisierung, die Analyse der kontinuierlichen Datenwortverarbeitung in Bezug auf den Hauptspeicher- und Zwischenspeicherzugriff, sowie die Analyse zum Pipelining der Verfahren. Alle Architekturen werden inklusive der Kontrollstrukturen detailliert beschrieben. Zum Nachweis der Machbarkeit werden die Architekturen auf einen Virtex 6 FPGA übertragen und die benötigten Ressourcen, die Laufzeiten sowie die resultierende Bildqualität präsentiert und bewertet. Ein spezielles Framework erlaubt die einfache Portierung auf weitere FPGAs, sowie die ressourcenabhängige Skalierung, um die jeweils maximale Beschleunigung zu erreichen.

Das Resultat ist eine Architektur, die eine nahezu kontinuierliche Datenwortverarbeitung bei massiver Parallelisierung und gleichzeitig minimaler Unterbrechung der Pipeline ermöglicht. Es wird gezeigt, dass eine schritthaltende Verarbeitung bei gleichzeitiger strikter Begrenzung des Energiebudgets, im Zeitbereich mit dem GBP (bis zu mittleren Bildgrößen) sowie mit dem FFBP (für beliebige Bildgrößen bei gleichzeitigem Abtausch gegen Qualität), möglich ist. Der Einsatz auf UAVs ist damit sinnvoll möglich.

**Schlagworte:** Radar mit synthetischer Apertur, SAR, Zeitbereich, Rückprojektion, FPGA

## **Contents**

| Lis | st of t | erms a  | and abbre   | viations                                                         | ΧI   |

|-----|---------|---------|-------------|------------------------------------------------------------------|------|

| Lis | st of s | ymbol   | s           |                                                                  | XIII |

| 1   | Intro   | ductio  | on          |                                                                  | 1    |

|     | 1.1     | A brie  | f history c | of Radar and SAR                                                 | 3    |

|     | 1.2     |         | -           | resulting motivation                                             |      |

|     | 1.3     | Resear  | rch object  | ives                                                             | 9    |

|     | 1.4     |         |             | s work                                                           |      |

| 2   | SAR     | image   | processi    | ng                                                               | 11   |

|     | 2.1     | SAR s   | ignal mod   | lel                                                              | 11   |

|     | 2.2     | Azimu   | ith compre  | ession in frequency-domain                                       | 16   |

|     | 2.3     | Azimu   | ith compre  | ession in time-domain                                            | 17   |

|     |         | 2.3.1   | Global b    | ackprojection algorithm (GBP)                                    | 17   |

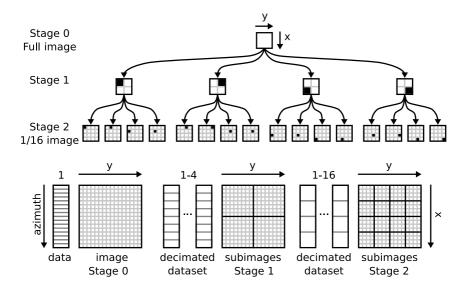

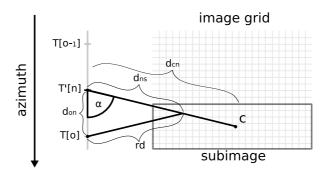

|     |         | 2.3.2   | Fast fac    | torized backprojection algorithm (FFBP)                          | 21   |

|     |         | 2.3.3   | FMCW        | ${\sf backprojection\ algorithm\ (start-stop-approximation)\ }.$ | 25   |

| 3   | Rela    | ted wo  | ork         |                                                                  | 29   |

|     | 3.1     | Non d   | edicated a  | architectures                                                    | 29   |

|     | 3.2     |         |             | tectures                                                         | 31   |

|     | 3.3     | Evalua  | ation and   | discussion                                                       | 32   |

| 4   | Cond    |         | l hardwar   |                                                                  | 33   |

|     | 4.1     | Field I | Programm    | able Gate Arrays (FPGAs)                                         | 33   |

|     | 4.2     | Princi  | ples for de | edicated hardware implementation                                 | 36   |

|     | 4.3     | Analys  | sis of the  | mathematical SAR model                                           | 39   |

|     | 4.4     | Analys  |             | essing dependencies                                              |      |

|     |         | 4.4.1   |             | pendencies                                                       |      |

|     |         | 4.4.2   | FFBP d      | ependencies                                                      | 47   |

|     |         | 4.4.3   | Conclusi    | on of dependency analysis                                        | 53   |

|     | 4.5     | Analys  |             | aming capabilities                                               |      |

|     |         | 4.5.1   | Memory      | access patterns (loop ordering)                                  | 54   |

|     |         |         | 4.5.1.1     | General considerations for RAM access                            |      |

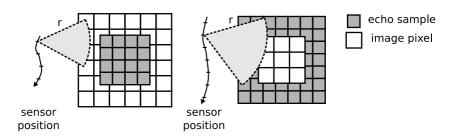

|     |         |         | 4.5.1.2     | Considerations for GBP RAM access optimization .                 | 57   |

|     |         |         | 4.5.1.3     | Considerations for GBP RAM access reduction                      | 60   |

|     |         |         | 4.5.1.4     | Considerations for FFBP RAM access optimization                  | 65   |

|     |         |         | 4.5.1.5     | Considerations for FFBP RAM access reduction                     | 68   |

| 7 | Sum        | ımary     |                                                          | 159       |

|---|------------|-----------|----------------------------------------------------------|-----------|

|   | 6.4        | ∟valua    | ation and discussion of results                          | 154       |

|   | <i>C</i> 4 | 6.3.3     | FFBP image results                                       | 153       |

|   |            | 6.3.2     | FMCW image results                                       | 152       |

|   |            | 6.3.1     | GBP image results                                        | 151       |

|   | 6.3        | _         | results                                                  | 151       |

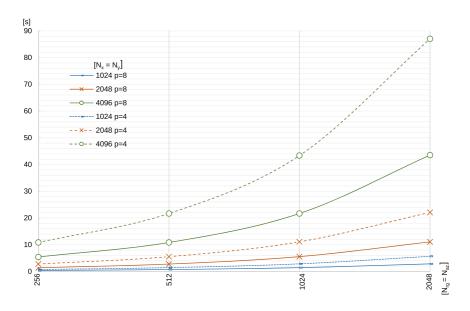

|   |            | 6.2.3     | FFBP performance results                                 | 148       |

|   |            | 6.2.2     | FMCW performance results                                 | 148       |

|   |            | 6.2.1     | GBP performance results                                  | 145       |

|   | 6.2        |           | mance results                                            | 145       |

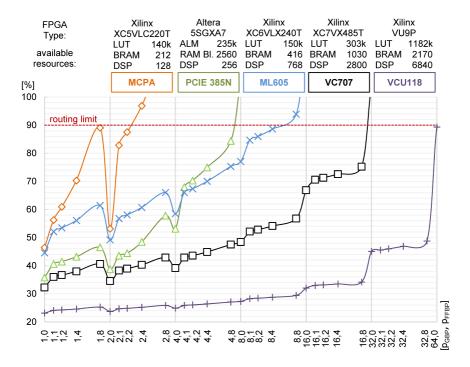

|   |            | 6.1.3     | FFBP resource utilization                                | 141       |

|   |            | 6.1.2     | FMCW resource utilization                                | 139       |

|   |            | 6.1.1     | GBP resource utilization                                 | 135       |

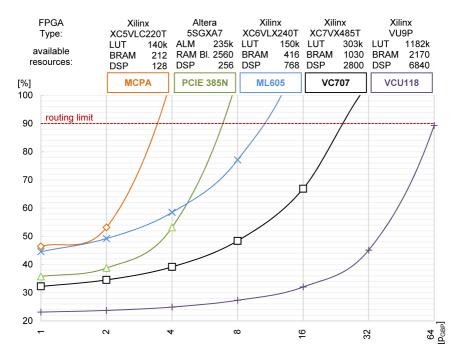

|   | 6.1        |           | rce utilization                                          | 135       |

| 6 |            |           | d evaluation                                             | 135       |

| _ |            |           |                                                          |           |

|   | 5.5        | •         | ation of dedicated modules                               | 132       |

|   |            | 5.4.4     | Full FFBP system                                         | 131       |

|   |            | 5.4.3     | Factorizer                                               | 126       |

|   |            | 5.4.2     | Mapper                                                   | 121       |

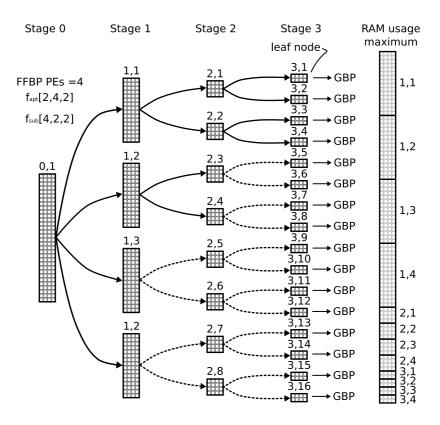

|   | 5.1        | 5.4.1     | Analysis of factorization impact on image quality        | 116       |

|   | 5.4        |           | ated FFBP implementation                                 | 114       |

|   | 5.3        | -         | ated FMCW implementation                                 | 112       |

|   |            | 5.2.2     | GBP control structure                                    | 111       |

|   | J          | 5.2.1     | GBP PE                                                   | 107       |

|   | 5.2        | -         | ated GBP implementation                                  | 106       |

|   |            | 5.1.4     | Complex multiplication                                   | 104       |

|   |            |           | 5.1.3.2 Implementation of interpolation                  | 101       |

|   |            | 5.1.5     | 5.1.3.1 Evaluation of interpolation methods              | 97        |

|   |            | 5.1.3     | Interpolation                                            | 97        |

|   |            | 5.1.2     | Square root and trigonometric functions (CORDIC)         | 90        |

|   | 5.1        | 5.1.1     | Range distance approximation                             | 90        |

| 3 | 5.1        |           | mplementation dedicated signal processing function units | <b>89</b> |

| 5 | الامد      | duuara ii | mulamentation                                            | 89        |

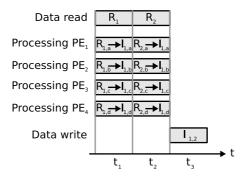

|   |            |           | 4.5.3.2 FFBP intra loop streaming                        | 85        |

|   |            |           | 4.5.3.1 GBP intra loop streaming                         | 83        |

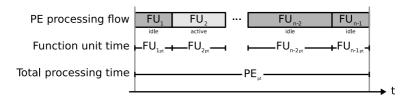

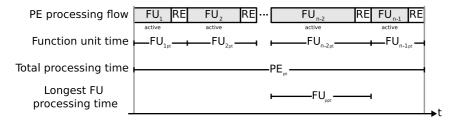

|   |            | 4.5.3     | Intra loop streaming (pipelining)                        | 80        |

|   |            |           | 4.5.2.3 Inter loop streaming on module level             | 78        |

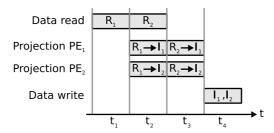

|   |            |           | 4.5.2.2 FFBP inter loop streaming                        | 75        |

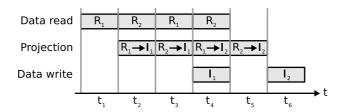

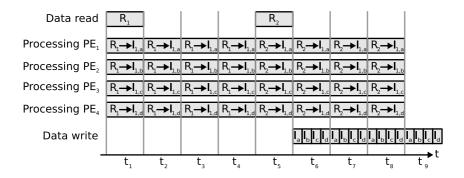

|   |            |           | 4.5.2.1 GBP inter loop streaming                         | 70        |

|   |            | 4.5.2     | Inter loop streaming (read write balancing)              | 69        |

#### List of terms and abbreviations

ALU Arithmetic Logic Unit

ARU Arithmetic Unit

ASIC Application Specific Integrated Circuit

BRAM Block Random Access Memory

CAT Computer Aided Tomography CBP Convolution Backprojection

CE Cordic Element

CLB Configurable Logic Block

CORDIC Coordinate Rotation Digital Computer

COTS Commercial Of The Shelf

CUDA Compute Unified Device Architecture

DDR Double Data Rate

DSP Digital Signal Processor

FBP Filtered Backprojection

FFBP Fast Factorized Backprojection

FFT Fast Fourier Transform

FIFO First In – First Out

FIR Finite Impulse Response

FMCW Frequency Modulated Continuous Wave

FPGA Field Programmable Gate Array

FSM Finite State Machine

FU Function Unit

GBP Global Backprojection GPP General Purpose Processor GPU Graphic Processing Unit

HDL Hardware Description Language

ISLR Integrated Sidelobe Ratio

LFM Linear Frequency Modulated

LUT Look Up Table

MAC Multiply-Accumulate MSE Mean Squared Error

NoC Network on Chip

PE Processing Element

PLD Programmable Logic Device

PPP Pulse to Pixel Projection

PSLR Peak Sidelobe Ratio

PSNR Peak Signal to Noise Ratio

Radar Radio Detection And Ranging RAM Random Access Memory RAR Real Aperture Radar RDA Range Doppler Algorithm

RISC Reduced Instruction Set Computer

RMS Root Mean Square ROM Read Only Memory

SAR Synthetic Aperture Radar

SDRAM Synchronous Dynamic Random Access Memory

SIMD Single Instruction Multiple Data

SoC System on Chip

Sonar Sound Navigation And Ranging SRAM Static Random Access Memory

TDC Time Domain Convolution TDP Thermal Design Power

UAV Unmanned Aerial Vehicle

UEMU Unified EMUlation Framework

UWB Ultra WideBand

WKA Wavenumber Domain Algorithm

# List of symbols

| Notation      | Description                                | Dimension |

|---------------|--------------------------------------------|-----------|

| $\Theta_{az}$ | aperture angle in azimuth direction        | 0         |

| $\Theta_{rg}$ | aperture angle in range direction          | 0         |

| $l_a$         | antenna lenght                             | m         |

| $t_7$         | aperture position vector z component       | m         |

| $t_{\rm v}$   | aperture position vector y component       | m         |

| $t_X$         | aperture position vector x component       | m         |

| $N_{az}$      | apertures in azimuth                       | pure      |

| $r_a$         | azimuth resolution                         | m         |

| $b_w$         | beam width                                 | m         |

| $b_l$         | burst length of memory transfer            | pure      |

| $B_{cf}$      | bus clock frequency                        | Hz        |

| $calc_{GBP}$  | calculated runtime of the GBP              | S         |

| $IY_{subC}$   | center position of subimage on ground in y | m         |

| $IX_{subC}$   | center position of subimage on ground in x | m         |

| $I_{subC}$    | center position of subimage on ground      | m         |

| $\delta y$    | distance between pixel in y axis           | m         |

| $\delta x$    | distance between pixel in x axis           | m         |

| $r_{range}$   | covered distance in range line             | m         |

| $i_{rg}$      | discrete sample position in range          | pure      |

| $i_{az}$      | discrete aperture position in azimuth      | pure      |

| $i_y$         | discrete y coordinate for pixel            | pure      |

| $i_{\chi}$    | discrete x coordinate for pixel            | pure      |

| $r_z$         | distance in z between pixel and antenna    | m         |

| $r_y$         | distance in y between pixel and antenna    | m         |

| $r_{\chi}$    | distance in x between pixel and antenna    | m         |

| $r_{max}$     | distance antenna to end of samples         | m         |

| rd            | distance between sample and aperture       | m         |

| $r_{min}$     | distance antenna to first sample           | m         |

| $\delta rg$   | distance between range samples             | m         |

| $\delta r$    | distance between pixel and antenna         | m         |

| $	au_p$       | duration of pulse                          | S         |

| $IY_{subR}$   | half width of subimage on ground in y      | m         |

| Notation      | Description                                   | Dimension |

|---------------|-----------------------------------------------|-----------|

| Z             | height map array for ground area              | m         |

| z             | height of coordinate in z axis                | m         |

|               |                                               |           |

| IP            | image pixel position array on ground          | m         |

| I             | image plane array                             | pure      |

| У             | image pixel in y direction                    | pure      |

| X             | image pixel in x direction                    | pure      |

| $r_{cell}$    | index for range cell                          | pure      |

| $i_r$         | index of sample in range line                 | pure      |

| $S_{comp}$    | interpolated phase corrected aperture         | pure      |

| $S_{int}$     | interpolated aperture                         | pure      |

| $hw_{GBP}$    | measured runtime of the GBP in hardware       | S         |

| T'            | new aperture position array                   | m         |

| $p_{fint}$    | number of parallel interpolations FUs         | р         |

| $p_{fact}$    | number of parallel factorizer PEs             | pure      |

| $f_{sub}$     | number of subimages in total                  | pure      |

| $N_{y}$       | number of pixel in y                          | pure      |

| $N_x$         | number of pixel in x                          | pure      |

| $f_{sub_{v}}$ | number of subimages in y                      | pure      |

| $f_{sub_x}$   | number of subimages in x                      | pure      |

| $f_{apt}$     | number of factorized apertures                | pure      |

| T             | original aperture position array              | m         |

| $p_{FFBP}$    | parallelization degree of the FFBP PE         | pure      |

| $p_{GBP}$     | parallelization degree of the GBP PE          | pure      |

| p             | parallelization degree of processing elements | pure      |

| $pc_c$        | phase correction constant                     | pure      |

| $\phi_{corr}$ | phase correction angle                        | 0         |

| $PE_{pcf}$    | processing element pipeline frequency         | Hz        |

| $PE_{cf}$     | processing element clock frequency            | Hz        |

| $r_{comp}$    | range compensation factor                     | complex   |

| $r_r$         | range resolution                              | m         |

| ·             | _                                             |           |

| $N_{rg}$      | samples in aperture                           | pure      |

| S'            | set of new apertures                          | pure      |

| S             | set of apertures                              | pure      |

| B             | signal bandwidth                              | Hz        |

| rg            | single range sample position                  | pure      |

| Notation                                                        | Description                                                                                                                                                                                                                                                              | Dimension                            |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| $d_s$ $c_0$ $\delta r_s$ $r_{zs}$ $r_{ys}$ $r_{xs}$ $IY_{subR}$ | slant range to ground speed of light squared distance between pixel and antenna squared distance in z between pixel and antenna squared distance in y between pixel and antenna squared distance in x between pixel and antenna startposition of subimage on ground in y | m<br>m<br>s<br>m<br>m<br>m<br>m<br>m |

| $PE_{llt} \ PE_{pt} \ 	au$                                      | time to load a full range line<br>time of processing of one PE<br>time of travel                                                                                                                                                                                         | s<br>s<br>s                          |

| $d_{nc}$ $d_{oc}$ $d_{ns}$ $d_{cn}$ $d_{on}$                    | vector between new aperture and new center vector between old aperture and new center vector between new aperture and sample vector between center and new aperture vector between old and new aperture                                                                  | m<br>m<br>m<br>m                     |

| $\lambda$ $D_{ww}$ $B_{ww}$ $IY_{subD}$ $IY_{absD}$ $IX_{absD}$ | wavelength of the radar width of data word width of memory bus word width of subimage on ground in y width of image on ground in y width of image on ground in x                                                                                                         | m<br>bit<br>bit<br>m<br>m            |

#### 1 Introduction

The principle of visual perception is a powerful and important mechanism of sensing. Many daily routines, whether complex or simple, rely strongly on this principle. The power lies within the capability of the eyes, to constantly assimilate a vast amount of surrounding information, coupled with the brain that processes and interprets this data within a very short time. Thus, many technical systems forward information only or mainly in a visual manner. The principle of Radio Detection And Ranging (Radar) constitutes no exception to that. Radar sensors send electromagnetic waves to illuminate the surrounding area, the reflected echoes carry wavelength characteristic information back to the sensor. This information is visualized and can be interpreted with a certain knowledge of the system. The most common use case for Radar technology is the range detection of objects and determination of their velocity and direction. This is used for the coordination of maritime and air traffic. The big advantage of this technology becomes obvious in four features:

- 1. The range of the human eye is extended

- 2. As an active system radar is independent of daylight

- 3. Information that is not visible for the human eye becomes accessible

- 4. Specific electromagnetic waves can penetrate certain materials and atmospheres

Besides the very basic and spread application of maritime and air traffic control, the principle of Radar can be enhanced in many different ways to gather and represent supplementary information. One of these enhanced principles is the imaging technique Synthetic Aperture Radar (SAR). Radar systems usually present information in a greatly reduced complexity, objects are reduced to a dot or their Radar cross-section. Since the process of gathering SAR information is different from Radar, certain information is lost, while other information is gained. In contrast to Radar, SAR systems are capable of presenting information in a way, that is more likely to be interpreted directly by the human eye. When mounted on an airborne platform, the gathered data can be processed to become comparable to electro-optical ground images. Depending on the used SAR principle, this technology is useful in many scenarios such as:

- 1. Topographic mapping of planetary surfaces or ocean floors [1, 2]

- 2. Monitoring the development and condition of crops [3]

- 3. Disaster control (e.g. landslide identification [4])

- 4. Military or civil surveillance [5]

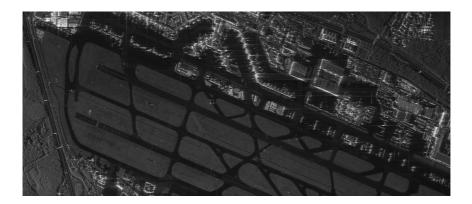

Figure 1.1: SAR image of Frankfurt airport provided by Intermap Technologies [6]

An example for SAR generated images is given in Fig. 1.1 provided by Intermap Technologies Canada. The image is part of a mapping campaign surrounding Frankfurt airport (Germany).

On a first glimpse, this image resembles a standard planar representation of a top-down grayscale aerial photo. But a detailed examination of Fig. 1.1 reveals fundamental differences to electro-optical top-down images. Some structures are emphasized while others are blurred, buildings seem to be observed from an angle and not top-down, and although streets and runways are present, no cars or planes seem to be present in the image. The differences to electro-optical images result from the SAR principle and how data is recorded and processed.

First, electromagnetic microwaves can be reflected almost completely, pass through or be absorbed depending on the material. This can be an advantage, as it creates the mentioned highlighting or fading of structures. Second, the area was scanned in  $8.8\ km$  height with a slant range of  $9.2\ km$ . This results in an angle of roughly  $45^\circ$ , creating a slightly tilted representation of higher objects. Still, it would not be perceived as a  $45^\circ$  angle. With SAR, even sharper angles are possible whereas the perception is not affected to the same extent. This allows for extreme slant range scans. In contrast to optical systems, the achievable spatial resolution of a SAR system does not change with the slant range, making it a perfect candidate for satellite missions. Third, SAR images base on data recorded over time, while an optical image is recorded in an instant. This results in smearing and dislocation of moving objects in a SAR image (e.g. white artifacts in the runway area). This effect is a disadvantage if objects need to be identified, which is important in surveillance but not in mapping means. In some cases, this can become an advantage, as objects can be indicated as being in regular motion or static.

Ground imaging is the classic SAR scenario, but many adaptations exist which allow for the retrieval of different scientific data, making SAR an important tool for different applications. Still, this technology comes with certain disadvantages which exist in recording and fast and accurate processing of SAR data. The presented thesis tackles especially the problems of faster and more accurate processing especially in harsh environments.

#### 1.1 A brief history of Radar and SAR

The first Radar system was developed in the year 1904. The German engineer Christian Hülsmeyer developed a device called Telemobilskop, which allowed to detect ships in a distance of up to 3000 m with the help of electromagnetic waves [7]. In 1922 the Italian physicist Guglielmo Marconi developed a device to detect metallic objects [8]. This principle was adopted in the same year by two American engineers, A.h.Taylor and L.C. Young, who build the first Continuous Wave (CW) Radar [9]. The second world war boosted the research and development of different radar technologies significantly, resulting in increasingly powerful constructions. In 1939 a Radardevice was used onboard an airborne platform for the first time [9]. This fast development shows that Radar was applicable in the early stages with available technologies.

Compared to Radar, SAR demands for more complex calculations. The theory of wavefront reconstruction was developed by the Hungarian engineer and Nobel Prize winner Dennis Gabor in 1948 [10]. In the year of 1951, the American mathematician Carl A. Wiley recognized, that this theory can be combined with the airborne Radar technology to generate images of an observed ground area. The principle of SAR was born, but the technology to perform the actual math for such complex signal processing was not available at that time [11]. Nevertheless, the first simple analog experimental SAR system was operating in 1952 at the University of Illinois [12]. The first SAR images of the coast of Key West (Florida) were created in 1953 [13] with this system. The patent was registered only later by Wiley in 1954 [14] and published in 1965.

More precise SAR focusing systems were developed in the optical field by the American engineers Loius J. Cutrona, Weston E. Vivian and Emmett N. Leith [15]. They started the development of optical (analog) SAR processors using the principle of Fresnel approximation. This was the standard way to generate SAR images until the development of digital SAR signal processors. The first concepts and simulations for digital SAR processing were conducted during the 1970s by the American engineers William M. Brown [16], John C. Kirk [17], W.J. van de Lindt [18] and C. Wu [19]. With the introduction of digital processing in SAR focussing, many new problems raised about how to record and process the digital data [20]. An operating digital SAR processor was first designed for the SEASAT satellite in 1978 [21]. From this day, digital SAR focusing became relevant.

In general SAR data processing can be separated in the frequency-domain-based and time-domain-based algorithms. Since the mathematical model of wavefront reconstruction was too complex for the available processing capacities in the late seventies, a less demanding algorithm had to be developed for SEASAT. This was done by MacDonald Dettwiler (MDA) and the Jet Propulsion Lab (JPL) [20] and got to be known as Range Doppler Algorithm (RDA) [22]. Therefore, the RDA was the first frequency-domain-based operating digital SAR processor. Approximations were used to simplify the mathematical model of SAR processing, which allows for faster computation with less accuracy for some cases. Many developments in the decades after the SEASAT project increased the potential of SAR, including antennas, digital components, and algorithms. Leading to applications in many different fields besides ground imaging, like topography, terrain discrimination, forestry, urban growth, oceanography, and many others.

With exponential growing processing capacities in the following decades, other frequency-domain-based algorithms like the Wavenumber Domain Algorithm (WKA) [23] and the Chirp Scaling Algorithm (CSA) [24] were developed, which increased the quality of SAR images. The WKA was the first algorithm to fully embrace the principle of wavefront reconstruction. All of the named algorithms are still popular today. Especially the RDA is widely spread as it is fast and simple and still offers good image quality. But all frequency-domain algorithms are limited in certain aspects because approximations or assumptions are made to simplify the calculation. The most important limitations are the maximum bandwidth of the Radar and the shape and extent of deviation from a linear path.

Processing in the time-domain is free from the here mentioned limitations but also more complex. The basic principle of time-domain-based algorithms is known as backprojection and is based on the Radon transformation postulated by the Austrian mathematician Johann Radon in the year 1917 [25]. It is used to transform a plane into a set of lines (projections), where each line (projection) contains the density information of the entire plane from one defined angle. Radon himself already postulated the inversion formula that is used to construct the plane information from the lines (projections). To retrieve the line information, an object or area needs to be circled by several aligned sources and several aligned sinks, facing each other to collect the density information. This is called a parallel beam geometry.

The base of the time-domain algorithms, which are also used in SAR, emerged first from the field of astronomy with the formulation of the projection slice theorem in 1956 by the Australian physicist Ronald Bracewell [26]. Thereby, Bracewell formulated the bridge between the Radon transform and the Fourier Transform by expressing the relation between the projection data and their two dimensional Fourier transform. The theorem was revisited in the early sixties for the Computer Aided Tomography (CAT) principle by different scientists, the American physician William H. Olfendorf in 1961 [27], the American physician David E. Kuhl in 1996 [28] and the South African physicist Allan McLeod Cormack in 1963 [29], who formulated the basic adaption. But a clear image could not be retrieved with the given settings.

Cormack continued on the field and was able to improve the method, but it was up to Bracewell and Riddel in 1967 [30], who enhanced the theorem with appropriate filters to remove ambiguities. The method is know today as Filtered Backprojection (FBP), Convolution Backprojection (CBP) or Time Domain Convolution (TDC). The American mathematician Larry Shepp and the electrical engineer Benjamin F. Logan implemented this method for CAT the first time in 1974 and improved it further, creating clear images of a section of a human head. The principle was adapted in parallel by Lakshminarayanan [31] and Budinger et. al [32] in 1975, to a fan beam geometry with only one source covering the entire object.

When compared, a specific type of a SAR scenario (spotlight mode) and fan-beam CAT scenarios are sorts of similar. In both cases, an area is circled and scanned from all angles by a certain type of electromagnetic waves. Considering the similarities, it is surprising that the class of time-domain algorithms was recognized for SAR much later. Compared to frequency-domain-based algorithms, time-domain-based algorithms include more detailed geometrical information during the image forming process. This results in better image quality but also a higher degree of complexity and therefore more demanding processing capacities. The early use of time-domain-based algorithms in CAT might origin from the fact that CAT systems create smaller images, while SAR systems usually create large images. Processing capabilities were simply not given at that time. When compared in more detail, CAT and SAR scenarios are different for many reasons. CAT is a circular scenario with an exact, predefined path for the multiple transmitters and receivers which are located in opposite positions. facing each other (bistatic), and are active simultaneously. Most SAR scenarios only use one transmitter and receiver simultaneously which are placed directly next to each other (monostatic), or sender and receiver are the same antenna alternating between transmission and reception. On top of that, the path is not predefined and could be either circular or linear with no exact position information. In addition to these differences, another frequency band, which can also be much wider in bandwidth, is used for SAR. But for the mentioned reasons, time-domain-based solutions could not be applied directly to SAR.

In 1983 the American engineer David C. Munson proved, that FBP could be adapted to process SAR data of a spotlight scenario [33]. A more common case for SAR is the so-called stripmap geometry where an area is scanned while flying along a linear path. The adaption to a SAR stripmap geometry was covered later by many authors independently. The American and Swedish mathematicians John A. Fawcett [34] and Hans Hellsten et. al [35] proved, independent from each other, a valid method to invert the Radon transformation for a SAR setup in 1985 and 1987 by using Fourier Hankel transformations. Both rely on straight, instead of circular, paths which can be used for stripmap scenarios. In the approach of the Swedish mathematician Lars Erik Andersson [36] in 1988 it is described how the algorithm is adapted to handle Ultra WideBand (UWB) signals, which is a key feature for SAR data processing.

When both methods are combined, a general algorithm can be derived that can process UWB SAR data in a stripmap geometry. This algorithm is often referred to as Global Backprojection (GBP) or TDC algorithm and has become a golden reference for the processing of SAR data, as it provides the best image quality. But it has high demands in processing capacities at the same time. Because of this, it is not often used in systems that need to deliver fast image results.

To counter long processing times, faster versions of the GBP algorithm were developed over the past years. Two different classes beside the basic GBP algorithm class exist. First, the two-stage algorithms which reside in a complexity class between the GBP and frequency-domain algorithms, e.g. the Fast Backprojection algorithm (FBP) developed by Ali. F. Yegulap in 1999 [37] or the Local Backprojeciton (LBP) algorithm developed by Swedish mathematicians Olle Seger et. al in 1998 [38]. Second the multiple stage algorithms that can actually reach the same complexity of the frequency-domain algorithms, e.g. the Quadtree Backprojection algorithm (QTBP) developed by John McCorkle et. al in 1996 [39], the Links Fast Backprojection algorithm (LFBP) developed by the Swedish mathematicians Stefan Nilsson et.al in 1998 [40], the Fast Hierarchical Backprojection algorithm (FHBP) developed by the American engineer Samit Basu et. all in 2000 [41] and the Fast Factorized Backprojection algorithm (FFBP) developed by the Swedish mathematician Lars Ulander et. al in 2000 [42]. Frankly, the modified versions reduce the computations for the GBP step, by combining adjacent areas of SAR data to reduce the processing complexity. As there is no free lunch, speeding up the processing results in a decrease in image quality under certain circumstances.

Depending on the size and quality of SAR data, the demands in image quality, processing capacities and the given SAR scenario, any of the time or frequency-domain algorithm can be used. The ongoing fast development of computer technology increased the capabilities of SAR systems continuously, which created an interest in the technology in military and civil organizations, making it a key technology in remote sensing.

#### 1.2 Challenges and resulting motivation

Inverse image reconstruction from multiple separated echos is of interest in fields of application like SAR, CAT and Sound Navigation And Ranging (Sonar). Different wavelengths, modes, and antenna settings allow for a variety of information to be obtained from the observed area. SAR can be used in near field scenarios, but the most common use cases are a far-field scenario like spaceborne and airborne SAR. For airborne scenarios, Unmanned Aerial Vehicles (UAVs) gain more importance due to the high reduction of costs and risk. This allows for wider civil usage of SAR in the fields of disaster prediction and control, crop and forest monitoring, archaeology, cartography, and others.

But implementing SAR on UAVs calls for strict restrictions regarding system dimensions and energy consumption of the system processing SAR data. Furthermore small and lightweight airborne platforms react more sensitive to atmospheric conditions then bigger and heavier planes. Therefore, the imaging algorithm needs to be robust enough to compensate for the effects of motion in the platform trajectory. Nevertheless, because of the mentioned advantages, this work is focused on a UAV based SAR scenario.

Depending on the application case and the sensor, the amount of raw data can be in the range of mega samples per second (MS/s). As image reconstruction algorithms come with a high degree of complexity, this results in large processing times (growing exponentially with the amount of raw data) and high energy consumption. For air- and spaceborne platforms these aspects are critical for operation. For effective missions, the image should be available shortly after the data was sampled (real-time mission control). Storing the data on-board for ground processing is therefore not a preferred option. Two option exist to handle this (runtime/energy) challenge. The first and trivial option is a real-time transmission of the raw data to the ground, so that image reconstruction can be performed on high-performance computers. But based on the sensor scan rate, the amount of raw data per second cannot be transmitted via standard downlinks. This calls for broadband solutions or the compression of the raw data before transmission. But SAR raw data resembles a noise structure, which is why compressing results in few percentages of data reduction. Broadband downlinks are not always possible either, common limitations are the given terrain (no line of sight) or the maximum energy consumption (for transmission) of the given platform (e.g. satellites). The sophisticated and second option is on board image reconstruction. Standard image compression codecs such as H264 can then be used to reach high data reduction factors on the generated images, allowing for standard downlinks to be used for real-time transmission. This is advantageous in two aspects. First, only a fraction of the raw data is stored onboard in small processing buffers, which reduces storage hardware to a minimum. Second, real-time mission control is possible if the delays between echo reception onboard and image reception on the ground can be greatly reduced. This is possible when the delays for processing, compression and image transmission are small enough. The delays for image transmission and compression are considerably small, as highly efficient hardware solutions exist for image compression, leaving only a fraction of the original data for fast image transmission. Only the delay for processing is challenging as image generation algorithms demand high-performance computing. This automatically results in bigger systems dimensions and high energy consumption. To reduce the requirements the simplest image generation algorithm should be picked.

When only runtime complexity is considered, frequency-domain-based algorithms are the better choice for processing SAR data, as they are faster at least one order of magnitudes when compared to time-domain algorithms (backprojection). The downside of these algorithms lies within the approximations used for image generation. Approximations simplify the mathematical model in a way that only

simple trajectories (linear movements) of the platform result in good image quality. But airborne platforms underlie strong deviations, which can result in a drastically reduced image quality. These errors can be compensated to a certain degree, but a full recovery is not possible. As a rule of thumb, it can be stated, that a deviation within the amount of a quarter wavelength of the carrier frequency from a linear path in any axis, does not affect the quality of the image. For SAR systems the carrier frequencies are partitioned in wavebands from 0.2 GHz to 300 GHz, resulting in wavelengths from 1.5 m to 1 mm. Applying the quarter wavelength rule, already the upper boundary of 1.5 m would limit the allowed motion deviation to 37.5 cm. For any type of airborne platform, this limitation would be violated by the typical flight path deviations. Time-domain algorithms, on the other hand, are more complex, but do not rely on approximations wherefore any trajectory is allowed and any deviation can be compensated. This is of special interest for small airborne platforms (UAVs) as they are more affected by weather conditions. This work is addressing the question under which conditions this problem can be solved, which hardware could be used for such a demanding task, and how this might limit the achieved result.

This creates a challenging scenario: A small airborne platform with reduced space, and restrictions on weight and energy consumption, has to be capable of highperformance computing for time-domain-based SAR processing. For UAVs all aspects need to be reduced to the lowest possible values to use a maximum of resources for the actual SAR sensor system. Common General Purpose Processor (GPP) architectures are not suited for this task. The power of GPPs lies within the broad variety of tasks they can handle. Due to this, the processing performance for tasks is limited on average. While multicore or manycore architectures, containing many GPP cores could partly close this gap, constraints on system size and energy consumption prohibit this solution, as already one powerful GPP core can consume the energy of 100 W and above at peak performance. Another option are Graphic Processing Units (GPUs) which are tailored for image processing. The power of GPUs lies within the massive parallel processing but makes these platforms also very energy-demanding which can result in 200 W power dissipation and above. Additionally to the high energy demands, GPUs need a host system which increases the system size. Digital Signal Processors (DSPs) which are processors that are tailored for signal processing tasks consume less energy when compared to standard GPPss or GPUss, but the performance for massive parallel tasks is reduced.

The optimal architecture that combines all criteria are Application Specific Integrated Circuits (ASICs). For maximum performance, the circuit can be designed to only implement the signal processing operations required for the specific task. Omitting unnecessary operations automatically reduces the architecture to the lowest possible system dimensions and energy consumption. The parallelism of the implemented operations can be used to increase performance. The big downside of an ASIC is the fact, that it cannot be updated to algorithmic adaptations and that it exceeds development time and cost by far, when compared to other architectures.

A compromise solution is Field Programmable Gate Array (FPGA) technology, which allows the same level of adaption and parallelism but does not match the same small system dimensions, low energy consumption, and fast operating frequency as ASICs. However, system dimension and energy consumption will still reach lower levels when compared to other high-performance platforms. The relatively low operating frequencies of FPGAs can be compensated by the massive parallelism. Development time is however comparatively high, as it requires a full hardware description. In general, the time factor needs to be considered for system design but becomes less relevant as system constraints get harsher. In contrast to ASICs, FPGAs can be adapted to algorithmic changes, although not as fast as any other mentioned architecture. When leaving development time aside, considering all given constraints and the pros and cons of each technology, FPGA technology is the best compromise. The resulting motivation is to investigate how and within which limits, onboard processing of SAR data in the time-domain is possible with FPGA based systems.

#### 1.3 Research objectives

As a key technology for surveillance, disaster control and cartography, SAR image generation is a continuous research topic. Different approaches in time-domain were already examined on different non-dedicated architectures [43, 44, 45, 46] and dedicated architectures [47, 48, 49]. Nevertheless, it becomes apparent that a gap in the field of fast time-domain-based processing on FPGAs exits.

Therefore, as a first step, one major objective is the identification of fast timedomain-based processing algorithms suitable for FPGAs implementation. A preliminary study with a high-level software implementation is necessary prior to any implementation in hardware. The study serves as a reference for quality evaluation and to examine algorithm settings, while the objective is to identify the best trade-off between achieved quality and complexity. The second objective is a low-level accuracy analysis. In contrast to pure software implementations, dedicated designs demand a deeper understanding of the underlying hardware structure for optimal results. This starts with the number representation in fixed-point format rather than floating-point format as used in software implementations. Fixed point format demands detailed analysis to understand how the reduced number format might affect the accuracy. The third objective is an efficient implementation. FPGA designs cannot compete with other architectures in terms of operating frequency, wherefore the objective is to choose algorithms, which are either suited for massive parallelization or divisible in small steps to implement a fine-grained pipelined streaming architecture. In addition to the algorithm structure, all steps can be performed with different accuracy. It is the objective, to identify approximations that fit the needs, are efficient to implement and are easy to pipeline or used in parallel. The fourth objective is scalability and portability. As the resources of FPGAs on the market constantly increase, the designed architecture should be divided in generic modules that can be scaled in size, accuracy

#### 1 Introduction

or amount to max out the resources of a wide variety of FPGAs. For universal utilization, the architecture should only depend on common hardware periphery like Double Data Rate (DDR) memory. To map the architecture on different FPGAs, the signal processing modules should be wrapped in a module that translates between the board-specific periphery and the internal communication interface. This would allow for module internal changes without any effect on the external periphery and vice versa. The fifth objective is the proof of the entire design in the form of a fully working, closed-loop real-time laboratory setup. As every setting of SAR sensors and every parameter in backprojection algorithms can change the outcome of the image result, a laboratory demonstrator is necessary to validate the universal application of the architecture. The whole setting should include a SAR sensor, signal sampling, and signal processing in real-time. Where real-time means, data needs to be processed within the same duration of sampling time. To increase the effectiveness of real-time mission control, the latency of processing should be as small as possible.

#### 1.4 Structure of this work

This thesis is structured as follows. Chapter 2 will explain the fundamental theories of the SAR principle and signal model. Based on this, the idea behind backprojection is described and the used algorithms will be explained in more detail. To understand the relevance of the presented work, Chapter 3 will give an overview of the state of the art SAR processing with backprojection on different architectures. To understand how an efficient implementation of time-domain-based processing on dedicated architectures can be achieved. Chapter 4 will explain the fundamental ideas for fast implementation. All alternative concepts will be discussed, considering the fact, that an on-board integration of time-domain-based processing on dedicated hardware is the main goal. After this, in Chapter 5 the basic signal processing blocks for fast implementations and the backprojection architectures are explained in detail, to understand which concrete measures were adopted for implementation. In Chapter 6 the concepts will be evaluated regarding resource utilization and runtime. Image quality is evaluated on different data sets which vary in their SAR scenario setting. Also, further options for fast dedicated implementations are discussed. A summary of the whole work is given in Chapter 7.

#### 2 SAR image processing

Radio Detection And Ranging (Radar) is a key technology for a variety of different applications in many different fields. Synthetic Aperture Radar (SAR) is one of these fields, where Radar technology is used to generate digital 2D images of an observed ground area. SAR systems usually base on pulsed Radar systems in a far-field scenario which involves an airborne or space-borne platform. Due to the latest development in SAR sensor technology, apart from far-field scenarios, also near field scenarios can be covered. This is possible by the use of Frequency Modulated Continuous Wave (FMCW) Radar sensors, which offer finer resolutions but do not cover bigger distances. The basic SAR signal model and the generation of images from the raw data will be explained in the following sections. The processing steps for image generation, the acquired data and the applied algorithms will be outlined.

#### 2.1 SAR signal model

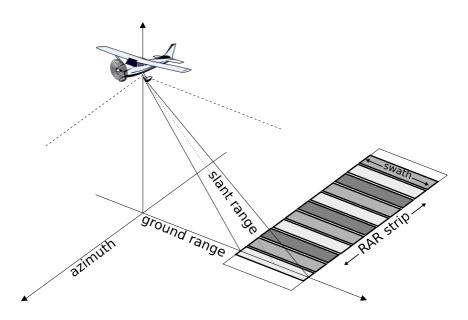

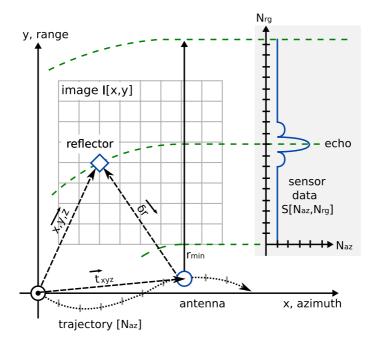

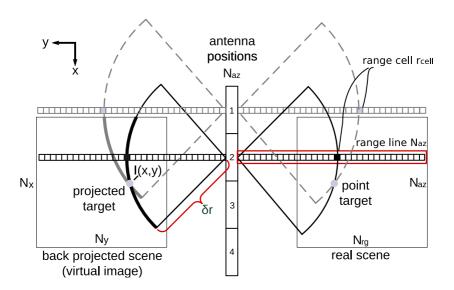

All SAR system base on the principles of Real Aperture Radar (RAR) systems [50]. Enhancements of the technology, which mostly based on signal processing, allowed to overcome the natural limitations of RAR. The limitations can be understood by looking closer into the process of how RAR systems generate images. To retrieve ground information, a RAR system sends multiple narrow beams of energy perpendicularly to the flight path (azimuth direction) of the airborne or space-borne platform to the ground. The echos are collected over time and are used to generate the ground image. The geometry is depicted in Fig. 2.1.

Based on the beam width and the distance to the ground a rather small or rather big area, called the swath, is illuminated by the beam. The distance between any point within the swath and the RAR system is called slant range. This swath has a length in range direction (perpendicular to the flight path in azimuth direction) which results from the slant range  $d_s$  and the aperture angle in range direction  $\Theta_{rg}$  of the used antenna. Within this swath, echos from further ranges return at a proportionately larger time then echos from closer ranges. Based on these time values, the echos can be separated into equidistant cells, which are combined to a range cell vector (range line  $N_{az}$ ). The relative intensity of the echos in the vector is used to generate a single image line of a narrow swath of terrain. The size of the cells defines the resolution of the image line in range direction. The resolution in azimuth direction is defined by the width of the swath, which depends on  $d_s$  and the aperture angle  $\Theta_{az}$  in the azimuth direction. Due to the continuous forward movement of the platform, the next pulse is transmitted at a slightly different position in azimuth.

Figure 2.1: Geometry for stripmap RAR on airborne platform

Therefore, a slightly different strip of terrain will be illuminated. By forming a sequential strip (RAR strip) of terrain swaths side by side in azimuth, a two-dimensional data array that forms the RAR image is created.

Due to the principle of how RAR systems work, the resolution of the image is heavily limited. To be able to distinguish between two objects in range direction, the objects must be separated by a minimum distance in slant range  $d_s$  in order to locate them in two different range cells. The distance  $d_s$  to an object is defined by the travel time  $\tau$  of the pulse to an object. Since the pulse travels to the object and back to the sensor with the speed of light  $c_0$ , the actual distance results to Eq. (2.1) [20].

$$d_s = \frac{c_0 \cdot \tau}{2} \tag{2.1}$$

This distance  $d_s$  must be greater than the radar pulse length  $\tau_p$ . Otherwise the back scattered pulse of the second object would overlap with the back scattered pulse of the first object and would locate both echos in the same range cell. Range resolution  $r_r$  is therby defined to equation Eq. (2.2) [20].

$$r_r = \frac{c_0 \cdot \tau_p}{2} \tag{2.2}$$

To focus in range direction, in order to improve the resolution in range, the length of the radar pulses  $\tau_p$  should be as short as possible. But shortening the pulse is problematic for three reasons.

First, the higher the frequency of a Radar system, the more it is affected by weather conditions like rain or clouds.

Second, the pulse must transmit enough energy, so that the backscattered echo energy is still strong enough to enable for the detection of the reflected signals. To keep the energy level constant, shortening the pulse demands for an increase of pulse energy (amplitude). This is problematic, since the design of systems that transmit very short, but high energy pulses are difficult and uneconomical.

The third reason is the direct dependency of range and azimuth resolution. To counter the range resolution problem, the first enhancement to RAR systems is introduced with the technique of range compression. Range compression is one of the two major steps in focusing Radar data and thereby an important step for moving from RAR to SAR systems. Range compression uses so-called chirped pulses (chirps) which are used in most Radar systems. Chirps are characterized by a Linear Frequency Modulated (LFM) pulses instead of short pulses with a constant frequency. Another type of pulses are so-called FMCW pulses which are covered later. Chirps can be much longer than a not modulated pulse and thus allows the pulse energy to be transmitted with lower peak power. When the echoed chirp is filtered with a matched filter, a narrow pulse is the result which contains condensed pulse energy. This improves range resolution and signal to noise ratio. The matched filtering can be implemented in many ways. One efficient method is the use of Fast Fourier Transforms (FFTs) and is done in the frequency-domain. Such operations have certain advantages in terms of processing speed, which is one reason for the existence of frequency-domain-based SAR processing algorithms. The matched filter corresponds to the convolution of the echo with a replica of the original pulse. This focuses the pulse to a much shorter length. Overlapping pulses can now be distinguished by referencing time to frequency within the signal bandwidth B. The range resolution is then defined by Eq. (2.3) [20].

$$r_r = \frac{c_0}{2 \cdot B} \tag{2.3}$$

The range compression finishes the focusing of the Radar data in range direction. As already mentioned, shortening the pulse length is problematic also because of the direct dependency of the azimuth resolution from the range resolution. The azimuth resolution defines the ability to separate two objects in azimuth direction. This resolution is defined by the aperture angle  $\Theta_{az}$  of the antenna. All objects that are illuminated by the antenna beam while having the same distance to the antenna, will backscatter energy at the same time. These echoes are received at the same time by the sensor, wherefore the sensor cannot distinguish between the two objects, although the might lie on the opposite edges of the beam.

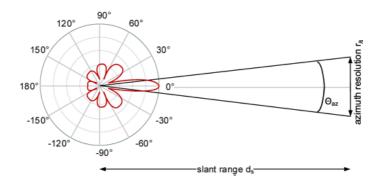

Figure 2.2: Antenna diagram with aperture

Therefore, the beam needs to be as narrow as possible in order to illuminate as few objects in azimuth at the same time. Figure 2.2 shows an antenna diagram with the corresponding aperture angle  $\Theta_{az}$  [20]. The angle is defined by the width of the main lobe of the antenna, whereby the main lobe is defined as the area where loss of echo energy does not drop under 3 dB (50%). Since the aperture angle  $\Theta_{az}$  defines the beamwidth and is a fixed value for a given antenna, the diagram shows that the azimuth resolution  $r_a$  (so also the range resolution) depends on the slant range distance  $d_s$  to the object. The beamwidth  $b_w$  depends on the physical length  $l_a$  of the RAR antenna in azimuth direction and the wavelength  $\lambda$  of the Radar and results to Eq. (2.4) in meter. [20].

$$b_w = \frac{\lambda}{l_a} \tag{2.4}$$

This shows that to narrow the beamwidth, either the wavelength (pulse width) needs to be reduced or the size of the real antenna must be increased. Due to the already discussed limitations, the wavelength can only be shortened to a certain limit. The same applies to the antenna length  $l_a$ . Since the resolution in azimuth results to Eq. (2.5) [20], only the slant range distance can be reduced.

$$r_a = d_s \cdot \tan b_w \cdot 2 \tag{2.5}$$

Also, the slant range can only be reduced in certain limits on airborne and spaceborne platforms and would not be sufficient to reduce azimuth resolution as required.

To solve this problem, the data must be focused in azimuth. This is the second step after range compression and completes the processing of SAR data. As already indicated by the name, a long real aperture is synthesized by stitching several small real apertures together, forming a virtual antenna.

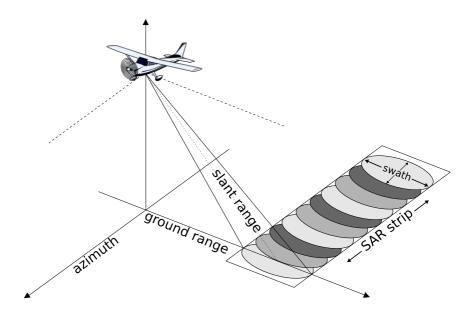

Figure 2.3: Geometry for stripmap SAR on airborne platform

To form the synthetic aperture, the linear movement of the platform along a linear track in azimuth is used. This is called stripmap mode in SAR. In contrast to RAR systems, the antenna of such systems is small. Thereby the aperture and the resulting swath size on the ground is wide. Therefore, an object on the ground will be illuminated by many different pulses which overlap each other. This also means that an object is illuminated from many different angles during the flight (antenna synthesis). The principle is shown in Fig. 2.3.

While in RAR systems, an image is formed rather simple due to the single image line scans, SAR systems rely on a rather complex signal processing to focus the image. This is also called azimuth compression. The different techniques to perform azimuth compression are discussed in the following sections and is the main focus of this work. The basic principle of azimuth compression relies on the fact that every pulse that covered the object, contains a small amount of echo energy from this object. The echo energy is located in the range line  $N_{az}$ , the position within the range line depends on the distance between object and sensor. Due to the wide aperture, this distance information results in a blurred position, represented by a circular arc around the antenna position. Due to the movement of the platform, the distance between sensor and object will change continuously, which shifts the position of the echo energy in every following range line  $N_{az}$ . The multiple samples of blurred information create an overdetermined equation system, allowing to trace back an object location.

The backtracing is done by simple summation of energy. An object at a certain position will create an energy pulse in a specific range position, according to the distance to the antenna. This position will shift in every line due to the movement of the antenna. This energy can be projected as a circular arc around each antenna position. By doing this, all arcs will overlap at the correct position to focus the object. This belongs to the mathematical group of inverse problems since the image is traced back from a set of indirect observations. According to [20] the azimuth resolution for SAR systems results to Eq. (2.6), so to half of the antenna length  $l_a$ .

$$r_{as} = \frac{l_a}{2} \tag{2.6}$$

This shows the superiority of SAR systems. First, to increase the number of samples per object the beam width should be widened, which is contrary to RAR system. Second, the resolution does not depend on slant range  $d_s$  anymore, since the length of the virtual antenna can be used to compensate for the change in slant range. This enables for high ground resolutions which are not possible with RAR systems. The disadvantage of SAR system is the high demand for processing power to perform the signal processing to focus the image. In addition to the stripmap mode, other modes exist where the antenna is always steered to focus on one spot during forward-motion on a straight path (spot mode). Another form is circular SAR, where an area is circled and continuously scanned. Both modes allow for even higher resolutions. The processing is divided into frequency and time-domain-based algorithms, both having pros and cons which are covered in the following sections.

#### 2.2 Azimuth compression in frequency-domain

While range compression is similar for all domains, azimuth compression is divided into frequency and time-domain-based algorithms. The most prominent algorithms in the frequency-domain are the Range Doppler Algorithm (RDA) and the Wavenumber Domain Algorithm (WKA). The undeniable advantage of frequency-domain-based processing is the relatively small complexity when compared to time-domain-based processing. Both the RDA and the WKA reside within the complexity class of  $\mathcal{O}(N^2 log N)$  for images with the size of  $N \times N$  pixels. Where N represents the number of collected echo lines  $N_{az}$ . Data is transformed into the frequency-domain via a FFT for processing. The class of algorithms is named after that. In the frequencydomain, a simplification is possible as the convolution theorem [51] states that a convolution in the time-domain equals a pointwise multiplication in the frequencydomain. This allows substituting all matched filter convolutions in the algorithms with multiplications. While processing speeds up, the simplification does not allow for a direct interpretation of time-dependent parameters. This can create ambiguities and reduced image quality under certain conditions (motion variations from a linear track). Motion compensation algorithms are capable of correcting the deviations to a certain degree.

Nevertheless, the RDA and WKA are still state of the art algorithms and are used in most SAR systems for processing. But one has to bear in mind, that SAR systems usually were mounted to bigger and more stable platforms in the past, wherefore motion was not a severe problem. With the availability of smaller SAR frontends which are capable of high-resolution scans, smaller platforms are also used. Especially small Unmanned Aerial Vehicles (UAVs) are affected by atmospheric turbulences, because of the lightweight system design, comparatively lower speed, and altitude. For this reason, the assumption of an ideal flight path fails in most practical airborne scenarios, which makes the precise correction of motion errors mandatory.

#### 2.3 Azimuth compression in time-domain

Frequency-domain-based compression assumes a rather straight flight path to work properly. While the assumption of an ideal straight flight path (without bigger deviations) can be valid for bigger platforms, such assumptions are usually invalid for smaller lightweight platforms. The big advantage of time-domain-based azimuth compression over frequency-domain-based azimuth compression is the inclusion of all available trajectory information, which allows compensating any deviation during processing. Additionally, the principle provides the best possible image results for SAR data. The Global Backprojection (GBP) is the basic algorithm for time-domainbased azimuth compression and is therefore explained in detail. But it imposes the highest degree of complexity for processing. To reduce complexity, several different methods exist, from which the Fast Factorized Backprojection (FFBP) shows the most potential for complexity reduction, flexibility, and preservation of image quality. Therefore, this method is examined as well. All of these methods were developed under the principle of very short Radar pulses, the FMCW technology with longer frequency pulse ramps might violate this assumption for processing. In order to compensate for longer pulse ramps, the principle of FMCW Radar is explained.

#### 2.3.1 Global backprojection algorithm (GBP)

The backprojection principle is based on the Radon transform [25], which can be used for indirect image formation. It is commonly used in the medical field [30] as data sets and image dimensions are smaller, which allows for decent runtimes despite the high complexity of the mathematical problem. This problem resides in the complexity class of  $\mathcal{O}(N^3)$  [52], where N represents the number of collected echo lines and processed image pixels in x and y dimensions. Therefore, computation time is challenging when high-resolution images are required in real-time due to exponentially growing processing times. Different adaptations reformulated the problem and adapted it to SAR scenarios [33, 34, 35, 36]. The GBP follows the basic physical and geometric principles of SAR which is depicted in Fig. 2.4.

Figure 2.4: SAR geometry with trajectory vector and overlapping image plane [53]

SAR data is acquired by moving a wide aperture sensor on a path in azimuth while looking sidewards during pulse transmission. During acquisition, all objects (which are illuminated by the sensor) induce an echo signal in the raw sensor data S of each pulse. By traveling  $N_{az}$  positions,  $N_{az}$  views (range lines) of an observed object from different angles and distances are collected. System-specific range compression, according to Section 2.1, is used for each of these range lines, to form the equidistant range samples  $N_{rg}$  or range cells. These range samples form a range line that is part of the sensor data set S. The index of every range sample  $i_r$  represents the time when this sample was acquired. The described process is a direct observation result of the ground, viewed from the moving platform.

To form an image with backprojection, this traced back and transferred onto the image plane. This can also be understood as a projection of the energy back on the ground, which explains the name of the algorithm. The time indices  $i_r$  of each range sample in a range line, can be used to allocate the specific range sample in each range line that holds the echo signal of one specific object on the ground. This requires the position of the object on a 2D pixel raster to form an image plane.

The position  $\overrightarrow{xyz}$  is composed with the help of the components calculated according to Eq. (2.7) - Eq. (2.9).

$$x = i_x \cdot \delta x \tag{2.7}$$

Where  $i_x$  is the discrete coordinate of the current pixel in x in the image plane and  $\delta x$  is the increment in distance between two pixel. It is assumed, that the origin of the platform trajectory (which define the antenna positions) and the origin of the image plane are identical.

$$y = i_{v} \cdot \delta y \tag{2.8}$$

Where  $i_y$  is the discrete coordinate of the current pixel in y in the image plane I and  $\delta y$  is the increment in distance between two pixel.

$$z = Z[x, y] \tag{2.9}$$

Where z is the height value in m for every ground coordinate. The value is read from an array that holds a height map of the scanned aerial. The z component is required for correct calculation but not for the 2D image raster. Based on the antenna position  $\overrightarrow{t_{xyz}}$  and the position of the object on the raster  $\overrightarrow{xyz}$ , the distance between the object and the antenna can be calculated following Eq. (2.10).

$$\delta r = |\overrightarrow{t_{xyz}} - \overrightarrow{xyz}| \tag{2.10}$$

Due to the movement of the platform, the distance  $\delta r$  between an object and the antenna changes for every range line  $N_{az}$ . This gives an individual index or time value  $r_{cell}$  for the object in each range line and results to Eq. (2.11)

$$r_{cell} = \frac{\delta r - r_{min}}{\delta rg} \tag{2.11}$$

Where  $\delta rg$  is the distance between each range sample, and  $r_{min}$  is the distance from the antenna to the first range sample. Both factors are defined by the SAR system. As  $r_{cell}$  will not be a discrete value, interpolation is required, to match  $r_{cell}$  with the equidistant pattern of indices  $i_r$  of a range line. Since the complex valued range samples not only carry information about the reflected energy, but also about the phase signal, a phase correction is required as well. The correction requires the angle  $\phi_{corr}$  which results to Eq. (2.12).

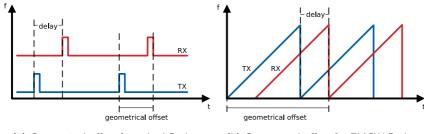

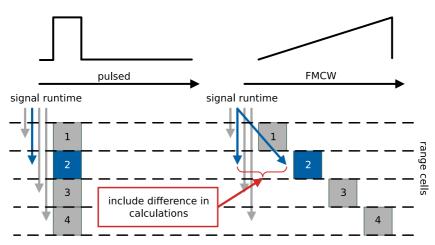

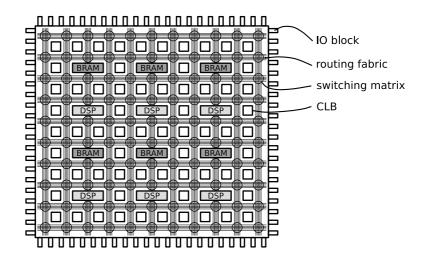

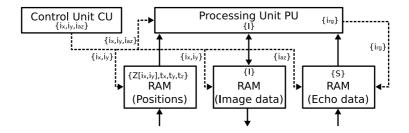

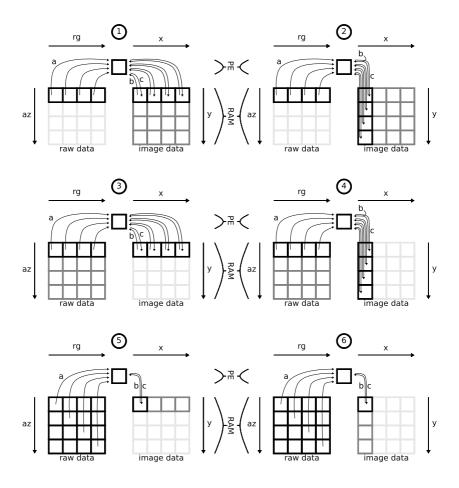

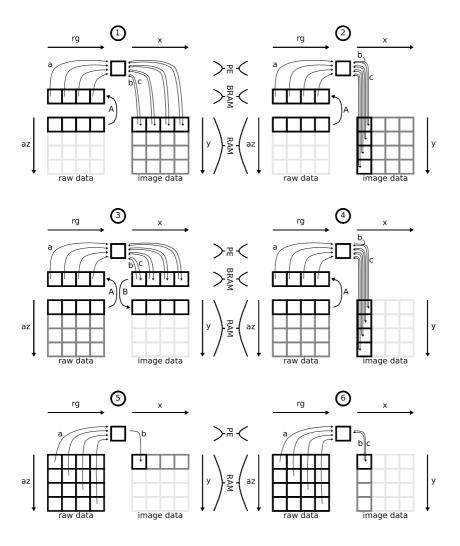

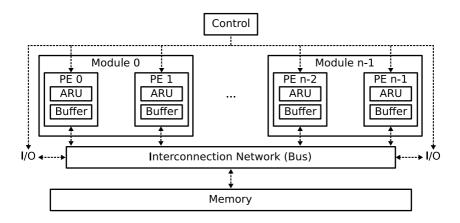

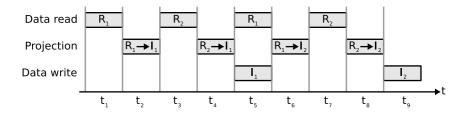

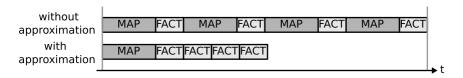

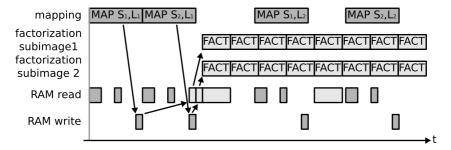

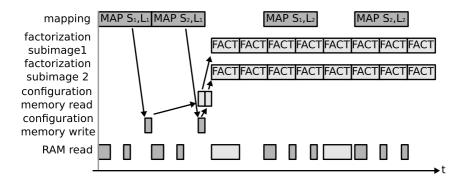

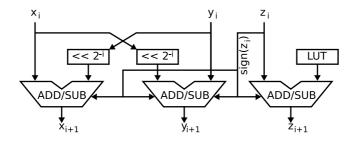

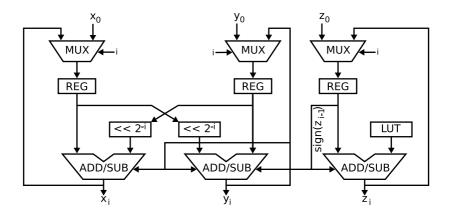

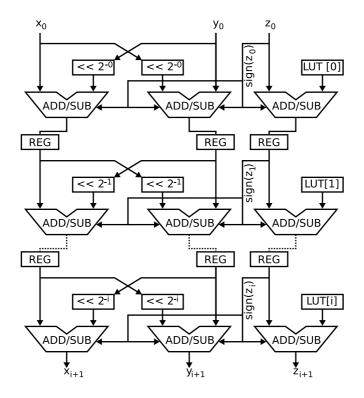

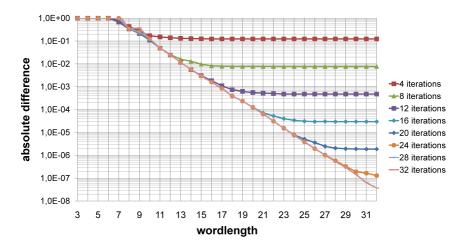

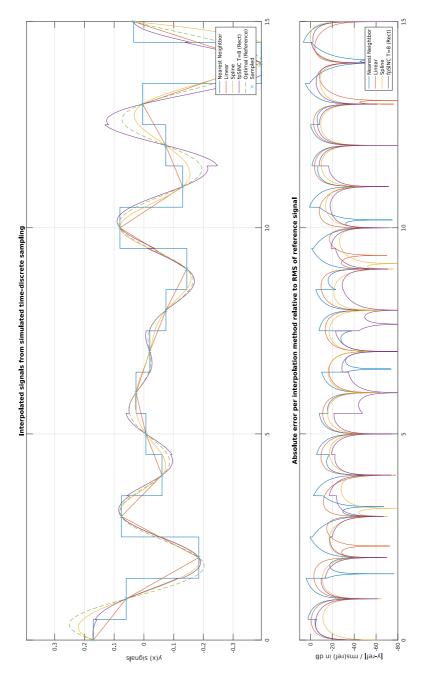

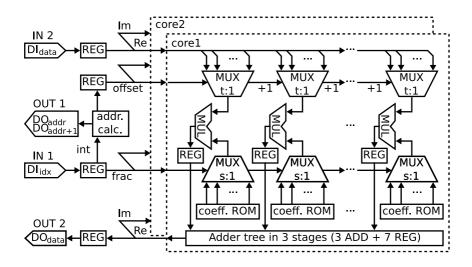

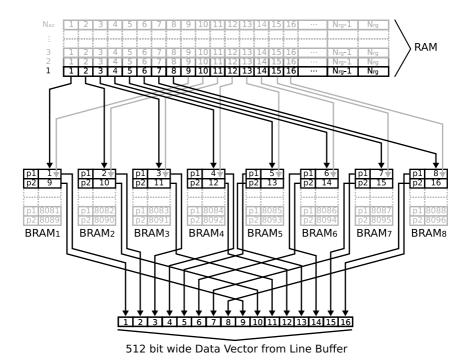

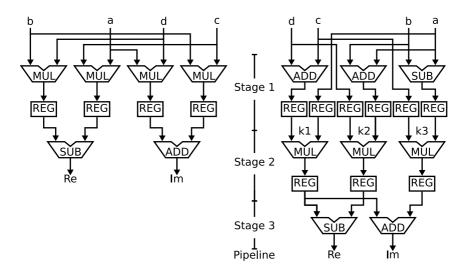

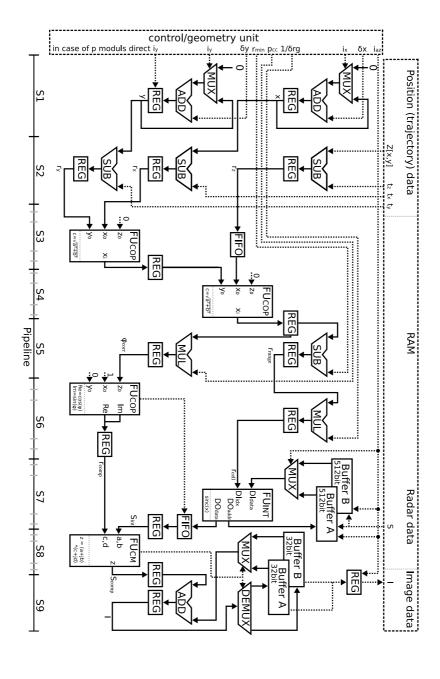

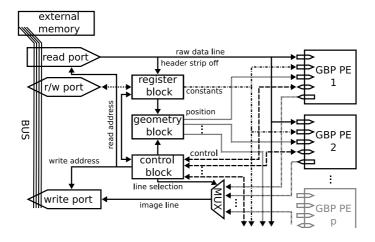

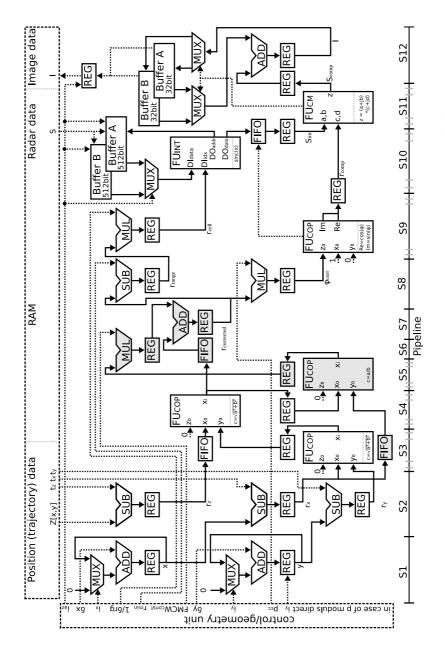

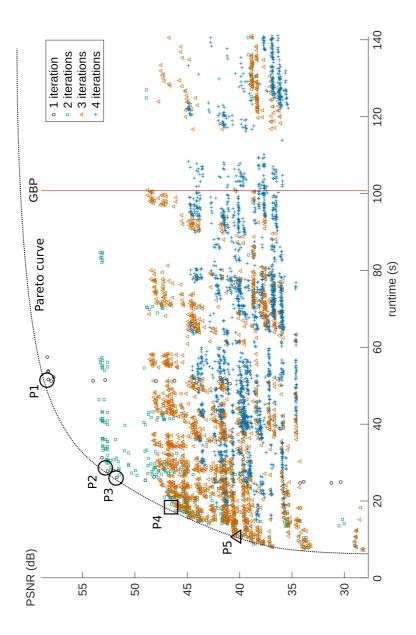

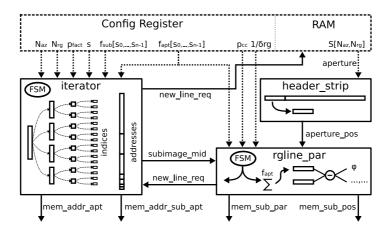

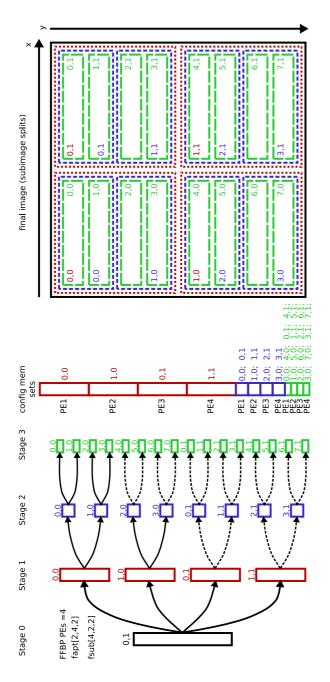

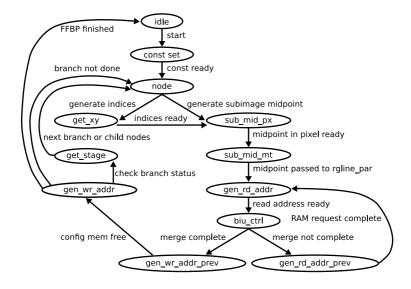

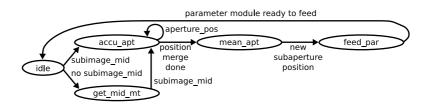

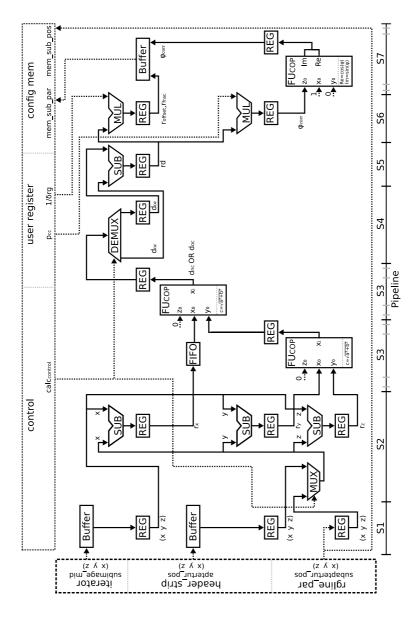

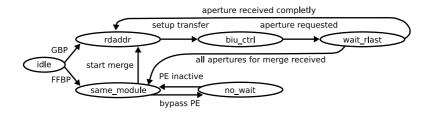

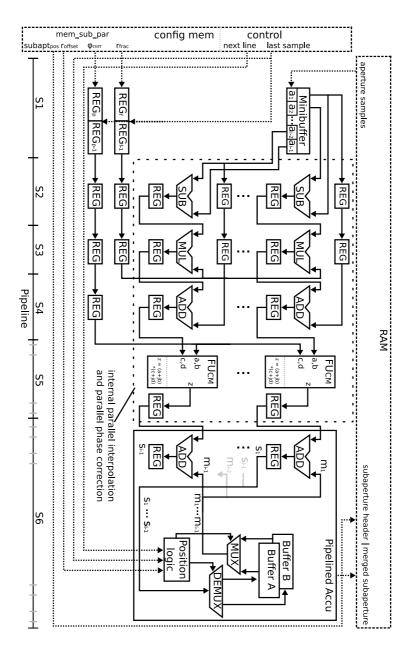

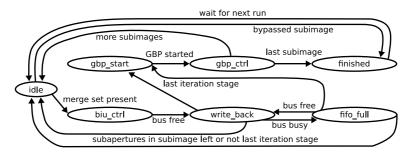

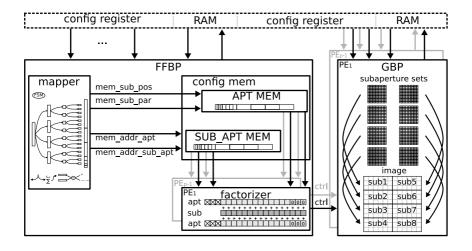

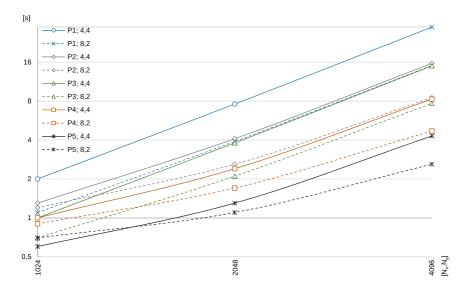

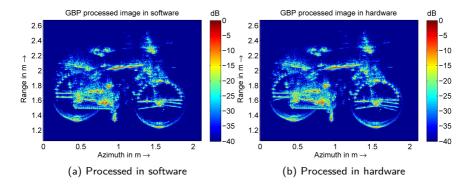

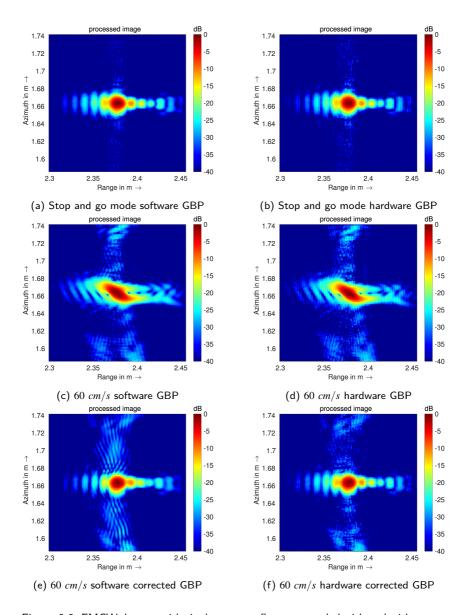

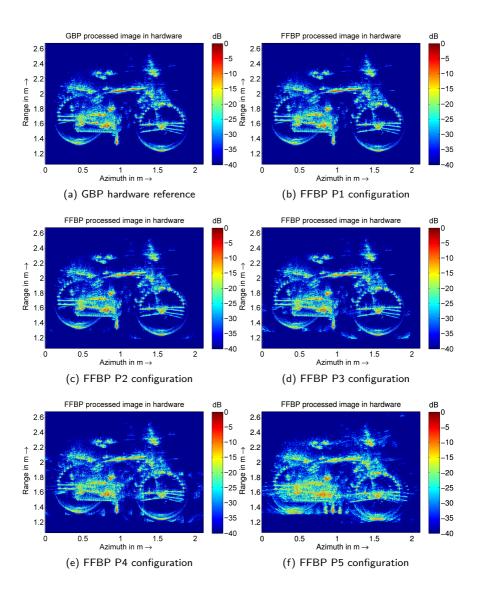

$$\phi_{corr} = \delta r \cdot \frac{4\pi}{\lambda} \tag{2.12}$$