#### Available online at www.sciencedirect.com

# **ScienceDirect**

Procedia Procedia

Energy Procedia 38 (2013) 933 - 941

SiliconPV: March 25-27, 2013, Hamelin, Germany

# Multilayer etching for kerf-free solar cells from macroporous silicon

Sören Schäfer<sup>a,\*</sup>, Marco Ernst<sup>a</sup>, Sarah Kajari-Schröder<sup>a</sup>, and Rolf Brendel<sup>a,b</sup>

<sup>a</sup>Institute for Solar Energy Research Hamelin, D-31860 Emmerthal, Germany <sup>b</sup>Department Solar Energy, Institute of Solid-State Physics, Leibniz Universität Hannover, D-30167 Hannover, Germany

#### Abstract

Kerf-free techniques for subdividing a single thick crystalline Si wafer into a multitude of thin Si layers have a large potential for cost reductions. In this paper, we explore pore formation in Si for separating many 18 µm-thick surface-textured layers from a thick wafer with a single etching process. We demonstrate the fabrication and separation of four macroporous Si layers in a single etching step. Generating many instead of single macroporous layers per etching step improves the economics of the macroporous Si process. We present our etching process that maintains the pore pattern defined by photolithography even after etching many absorber and separation layers.

© 2013 The Authors. Published by Elsevier Ltd. Open access under CC BY-NC-ND license. Selection and/or peer-review under responsibility of the scientific committee of the SiliconPV 2013 conference

Keywords: Kerf-free, layer transfer, macroporous silicon, thin films.

#### 1. Introduction

The wafers account for about 40 % of the cost of a PV module with crystalline Si solar cells [1]. Large cost reductions became possible if a low-cost technique existed, that slices a single wafer of e.g. 600  $\mu$ m into e.g. 30 thin layers with a thickness of 20  $\mu$ m each. This could possibly reduce the cost per wafer area by a huge factor. This slicing technique should, however, avoid the kerf loss of conventional wafer sawing. The cost for the sawing of the original wafer would then be distributed over the 30 slices generated from every wafer.

Various approaches for subdividing a thick wafer into many thin wafers were reported in the literature. Ion implantation was shown to generate  $\mu$ m-thick [2] and tens of  $\mu$ m-thick [3] Si slices. Spalling under mechanical stress was described [4] and demonstrated [5] to generate about 50  $\mu$ m-thin crystalline Si

<sup>\*</sup> Corresponding author. Tel.: +49-5151-999-314; fax: +49-5151-999-400. *E-mail address*: s.schaefer@isfh.de.

layers. An attractive alternative is lateral wet chemical etching [6] that generates layers of arbitrary thickness. In 1992 a patent by Lehmann suggested electrochemical etching of macropores for separating thin monocrystalline Si layers from a wafer [7]. We term such thin layers MacPSi layers since they are from macroporous silicon.

Recently, we demonstrated the fabrication of MacPSi layers on small areas of about 1 cm $^2$  [8] and later on large areas [9]. The MacPSi layers are penetrated by macropores that have a distance of about 8  $\mu$ m and a diameter of about 4  $\mu$ m. This structure reduces the surface reflection and enhances the light trapping which is an advantage over the other techniques that require surface texturing as an additional processing step [10]. Due to this excellent light trapping, solar cells from 35  $\mu$ m-thick MacPSi layers exhibit short-circuit current densities as high as 37.1 mA/cm $^2$  [11].

However, all the demonstrated approaches for separating thin layers, including the MacPSi approach, generate one film at a time. The wafer is treated by implantation, stressing or etching to generate a first film. The first thin layer is separated from the thick wafer and the treatment is repeated to generate the next layer. This is a disadvantage for the economics of the process. In case of wet chemical approaches the wafer has to be immersed into the chemistry and taken out of the chemistry, cleaned and dried for every layer. This also increases the consumption of the chemicals since each layer is likely to carry with it some etching solution from the bath.

In this conference contribution we demonstrate the etching of macropores for generating many thin slices within a single etching process as first described in Ref. [12]. Such multilayer etching aims at improving the economics of the MacPSi process.

### 2. Concept of multilayered etching

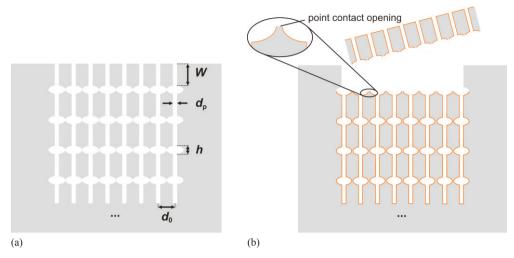

Figure 1a sketches the concept of multilayered electrochemical pore etching: Absorber layers of thickness W alternate with separation layers of thickness h. This is achieved by modifying the etching conditions in such a manner that the diameter of the pores are periodically modulated from small to large values and back to small values. For the absorber layer it is advantageous to have a low porosity which offers a lot of Si material for light absorption. For the thin separation layer it is advantageous to have a high porosity which permits an easy separation of the absorber layers. We either increase the pore diameter to a moderate level that keeps adjacent absorber layers connected by mechanically weak bridges; alternatively we greatly enhance the diameter of the pores in the separation layer to fully detach adjacent layers. Various scenarios are possible for separating the absorber layers:

Scenario 1: We first etch N absorber layers that are still interconnected by N-I separation layers. The pores of the N<sup>th</sup> separation layer are made sufficiently wide to separate the stack from the wafer. Depending on the details of the etching process, the detached multilayer stack may still be connected to the wafer at the rim of the stack. In this case, this connection may be removed by trenching with a laser. The stack of N absorber layers is then removed from the wafer and separated into individual layers in subsequent processes. For this subsequent separation one could either apply mechanical stress for breaking the weak interconnections; alternatively isotropic etching of Si could remove the interconnections.

Scenario 2: It is also possible to etch separation layers that fully separate all absorber layers from each other. The layers remain connected to the wafer at the rim. Sequential laser trenching and layer removal is then applied to take off one layer after the other. The full separation of all absorber layers while the stack is still connected to the rim can be achieved by electrochemical etching only or by a combination of electrochemical and isotropic chemical etching.

Fig. 1. (a) Schematics of the pore profile for generating a multitude of thin Si layers in a single processing step. Macroporous absorber layers with thickness W and single macropore diameter  $d_p$  alternate with separation layers of thickness h. The latter have a high porosity. The distance between the pores is  $d_0$ . (b) The inner pore walls are passivated, e.g. via an oxidation, as is indicated by the orange layer. Small point contact openings are formed at spots where the layers are connected to each other.

In this paper we follow Scenario 1. When etching the first absorber layer the pores nucleate at random positions or at regular periodic positions. The latter requires structuring of the Si surface prior to pore etching. The multilayer etching concept [12] implies that structuring the surface once is sufficient for generating all absorber layers. The costs for structuring the surface is thus reduced by the number of layers generated.

An attractive option of the multilayered approach is sketched in Fig. 1b. When choosing Scenario 1 one could envisage to first diffuse and/or surface passivate the full stack prior to separating the multilayer stack by applying mechanical stress. To be specific we consider an oxidation of the sample. The oxide layer is depicted in orange in Fig. 1b. Separating the oxidized absorber layers by mechanical stress generates small point contact openings on both sides of all inner macroporous absorber layers. Local contacts are advantageous for reducing recombination at the contacts. In a recent publication we demonstrated the fabrication of single macroporous Si layers with such local point contact openings in the passivating oxide layer [13]. This approach has a high-throughput of the passivation process since the cell area processed per wafer is a multiple of the wafer area.

#### 3. Experimental

# 3.1. Surface patterning for homogeneous nucleation

We start with an (100)-oriented, n-type, shiny-etched, Cz-Si wafer that has a resistivity of  $(1.5 \pm 0.2) \Omega cm$  and a thickness of  $(305 \pm 20) \mu m$ . The front side of the wafer receives a 110 nm-thick thermally grown silicon dioxide layer which serves as a diffusion barrier. The subsequent phosphorous diffusion with a sheet resistance of 10  $\Omega$ /sq of the rear side provides an ohmic contact and lateral conductivity for the electrochemical etching process. The silicon dioxide as well as the phosphorous silicate glass is etched off after the diffusion in 40 wt% hydrofluoric acid.

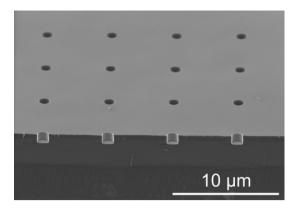

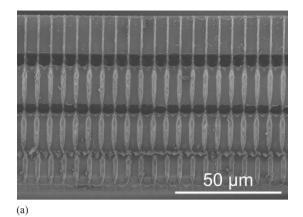

Fig. 2. Cross-sectional SEM micrograph of the patterned front surface.

The front side of the wafer is structured with inverted cylinders that are confined to several discrete areas of  $(0.5 \times 0.5)$  cm<sup>2</sup> on the front side. Figure 2 shows a scanning electron microscope (SEM, S-4800 from Hitachi) micrograph of the front surface before macropore formation. The desired pattern comes with a photolithography step, at the end of which the front side is covered with a photoresist which has about 600 nm-wide, roundly-shaped openings in a square arrangement. The distance between these openings is  $d_0 = 6 \mu m$ . A reactive ion etching step produces cylindrical holes that are  $(975 \pm 30)$  nm in diameter and  $(850 \pm 30)$  nm in depth.

### 3.2. Etching macropores

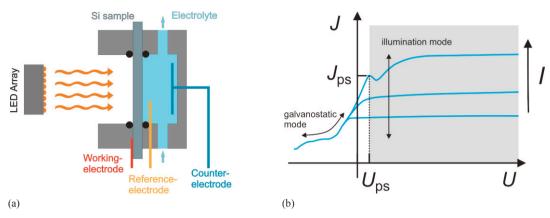

Figure 3a shows the schematics of the etching cell. The etched area is 1 cm<sup>2</sup> and circular in shape. We etch under rear side illumination [14] from an 880 nm light emitting diode (LED) array in 3 wt% hydrofluoric acid at 20 °C. Adding 5 vol% acetic acid improves surface wetting.

Pore etching requires negatively charged fluorine ions and positively charged holes at the Si/electrolyte interface. Illumination from the rear side of the wafer generates the holes. The fluorine ions are supplied via the etching solution.

Applying a positive voltage to the working electrode relative to the platinum counter electrode generates an anodic bias voltage U that we measure between the working electrode and the reference electrode. The latter is positioned in the electrolyte and near the wafer's surface. Thus, the bias voltage U is not influenced by the voltage drop in the electrolyte. Details of the chemical dissolution reactions can be found in Ref. [15].

Three parameters control the etching process. Two of them are independently chosen while the third one is then defined by the current-voltage curve of the etching cell. The three parameters are (i) the etching current density J which controls the dissolution of silicon, (ii) the anodic bias voltage U that controls the band bending in the Si, and (iii) the illumination intensity I that controls the photogeneration rate of holes and electrons. According to Lehmann's model [14], the porosity of a MacPSi layer equals the ratio  $J/J_{PS}$ , where  $J_{PS}$  is the critical current density at the onset of electropolishing. Thus, we tune the diameter of the pores by varying the etching current density J.

The pore tips collect most of the holes that diffuse from the rear side, where they are generated, towards the front side with the pores. This effect promotes silicon dissolution at the pore tip rather than at the pore walls. Figure 3b depicts the typical current-voltage characteristics of the Si/electrolyte that has some similarities to the characteristics of a Schottky contact.

Fig. 3. (a) Schematics of the etching cell. Macropores form at the Si/electrolyte interface on an area of 1 cm<sup>2</sup>. (b) Current-voltage characteristics of the Si/electrolyte interface for three different illumination intensities *I*. The current density  $J_{PS}$  marks the onset of electropolishing that occurs at an anodic bias  $U \ge U_{PS}$ .

# 3.3. Etching conditions

Transferring the pattern of the cylinders in the surface into all of the layers is a major challenge for the multilayer concept. The pores often tend to branch into two or more smaller pores and sometimes stop growing. Appropriate etching conditions are required for the absorber layers and for the separation layers to avoid this.

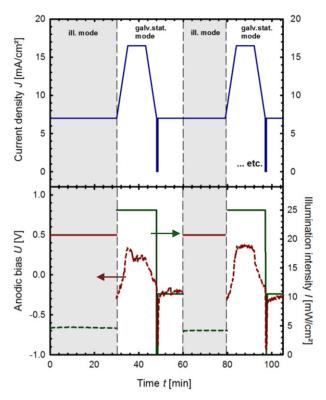

We solved this issue by using an etching current density profile in time as depicted in Fig. 4. Stable pore growth (no branching or dying of pores) is achieved in the so called illumination mode that we apply when etching the absorber layers. The so-called galvanostatic mode is used for maintaining the predefined arrangement of the pores when etching the separation layer.

First we describe the etching current density J (solid blue line) in Fig. 4. We use the etching current density J to tune the diameter of the pores. For the absorber layers we apply a constant etching current density of 7 mA/cm<sup>2</sup> for 30 minutes. For the separation layers, the current density is linearly increased to  $16.5 \text{ mA/cm}^2$  within 5 minutes. After 8 minutes, the current density decreases linearly to  $7 \text{ mA/cm}^2$  in five minutes. This current density profile repeats several times.

Now we address the bias voltage U and the illumination intensity I. One of the two parameters is set by the operator while the other parameter is then defined by the physics of the etching cell. Depending on what parameter is defined by the physics of the cell (and thus not set a priori), we distinguish two different etching modes: The illumination mode and the galvanostatic mode.

Illumination mode: Pore etching starts in the so-called illumination mode. Here the illumination intensity I (dashed green line in Fig. 4) varies as required and the bias voltage U (solid red line) is fixed to 0.5 V. At this voltage, the etching current density J does not change significantly with U as is illustrated in the grey shaded area of Fig. 3b. The anodic bias of U = 0.5 V is above the voltage  $U_{PS}$  ( $U_{PS}$  is typically < 0.2 V) and below the breakdown voltage  $U_{BD}$  ( $U_{BD}$  is typically > 2 V).

Figure 3b qualitatively illustrates the etching current density J for various illumination intensities I. For a fixed bias  $U \ge U_{\rm PS}$  the etching current density J depends on the illumination intensity. Stable macropore growth is observed in this mode [16], [17]. However, when inserting separation layers, the illumination mode leads to inhomogeneous macropore growth, e.g. splitting or branching into smaller pores.

Galvanostatic mode: The separation layers are therefore etched in the galvanostatic mode. Here, we set the illumination intensity to  $I = (25 \pm 1) \text{ mW/cm}^2$  which allows for an etching current density of

Fig. 4. Electrical etching parameters over time for etching a stack of two absorber and separation layers. The solid lines indicate parameters which are set. The current density (blue) is predefined for the whole etching process as it is used to tune the porosity of the layers. The anodic bias (red) or the illumination intensity (green) are set (solid lines) or variable (dashed lines), depending on the etching mode used. The etching modes are explained in the text.

16.5 mA/cm<sup>2</sup>. The preset etching current density J is then reached by adjusting the anodic bias U. In Fig. 3b this etching mode is illustrated by "moving along" one specific curve for voltages  $U \le U_{PS}$ . The etching of the separation layer consumes a lot of HF and thus reduces the concentration of fluorine ions in the separation layer. We therefore pause the etching process for 30 seconds (no current flow) to give the fluorine ions time to diffuse to the Si/electrolyte interface.

It turned out to be detrimental to switch to the illumination mode immediately after finishing the separation layer. We therefore maintain the galvanostatic mode for a few minutes. For that period we apply an illumination intensity of  $(10 \pm 0.5)$  mW/cm<sup>2</sup>. The galvanostatic mode in combination with a fixed and enhanced illumination causes a rather divalent dissolution reaction at the pore tip. This is known to result in more tapered pores [16]. Tapered pores increase the electric field density at the pore tips compared to the flattened pores from the illumination mode and, thus, prevent branching of the pores when etching the following absorber layer.

#### 4. Results and discussion

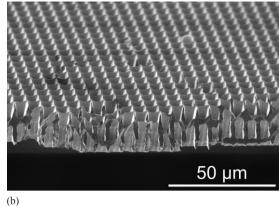

Figure 5a depicts a cross-sectional SEM micrograph of a detached free standing stack that consist of 4 macroporous layers, which we etched with the profile presented in section 3.3. The three upper MacPSi

Fig. 5. (a) SEM micrograph of a detached free standing stack of 4 MacPSi layers that is etched in a single process. The etch direction is from the top towards the bottom of the micrograph. The top MacPSi layer, which is etched first, has a higher porosity in relation to the other three layers. The fourth layer, which is etched at the end, has a reduced thickness compared to the first three layers. The porosity of the separation layers increases in the etching direction. (b) SEM micrograph of a free standing MacPSi layer which is deprived of the mesoporous silicon film.

absorber layers have a thickness of  $W = (18 \pm 1) \, \mu m$ . The fourth and last-etched layer has a thickness of about 14  $\mu m$ . An explanation for this is the decrease of the etch rate that is limited by the fluorine ion concentration at the pore tips. Since fluorine ions are transported through the pores, the concentration at the pore tip reduces the more the deeper the pores are. As a compensation for this the etching pause needs to be longer, so that ions can diffuse to the pore tip. Alternatively the etch time could be increased.

Another interesting consequence of the depletion of fluorine ions is an increasing porosity of the separation layers. As can be seen in Fig. 5a, the first two MacPSi layers are still connected via small bridges of silicon while the third and fourth layer are already separated and lie directly on top of each other. As mentioned above, the porosity is connected to the critical current density  $J_{PS}$ .  $J_{PS}$  on the other hand is proportional to the concentration of hydrofluoric acid [15]. The easiest way to overcome this is to gradually reduce the current density J from one separation to the next separation layer.

The porosity of the layers is  $(d_p/d_0)^2$ , since the pores are almost square in diameter and are positioned at the corners of squares. The three bottom layers have a porosity of  $(32 \pm 4)$  %. The top and first-etched MacPSi layer has, however, a higher porosity of  $(69 \pm 5.5)$  %. The reason for this deviation is not clear yet.

A few nm-thick film of mesoporous silicon, which is produced during the dissolution reaction, covers the MacPSi layers in Fig. 5a. Figure 5b shows a SEM micrograph of a single free standing MacPSi layer with a thickness of  $W = (17.5 \pm 0.5) \, \mu \text{m}$ . This is deprived of the mesoporous film by etching in 1 mol/l potassium hydroxide solution for a few seconds at room temperature.

The thickness of the separation layers is  $h = (5 \pm 1) \, \mu \text{m}$ . This is about 5 % of a 100  $\mu \text{m}$  kerf-loss by sawing a Si wafer. A fraction of this loss is used to generate a texture that is beneficial for the optical performance of the film [10].

The MacPSi layer stack can be detached from the substrate with low forces. In most cases the pressure of a water jet or a dip for a few seconds into potassium hydroxide solution suffices for the layers to detach from the substrate.

Fig. 6. Photos of the separation of a stack of two interconnected MacPSi layers. a) We attach stripes of adhesive tape onto both sides of the stack and then b), c) pull them apart. The layers remain attached to both tapes. The size of the layers is  $(0.5 \times 0.5)$  cm<sup>2</sup>.

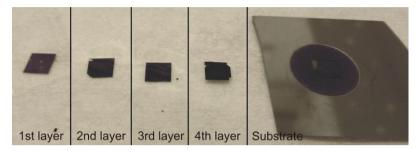

Fig. 7. Photos of 4 MacPSi layers that were etched in a single process and detached from the substrate. The area of the detached layers is  $(0.5 \times 0.5)$  cm<sup>2</sup>. All photos have the same scale. The first three layers were separated from each other with the approach illustrated in Fig. 6.

As shown in Fig. 5a, the first and second MacPSi layers (see Fig. 5a) are still connected by weak bridges. Hence, these both layers must be subdivided into separate layers after the detachment from the substrate.

The photos in Fig. 6 illustrate a method to do this. We apply stripes of adhesive tape to either side of the interconnected layers. The layers are separate when pulling the stripes apart. With this technique it is possible to detach and split all MacPSi layers.

Figure 7 depicts all the 4 small MacPSi films with a size of  $(0.5 \times 0.5)$  cm<sup>2</sup> after detachment plus the substrate wafer. In this particular case, the first three layers stuck together.

### 5. Conclusion

In this paper we demonstrated the separation of four less than 18 µm-thick macroporous Si absorber layers from a 305 µm-thick wafer with a single electrochemical etching step. This was achieved by alternating the etching mode between the illumination mode and galvanostatic mode. This etching procedure creates a layered stack of macroporous Si absorber layers and intermittent separation layers. The separation of the stacked absorber layers was realized by repeatedly applying tapes to both sides of the stack. A key advantage of this process is that the substrate wafer has to pass the etching process only once. Furthermore, the process allows for partly processing, e. g. passivating or diffusing the full layer stack before detachment. Thus, many absorber layers are processed per wafer which results in large throughput for passivation or diffusion.

Despite the fact that subsequent absorber layers are not yet exactly identical in morphology, we consider these first results on the multilayer etching approach to be quite promising. In particular, the pore distribution is maintained through all the 4 MacPSi layers.

However, we so far only demonstrated this process on a small area of  $(0.5 \times 0.5)$  cm<sup>2</sup>. Future work will be devoted to enhancing the etched area to industry typical solar cell sizes. Further work is also required to demonstrate the formation of more than four layers. This is not an easy task, since the transport of fluorine ions may impose physical limitations. Understanding the physics of the etching processes at large pore depths is therefore important.

# Acknowledgements

The authors thank Florian Schlachter from AMO GmbH in Aachen for processing the cylindrical holes into the wafer and Bianca Gehring (ISFH) for her valuable help with the macropore etching. This work was supported by the Federal Ministry for Environment, Nature Conservation, and Nuclear Safety under the contract FKZ 0325147.

### References

- [1] ITRPV 2012, International Technology Roadmap for Photovoltaics Results 2012, Third Edition, Berlin 2012, www.ITRPV.net, with own estimates for the cost of the poly Si.

- [2] Bruel M. Silicon on insulator material technology. Electron. Lett. 1995;31(14):1201.

- [3] Henley F, Lamm A, Kang S, Liu Z, Tian L. Direct film transfer (DFT) technology for kerf-free silicon wafering. In: Proceedings of the 23rd EU PVSEC. Valencia, Spain: WIP München; 2008, p. 1090–1093.

- [4] Suo Z, Hutchinson JW. Steady-state cracking in brittle substrates beneath adherent films. *International Journal of Solids and Structures* 1989;**25**(11):1337–53.

- [5] Dross F, Robbelein J, Vandevelde B, van Kerschaver E, Gordon I, Beaucarne G, et al.. Stress-induced large-area lift-off of crystalline Si films. *Appl. Phys. A* 2007;**89**(1):149–52.

- [6] Weber KJ, Blakers AW, Stocks MJ, Verlinden PJ. Thin silicon cells using novel LASE process. In: *Proc. of 3rd World Conference on Photovoltaic Energy Conversion*; 2003, p. 1262–1264.

- [7] Lehmann V, Hönlein W, Stengl R, Willer J, Wendt H. Verfahren zur Herstellung einer Solarzelle aus einer Substratscheibe, German patent DE4204455C1; Filing date: 29.01.1992.

- [8] Brendel R, Ernst M, Macroporous Si as an absorber for thin-film solar cells, Phys, Status Solidi RRL 2010;4(1-2):40-2.

- [9] Ernst M, Brendel R. Large area macroporous silicon layers for monocrystalline thin-film solar cells. In: 35th IEEE Photovoltaic Specialists Conference (PVSC): IEEE; 2010, p. 3122–3124.

- [10] Ernst M, Brendel R, Ferré R, Harder N, Kajari-Schröder S. Macroporous silicon as an absorber for thin heterojunction solar cells. In: 38th IEEE Photovoltaic Specialists Conference (PVSC): IEEE; 2012, p. 1040–1045.

- [11] Ernst M, Brendel R. Macroporous Silicon Solar Cells With an Epitaxial Emitter. IEEE J. Photovoltaics 2013;3(2):723–9.

- [12] Brendel R, Ernst M, Plagwitz H., Verfahren zum Bilden von dünnen Halbleiterschichtsubstraten sowie Verfahren zum Herstellen eines Halbleiterbaulements, insbesondere einer Solarzelle, mit einem solchen Halbleiterschichtsubstrat, German patent application DE102009024613; Filing date: 12.06.2009.

- [13] Ernst M, Zywietz U, Brendel R. Point contact openings in surface passivated macroporous silicon layers. *Solar Energy Materials and Solar Cells* 2012;**105**:113–8.

- [14] Lehmann V, Föll H. Formation Mechanism and Properties of Electrochemically Etched Trenches in n-Type Silicon. *J. Electrochem. Soc* 1990;**137**(2):653–9.

- [15] Lehmann V. Electrochemistry of Silicon, Instrumentation, Science, Materials and Applications. Weinheim: Wiley-VCH; 2002.

- [16] Lehmann V. The Physics of Macropore Formation in Low Doped n-Type Silicon. J. Electrochem. Soc 1993;140:2836-43.

- [17] Matthias S, Müller F, Schilling J, Gösele U. Pushing the limits of macroporous silicon etching. *Appl. Phys. A* 2005;80:1391–6.